質量保障措施

工藝保障

1)原材料控制。包括對掩膜版、

化學試劑、光刻膠、特別對矽材料等原材料的控制。控制不光採用傳統的單一檢驗方式,還可對關鍵原材料採用統計過程控制(statisticalprocesscontrol,SPC)技術,確保原材料的質量水平高,質量一致性好。

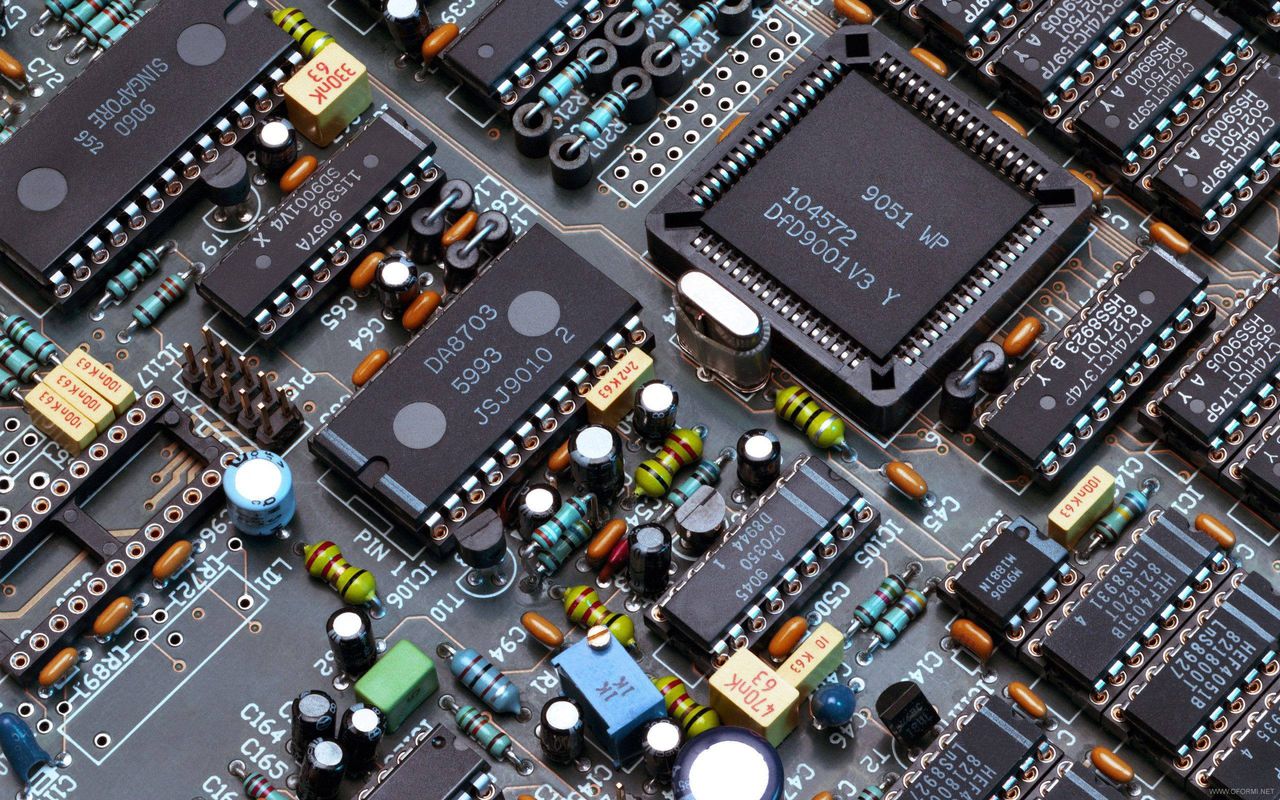

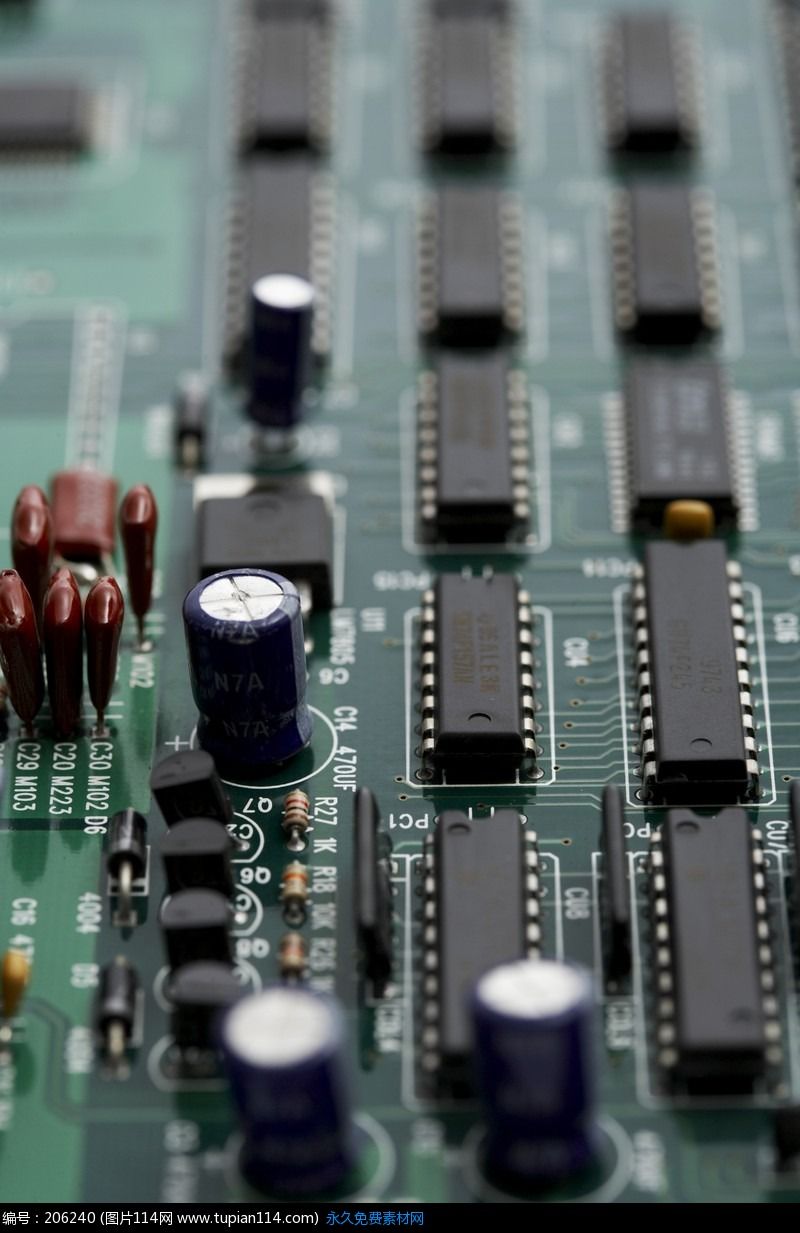

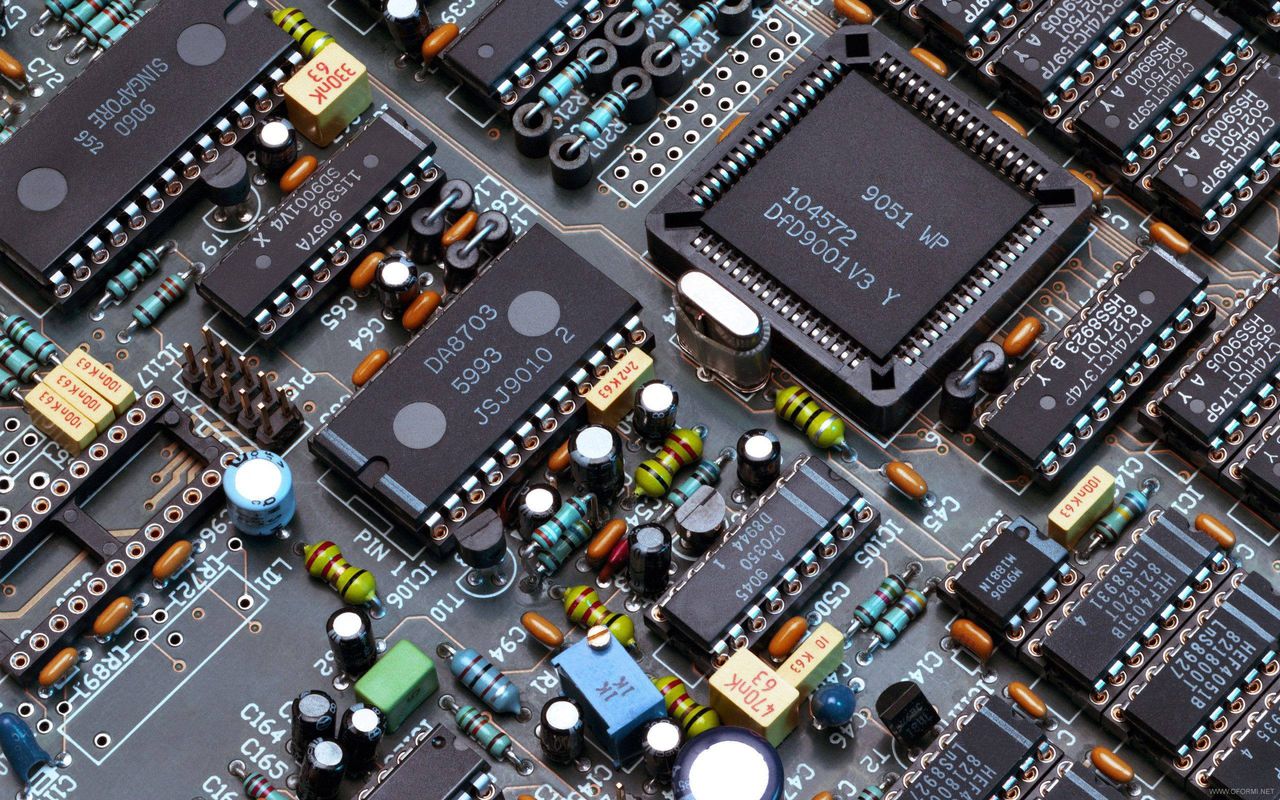

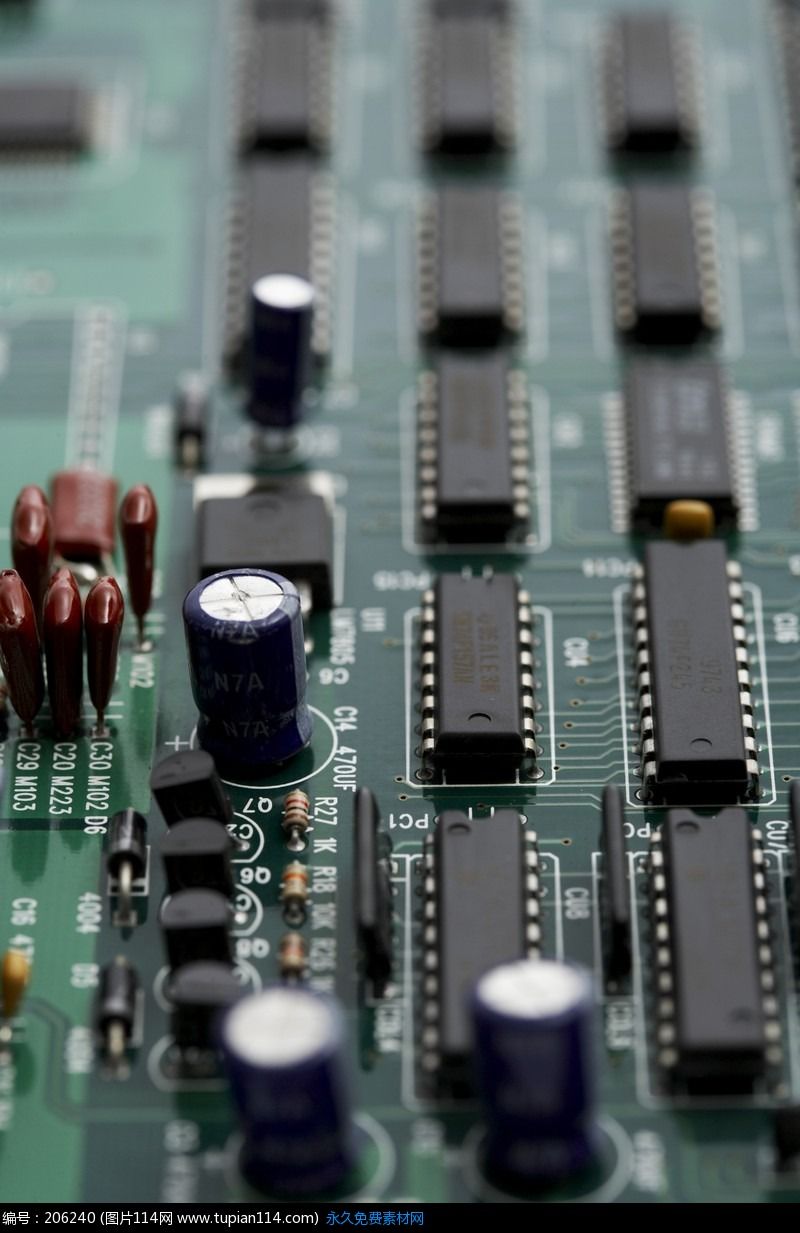

半導體積體電路

2)加工設備的控制。除採用先進的設備進行工藝加工外,還應做好對設備日常維護、

預防性維修等工作,同時應對設備的關鍵參數進行監控,必要時建立設備參數的SPC控制模型進行分析控制等。

3)工藝加工過程的控制。包括對關鍵工藝參數進行SPC控制、工序能力分析、6σ設計等,同時對工藝加工關鍵環節建立工藝檢驗手段,如對氧化層的針孔和裂紋的檢驗、對可動金屬離子的檢驗、對金屬層穩定性的檢驗等。此外,工藝方面的保障還應包括對操作人員的培訓和考核、對環境潔淨度的控制和建立先進的生產

質量管理信息系統等方面。

設計保障

1) 常規可靠性設計技術。包括冗餘設計、降額設計、靈敏度分析、中心值最佳化設計等。

2) 針對主要失效模式的器件設計技術。包括針對熱載流子效應、閂鎖效應等主要失效模式,合理設計器件結構、幾何尺寸參數和物理參數。

3) 針對主要失效模式的工藝設計保障。包括採用新的工藝技術,調整工藝參數,以提高半導體積體電路晶片的可靠性。

4) 半導體積體電路晶片可靠性計算機模擬技術。在電路設計的同時,以電路結構、版圖布局布線以及可靠性特徵參數為輸入,對電路的可靠性進行計算機模擬分析。根據分析結果,可預計電路的可靠性水平,確定可靠性設計中應採用的設計規則,發現電路和版圖設計方案中的可靠性薄弱環節。

製造工藝

積體電路在大約5mm×5mm大小的矽片上,已集成了一台

微型計算機的核心部分,包含有一萬多個元件。積體電路典型製造過程見圖1。從圖1,可以看到,已在矽片上同時製造完成了一個N+PN電晶體,一個由 P型擴散區構成的電阻和一個由N+P結電容構成的

電容器,並用金屬鋁條將它們連在一起。實際上,在一個常用的直徑為75mm的矽片上(已發展到φ=125mm~150 mm)將有 3000000個這樣的元件,組成幾百個電路、子系統或系統。通過氧化、光刻、擴散或離子注入、化學氣相澱積蒸發或濺射等一系列工藝,一層一層地將整個電路的全部元件、它們的隔離以及金屬互連圖形同時製造在一個單晶片上,形成一個三維網路。而一次又可以同時加工幾十片甚至上百片這樣的矽片,所以一批可以得到成千上萬個這樣的電路。這樣高的效率,正是積體電路能迅速發展的技術和經濟原因。

這個三維網路可以有各種不同的電路功能和系統功能,視各層的拓撲圖形和工藝規範而定。在一定的工藝規範條件下,主要由各層拓撲圖形控制,而各層的拓撲圖形又由各次光刻掩膜版所決定。所以光刻掩膜版的設計是製造積體電路的一個關鍵。它從系統或電路的功能要求出發,按實際可能的工藝參數進行設計,並由計算機輔助來完成設計和掩膜版的製造。

在

晶片製造完成後,經過檢測,然後將矽片上的晶片一個個劃下來,將性能滿足要求的晶片封裝在管殼上,即構成完整的積體電路。

分類

積體電路如果以構成它的電路基礎的電晶體來區分,有

雙極型積體電路和

MOS積體電路兩類。前者以雙極結型

平面電晶體為主要器件(如圖2),後者以MOS場效應電晶體為基礎。圖3表示了典型的矽柵N溝道MOS積體電路的製造工藝過程。一般說來,雙極型積體電路優點是速度比較快,缺點是集成度較低,功耗較大;而MOS積體電路則由於MOS器件的自身隔離,工藝較簡單,集成度較高,功耗較低,缺點是速度較慢。近來在發揮各自優勢,克服自身缺點的發展中,已出現了各種新的器件和電路結構。

半導體積體電路

積體電路按電路功能分,可以有以門電路為基礎的數學邏輯電路和以放大器為基礎的線性電路。後者由於半導體襯底和工作元件之間存在著有害的相互作用,發展較前者慢。同時套用於微波的

微波積體電路和從Ⅲ-Ⅴ族

化合物半導體雷射器和光纖維導管為基礎的光積體電路也正在發展之中。

半導體積體電路除以矽為基礎的材料外,砷化鎵也是重要的材料,以它為基礎材料製成的積體電路,其工作速度可比矽積體電路高一個數量級,有著廣闊的發展前景。

從整個積體電路範疇講,除半導體積體電路外,還有厚膜電路與

薄膜電路。

①厚膜電路。以陶瓷為基片,用絲網印刷和燒結等工藝手段製備無源元件和互連導線,然後與電晶體、二極體和

積體電路晶片以及分立電容等元件混合組裝而成。

②薄膜電路。有全膜和混合之分。所謂全膜電路,就是指構成一個完整電路所需的全部有源元件、無源元件和互連導體,皆用薄膜工藝在絕緣基片上製成。但由於膜式電晶體的性能差、壽命短,因此難以實際套用。所以所說的薄膜電路主要是指薄膜混合電路。它通過真空蒸發和濺射等薄膜工藝和光刻技術,用金屬、合金和氧化物等材料在

微晶玻璃或

陶瓷基片上製造電阻、電容和互連(薄膜厚度一般不超過1微米),然後與一片或多片電晶體器件和積體電路的晶片高密度混合組裝而成。

厚膜和薄膜電路與

單片積體電路相比,各有特點,互為補充。厚膜電路主要套用於大功率領域;而薄膜電路則主要在高頻率、高精度方面發展其套用領域。單片積體電路技術和

混合積體電路技術的相互滲透和結合,發展特大規模和全功能積體電路系統,已成為積體電路發展的一個重要方向。

發展趨勢

就lC產業技術發展的實際情況來看,lC集成度增長速度的降低,並不會導致微電子行業的停滯不前,IC產業可以在產品的多樣性方面以及產品性能方面實現現代化發展。隨著IC產業的不斷發展,IC產品能夠更加滿足市場的實際需求,IC產業設計人員可以結合行業客戶的實際需求來對IC產品進行設計和製造,進而推出多樣性的IC產品,並確保其功能得到一定程度的最佳化。與此同時;IC產業發展過程中可以致力於降低現有工藝設備的製造成本,從而促進IC產業的平衡穩定發展。從另一角度來看,IC集成度增長速度的降低,促使計算機系統和軟體開發人員有更多的時問和精力去研究IC產品,完善IC產品性能。

當前我國大陸地區的IC產業規模相對較小,僅占全球IC產業的一小部分,總的來看,中國的

積體電路產業在經濟和技術方面都要相對落後於國際先進水平。近年來國務院發布了關於IC產業發展的相關檔案,一定程度上刺激了國內lC產業投資,從而促進了中國IC產業增長率的提升。