基本介紹

- 中文名:逐位進位

- 外文名:cascaded carry

- 別名:串聯進位

- 相關概念:邏輯電路、加法器、二進制等

基本介紹

相關分析

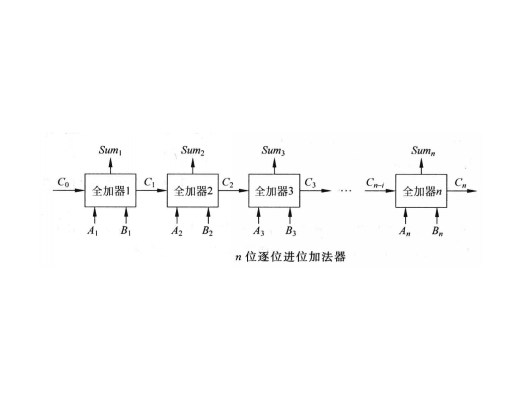

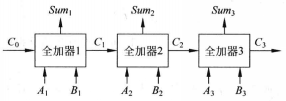

逐位進位是一種實現多位數相加的具體電路的方法。逐位進位的加法器,邏輯電路比較簡單,缺點是運算速度比較慢,因為最高位的加法運算,一定要等到所有低位的加法完成之後才能進行。為了加快運算速度,必須在最短的時間內使各位都形成穩定...

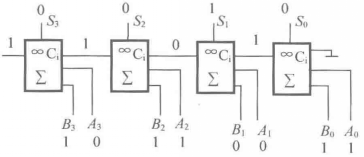

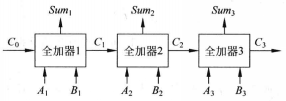

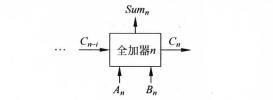

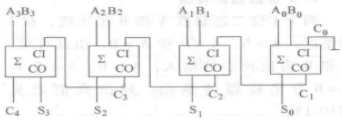

逐位進位加法器是一種進位加法器方式。一個N位加法器可以通過把N個一位的全加器(FA)電路串聯起來構成,即對於從k=1至N-1把Co,k-1連線到Ci,k,並使第一個輸入進位Ci,0連線至0。要實現二進制加法,一種自然的想法就是將1位的二進制加法重複32次(即逐位進位加法器)。這樣做無疑是可行且易行的,但...

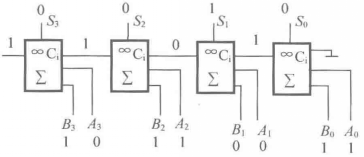

進位選擇加法器(Carry-Select Adder)是加法器中的一種。在逐位進位加法器(Carry-Ripple Adder)中,除最低位外,每一位都需要等待前一位輸出的進位信號。那么不妨預先考慮進位輸入的所有可能,對於二進制加法來說,就是0與1兩種可能,並提前計算出若干位針對這兩種可能性的結果。等到前一位的進位來到時,可以...

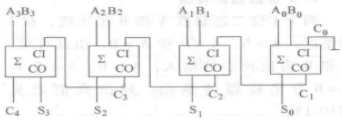

四位全加器,是指能實現四位二進制數全加的數字電路模組。簡介 多位全加器連線可以是逐位進位,也可以是超前進位。逐位進位也稱串列進位,其邏輯電路簡單,但速度也較低。器物分類 半加器 能對兩個1位二進制數進行相加求和及進位的邏輯電路稱為半加器。或:只考慮兩個一位二進制數的相加,而不考慮來自低位...

1、被加數A(32位)2、被加數B(32位)3、前一位的進位CIN(1位)4、此位二數相加的和S(32位)5、此位二數相加產生的進位COUT(1位)要實現32位的二進制加法,一種自然的想法就是將1位的二進制加法重複32次(即逐位進位加法器)。這樣做無疑是可行且易行的,但由於每一位的CIN都是由前一位的COUT...

這種計算方法是很簡單的,加法在系統中是連續並行處理的。為了減小延遲和占用面積。逐位進位加法器可以用進位保留加法器取代。這樣的話,每一個進位和求和信號都可以在下一個階段通過加法器。最終的結果在最末端的加法器中獲取。在陣列乘法器中我們需要相加的部分乘積要和乘數的比特數一樣多。這種排列如圖6所示:

異步計數器是異步時序電路,其主要特點是內部各觸發器的時鐘脈衝端CP不全都連線在一起,因此各觸發器的翻轉時刻有先有後,其輸出可能會產生干擾毛刺現象,但其電路結構簡單。異步二進制加法計數器 異步二進制計數器在做加法計數時是以從低位到高位逐位進位的方式T作的。因此,其中的各個觸發器不是同步翻轉的。按照...

種就是所謂的並行相加、逐位進位的串列方式。其優點是結構簡單,缺點 是運算速度較低。為了提高運算速度,通常採用超前進位的方法(如超前進位四位全加器74LS283)。【實驗內容及步驟】1.半加器邏輯功能的測試 把Ai、Bi連線到電平輸入端,Si、Ci連線到電平顯示端。按照邏輯 真值表分別輸入各組輸入狀態電平值,記錄Si...

要實現32位的二進制加法,一種自然的想法就是將1位的二進制加法重複32次(即逐位進位加法器)。這樣做無疑是可行且易行的,但由於每一位的CIN都是由前一位的COUT提供的,所以第2位必須在第1位計算出結果後,才能開始計算;第3位必須在第2位計算出結果後,才能開始計算,等等。而最後的第32位必須在前31位...

3.6.3逐位進位加法器 3.6.4基本的二進制加法/減法器 3.6.5基本的十進制加法器 3.7運算器的組成和結構 3.7.1多功能算數/邏輯運算單元(ALU)3.7.2內部匯流排 3.7.3運算器的基本結構 思考題與習題 第4章 中央處理器 4.1中央處理器的功能和組成 4.1.1中央處理器的功能 4.1.2中央處理器的組成 4...

因此將這種結構的電路稱為串列進位加法器(或稱為行波進位加法器)。其最大的特點是運算速度慢。2、超前進位加法器。可以通過邏輯電路實現得出每一位全加器的進位輸入信號,無需再從最低位開始向高位逐位傳遞進位信號。優勢在於提高了運行速度,但是當加法器的位數增加時,電路的複雜程度也隨之急劇上升。

移位操作指令是一組經常使用的指令,屬於彙編語言邏輯指令中的一部分,它包括移位指令(含算術移位指令、邏輯移位指令),循環移位指令(含帶進位的循環移位指令),雙精度移位指令三大類。其功能為將目的運算元的所有位按操作符規定的方式移動1位或按暫存器CL規定的次數(0~255)移動,結果送入目的地址。目的運算元是...

01相加,最低位產生的進位將逐位影響至最高位。因此,並行加法器的最長運算時間主要是由進位信號的傳遞時間決定的。提高並行加法器速度的關鍵是儘量加快進位產生和傳遞的速度。進位的產生和傳遞 進位表達式:Ci=AiBi+(Ai⊕Bi)Ci-1 Gi的含義是:若本位的兩個輸入均為1,必然要向高位產生進位。Pi的含義是:當兩個...

位數對齊,高位算起,同位相加,本檔滿10向前檔進。運算方法 選定一個計位點作為個位檔,個位檔一經選定,在整個運算過程中應保持不變。將被加數從左至右按數的位次順序撥在算盤上。將加數分別對準被加數的位次,從左至右逐位相加。在運算過程中,本檔滿10,則向前檔撥一顆下珠靠梁為進位。最後算盤上靠梁的算...

對於加法運算,如果次高位(數值部分最高位)形成進位加入最高位,而最高位(符號位)相加(包括次高位的進位)卻沒有進位輸出時,或者反過來,次高位沒有進位加入最高位,但最高位卻有進位輸出時,都將發生溢出。因為這兩種情況是:兩個正數相加,結果超出了範圍,形式上變成了負數;兩負數相加,結果超出了範圍,...

得數的十位數確定方法是,取兩數的個位與十位分別交叉相乘的和加上個位進位數總和的尾數,為得數的十位數。具體到上面例子,2×5+4×6+1=35,其中,5為得數的十位數,3為十位進位數;得數的其餘部分確定方法是,取兩數的十位數的乘積與十位進位數的和,就是得數的百位或千位數。具體到上面例子,4×5+...

7.5.2 先行進位的實現 204 7.6 定點運算器的組成 205 7.6.1 內部匯流排 206 7.6.2 帶有累加器的簡單運算器 208 7.6.3 單匯流排移位乘除運算器 209 7.6.4 三匯流排陣列乘除運算器 210 7.7 浮點運算和浮點運算器 211 7.7.1 浮點加/減法 211 7.7.2 浮點乘/除法 213 7.7.3 捨入處理 214 7.7...

第3課時筆算乘法(不進位)(1)/26 第4課時筆算乘法(不進位)(2)/27 第5課時筆算乘法(進位)(1)/28 第6課時筆算乘法(進位)(2)/29 第7課時用乘法兩步計算解決問題(1)/30 第8課時用乘法兩步計算解決問題(2)/31 第9課時用除法兩步計算解決問題(1)/32 第10課時用除法兩步計算解決...

4、~(按位非):對該整數的二進制形式逐位取反。5、6、>> 右移:m>>n的含義為把整數m表示的二進制數右移n位,m為正數,高位全部補0,m為負數,高位全部補1。按位加運算符其實就是按位異或,屬於邏輯運算指令。按位加運算不考慮進位,所以運算時,相同為0,相異為1。按位加 用按位運算實現加法也就是...

拓展數學思維,設立了“小數學家”欄目,內容是與教材該節知識相關的思維訓練題,並在“思路點撥”欄目中給出了解題思路和方法指導,便於學生自學和家長輔導。圖書目錄 準備課 位置 1~5的認識和加減法 認識圖形(一)6~10的認識和加減法 11~20各數的認識 認識鐘錶 20以內的進位加法 總複習 ...

在加法方面,發明了一位數加法的指算加法:直加、反手加。減內湊反手加、加外湊反手加,進1減補加;提出了多位數加法的新法則:數位對齊,高位加起,寫十記個,升個為十,串加下位,逐位右移,在乘法方面,總結出乘數是一位數乘法的8條進位規律共36句口訣和8條個位規律共13句口訣,以及一條求乘積的每位數...

同時,牢固樹立過“緊日子”思想,把有限的財力用在“三保”上,用在“刀刃”上;三是“進”,就是要跳起來摘桃子,通過努力工作付出,來取得好的業績,爭先進位。淶水既要仰望星空,懷揣夢想;又要腳踏實地,苦幹實幹。 做好政府工作,落實縣委全會要求,我們將以“三創四建”為統領,重點在以下七個方面攻堅發力。(一)在...

對於序數的集合S,mex(S)定義為“局外最小序數”,也就是說序數中不是S的元素的最小一個。對於有限序數,尼姆和可以簡單地通過將相加的各個數字的二進制表示逐位進行不進位的加法而得到(例如:100010+110010=10000)。 遞歸定義 αβ=mex{α′β+αβ′−α′β′:α′<α,β′<β}=mex{α′β+α...

在乘法器電路中,乘數中的每一位都要和被乘數的每一位相與,並產生其相應的乘積位。這些局部乘積要饋入到全加器的陣列中(合適的時候也可以用半加器),同時加法器向左移位並表示出乘法結果。最後得到的乘積項在CLA電路中相加。注意,某些全加器電路會將信號帶入到進位輸入端(用於替代鄰近位的進位)。這就是一...

此式中未標明πk-1的諸值,某位加得的πk即為左側高一位的πk-1。此例中最高進位π4=1,表示字元相加有進位,它可以取作多位字元相加中的位間進位數;或者作為一種控制標誌,或者捨棄不用。一位二進制數相減 兩個一位二進制數相減的基本規則是,字元運算不包括符號,負數的標誌可用有無借位數來表示。實際...

方向 DN(減少) UP(增加) 輔助進位 AC NA(無進位)中斷 EI(許可) DI(禁止) 奇偶標誌 PE(偶) PO(奇)符號 NG(負) PL(正) 進位 CY NC(清除進位)例:-Rf NV UP EI PL NZ NA PO NC :-OV DI← 輸入值 S命令 功能: 在指定的地址範圍內查找給定的字元串。說明: 用來指定在地址...

三進制是以3為底數的進位制,三進制數有0、1、2三個數碼,逢三進一。在計算機發展的早期,採用了一種偏置了的三進制碼(對稱三進制),有-1、0、1三個數碼,這種三進制逢+/-2進一。定義 三進制碼是以3為底數的進制代碼,逢三進一、退一還三。三進制碼採用0、1、2三個數碼,從小數點往左依次是個位...

5進位以及10進位制是人類普遍採用的記數方法,因此很早就用來計算與編制。中國古代軍隊的基本編制單位就是一五一十的“什伍”之制。另外古代展開軍隊作戰時往往會排列成左、右兩路或左、中、右三路的陣勢,由此影響到軍隊要採用2進位或3進位(包括其倍數)的編制。商代開創的這種“什伍”之制後來被周朝繼承,而周代...

與四則運算不同的是模2運算不考慮進位和借位,即模2加法是不帶進位的二進制加法運算,模2減法是不帶借位的二進制減法運算。這樣,兩個二進制位相運算時,這兩個位的值就能確定運算結果,不受前一次運算的影響,也不對下一次造成影響。模二加法 所謂“模2加法”就是0和1之間的加法,其中0+0 =0,1+0 =0+...

六十進制是以60為基數的進位制。印度-阿拉伯數字,就是一個以10為底的計數與演算系統。例如,在234中的2代表200,25中的2代表20,而102中的2就代表2。在一個完整的進制系統中,必須要有代表“零”的符號,才能將可能缺項的位數補零。直式加減乘除,就是建立在這樣的位值系統上。至於不使用進制的系統,大概...