硬體乘法器是現代計算機中必不可少的一部分,其基礎是加法器結構。

概念

數位訊號處理器(DSP)

數位訊號處理器(DSP)實現原理

硬體乘法器是現代計算機中必不可少的一部分,其基礎是加法器結構。

數位訊號處理器(DSP)

數位訊號處理器(DSP)

硬體乘法器是現代計算機中必不可少的一部分,其基礎是加法器結構。...... 硬體乘法器,其基礎就是加法器結構,它已經是現代計算機中必不可少的一部分。[1] 乘法器...

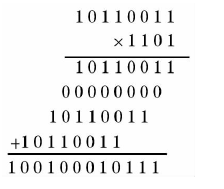

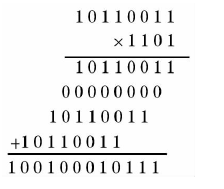

乘法器(multiplier)是一種完成兩個互不相關的模擬信號相乘作用的電子器件。它可以將兩個二進制數相乘,它是由更基本的加法器組成的。乘法器可以通過使用一系列計算機...

實驗十一 用狀態機實現序列檢測器第7章 綜合設計性實驗實驗一 16×16點陣顯示控制實驗二 數控分頻器實驗三 8位硬體乘法器實驗四 ADC轉換控制器...

微控制器硬體乘法器 集成的硬體乘法器模組執行高速乘法、乘方和累加操作,並能在一個周期內完成一個16位×16位乘法和累加操作。硬體乘法器由2個]6位並行載入操作...

例如:為了節省資源,減法器和硬體乘法器都可由加法器來構成。但寬位加法器的設計是很耗費資源的,因此在實際的設計和相關係統的開發中需要注意資源的利用率和進位...

1978年,Intel發布了一種“模擬信號處理器”——2920處理器。它包含一組帶有一個內部信號處理器的片上ADC/DAC,但由於它不含硬體乘法器,因此在市場上銷售並不成功...

數位訊號處理器是一種具有特殊結構的微處理器晶片,其內部採用程式和數字分開的結構[稱為哈佛結構(Harvard)],具有專門的硬體乘法器,廣泛採用流水線操作,提供特殊的...

DSP(Digital Signal Processor),即數位訊號處理器,是一種專用於數位訊號處理的可...⑤內部硬體乘法器,乘法運算時間短、速度快; ⑥高度的集成性,帶有多種存儲器接口...

·單周期的硬體乘法器(8×8) LGT非易失性程式和數據存儲器 ·8K/4K/2K/1K位元組系統內可程式FLASH ·數據保護功能 ·504位元組數據FLASH, 支持位元組讀寫(EEPROM)...

內嵌的Cortex-M3處理器運行速度高達100MHz,1.25DMIPS/MHz的執行效率,且內置MPU和單周期的硬體乘法器和除法器。SmartFusion將成為SOC設計的最佳解決方案。...

DSPs晶片是一種特別適合於做數位訊號處理的微處理器,主要用來實時的實現各種數位訊號處理算法,也叫數位訊號處理器。DSPs晶片具有乘法器和多功能單元。由於DSPs的主要...

在ARM核的命名規則中,TDMI的基本含義為: T: 支持高密度16位的Thumb指令集; D: 支持片上Debug; M:內嵌硬體乘法器(Multiplier); I: 嵌入式ICE,支持片上斷點...

ATmega169是基於增強的AVR RISC結構的低功耗8位CMOS微控制器。由於其先進的指令...只需兩個時鐘周期的硬體乘法器· 非易失性程式和數據存儲器–16K 位元組的系統...

ATmega16是基於增強的AVR RISC結構的低功耗8 位CMOS微控制器。由於其先進的指令...l 只需兩個時鐘周期的硬體乘法器l 非易失性程式和數據存儲器l 16K 位元組的...

ROM 選項:2KB – 32KB RAM 選項:512B – 1KB GPIO 選項:14、40 引腳 ADC 選項:14 位斜率 SAR 其它集成外設:LCD 控制器、硬體乘法器430x4xx系列...

CycloneII:Cyclone的下一代產品,2005年開始推出,90nm工藝,1.2v核心供電,屬於低成本FPGA,性能和Cyclone相當,提供了硬體乘法器單元。CycloneIII FPGA系列2007年推出,採用...

被廣泛的套用在了汽車電車管理、門禁系統、遙控器、智慧型家居、以及計量電錶等領域...– 只需兩個時鐘周期的硬體乘法器· 非易失性的程式和數據存儲器–128K 位元組...

ATmega8535是基於增強的AVR RISC結構的低功耗8位CMOS微控制器。由於其先進的指令...– 只需兩個時鐘周期的硬體乘法器· 非易失性程式和數據存儲器...

ATmega128-16AU,8位AVR微處理器,帶128KB在系統可程式Flash,生產廠家為美國ATMEL...只需兩個時鐘周期的硬體乘法器非易失性的程式和數據存儲器128K 位元組的系統內可...