基本介紹

- 中文名:串列加法器

- 外文名:serial adder

- 學科:計算機科學與技術

- 類別:加法器

- 方式:串列

- 優點:減少硬體資源占用率

基本概念

串列加法器設計

1位串列加法器

2位串列加法器

套用

串列加法器即加法器執行位串列行操作,利用多個時鐘周期完成一次加法運算,即輸入運算元和輸出結果方式為隨時鐘串列輸入/輸出。在實際生活中,希望減少硬體資源占用率時,就可以使用位串列加法器。基本概念 PU、MCU及DSP等電子器件中的加法...

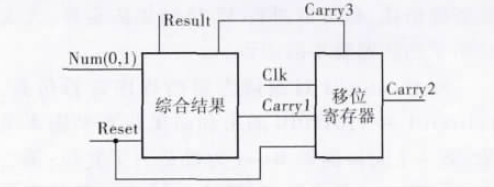

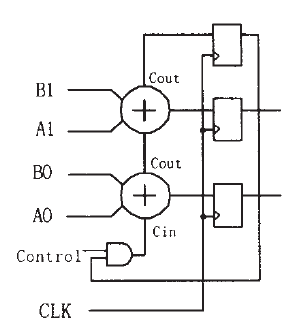

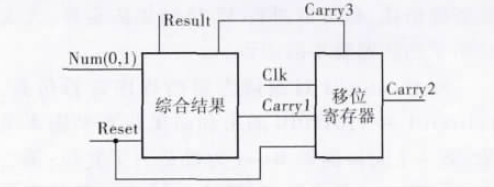

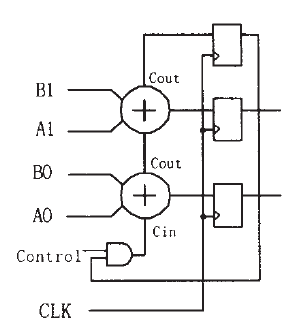

1位串列加法器 二進制數的加法過程是從最低位開始的,低位決定進位數:1和1相加就進1,其他進位0。下一位運算元與上一位進位決定本位相加結果:進位和運算元中1的個數不大於1則進位為0,否則進位為1。圖1 位串列加法器採用輸入...

1、串列進位加法器。每一位的相加結果都必須等到低一位的進位產生以後才能建立起來,因此將這種結構的電路稱為串列進位加法器(或稱為行波進位加法器)。其最大的特點是運算速度慢。2、超前進位加法器。可以通過邏輯電路實現得出每一位全...

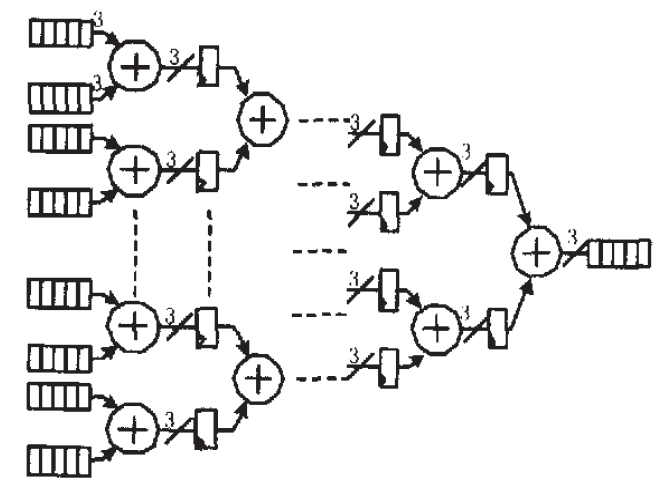

這樣的方法,使得實現32位的二進制加法所需的時間是實現1位的二進制加法的時間的32倍。基本方法 可以看出,上法是將32位的加法1位1位串列進行的,要縮短進行的時間,就應設法使上敘進行過程並行化。逐位進位加法器,在每一位的計算...

因此我們可以通過三個8421BCD碼加法器的相連組成一個三位串列進位並行加法器,這樣通過低位向高位產生進位進行十進制的加法運算,最後通過連線數碼管顯示所得的結果。當輸入二進制數的時候,兩個串接的74LS283四位加法器進行加法運算,產生...

行波進位加法器 行波進位加法器是將n個一位全加器串接起來進行兩個n位數的相加,進位是採用串列進位的方法來實現的,即本級的 作為下一級的 參與加法運算。其邏輯表達式為:同時 所以,串列進位鏈的總延遲時間與字長成正比,字長越...

二進制加法器是一種能產生兩個二進制數算術和的組合邏輯部件,能計算兩個二進制數的加法。簡介 被加數和加數的各位能同時並行到達各位的輸入端,而各位全加器的進位輸入則是按照由低位向高位逐級串列傳遞的,各進位形成一個進位鏈。由於...

這種加法器在進行任一位加法運算時,都必須等到比它低位的加法運算結束送來進位時才能進行。運算的進位,是從低位向高位以串形方式逐位進位。這種串列加法器電路雖然簡單,由於最高位的運算一定要等到所有的低位運算都完成並送來進位信號時...

2.5.1 串列加法器和並行加法器 2.5.2 算術邏輯單元ALU的功能和結構 2.5.3 真題與習題精編 2.5.4 答案精解 2.6 重難點答疑 2.7 命題研究與模擬預測 2.7.1 命題研究 2.7.2 模擬預測 ...

並行進位加法器設有並行進位產生邏輯,運算速度快;串列進位方式是將全加器級聯構成多位加法器。通常,並行加法器比串列級聯加法器占用更多的資源,並且隨著位數的增加,相同位數的並行加法器比串列加法器的資源占用差距也會越來越大。四位...

2.4.1 串列加法器和並行加法器 76 2.4.2 算術邏輯單元的功能和結構 79 2.4.3 本節習題精選 80 2.4.4 答案與解析 81 2.5 本章小結 82 2.6 常見問題和易混淆知識點 83 第3章 存儲系統 86 3.1...

2.4.1 串列加法器和並行加法器(71)2.4.2 算術邏輯單元的功能和結構(74)2.4.3 本節習題精選(76)2.4.4 答案與解析(77)2.5 常見問題和易混淆知識點(78)第3章 存儲系統的層次結構(81)3.1 存儲器的分類(82)3.1.1 ...

7.2 串列加法器131 7.3 計數器132 7.3.1 概述132 7.3.2 二進制異步計數器133 7.3.3 二進制同步計數器 134 7.3.4 非二進制計數器137 7.3.5 組合計數器140 本章小結141 習題7141 第8章 脈衝信號的產生與整形142 8....

2.4.1 串列加法器和並行 加法器 170 2.4.2 算術邏輯單元的功能和 結構 172 例題精析 174 習題精選 175 參考答案 178 第3章 存儲器系統的層次結構 182 3.1 存儲器的分類 182 3.1.1 存儲器的分類 ...

2.14 計數器及其套用 2.15 同步時序電路的設計 2.16 TTL門組成的脈衝電路 2.17 集成脈衝電路及其套用 2.18 555定時器及其套用 2.19 A/D和D/A轉換器 第三章 綜合實驗 3.1 數字鐘 3.2 電子秒表 3.3 串列加法器 3.4 ...

實驗十三 D/A、A/D轉換器 實驗十四 隨機存取存儲器2114A及其套用 實驗十五 可程式器件GAL的一般設計過程及編程技術 綜合設計一 串列加法器的設計 綜合設計二 電子秒表設計 綜合設計三 簡易彩燈循環控制器設計 綜合設計四 交通燈控制器...

9.3 串列加法器237 9.4 波形發生和變換電路238 9.5 定時預警電路242 9.6 數字搶答器243 9.7 數字頻率計247 9.8 交通信號燈250 9.9 霓虹燈顯示控制電路253 本章小結257 習題9 257 第10章 EDA技術與VHDL 10.1 VHDL編程...

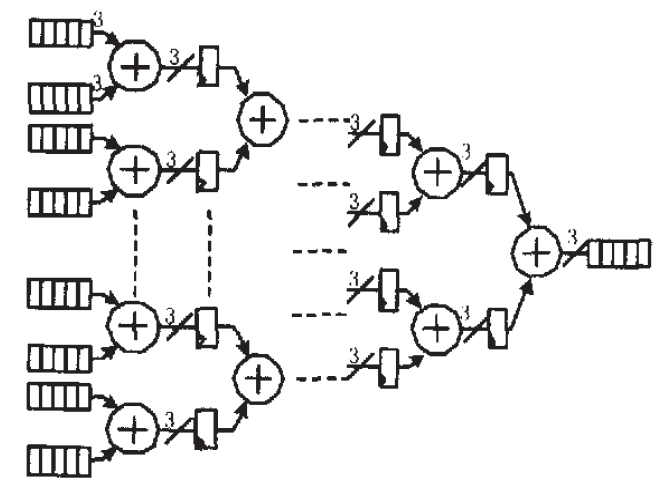

7.2 8位串列加法器的設計 132 7.2.1 基本元件的設計 132 7.2.2 8位串列加法器的頂層設計 135 7.3 24小時計時器的設計 137 7.3.1 2千萬分頻器的設計 137 7.3.2 60進制分頻器的設計 138 7.3.3 24進制分頻器的設計 ...

二十四、CC4026十進制計數器/脈衝分配器(七段解碼輸出)二十五、CC4027雙上升沿JK觸發器 二十六、CC4028 4線-10線解碼器(BCD輸入)二十七、CC4029 4位二進制/十進制加/減計數器(有預置端)二十八、CC4032三串列加法器(正邏輯)二十九、...

2.4.1串列加法器和並行加法器73 2.4.2算術邏輯單元的功能和結構76 2.4.3本節習題精選77 2.4.4答案與解析78 2.5常見問題和易混淆知識點79 第3章存儲系統83 3.1存儲器的層次結構84 3.1.1存儲器的分類84 3.1.2存儲器的...

2.4.1 串列加法器和並行加法器 75 2.4.2 算術邏輯單元的功能和結構 79 2.4.3 本節習題精選 80 2.4.4 答案與解析 81 2.5 本章小結 82 2.6 常見問題和易混淆知識點 83 第3章 存儲系統 86 3.1...

2.4.1 串列加法器和並行加法器 82 2.4.2 算術邏輯單元的功能和結構 85 2.4.3 本節習題精選 86 2.4.4 答案與解析 87 2.5 本章小結 88 2.6 常見問題和易混淆知識點 89 第3章 存儲系統 92 3.1...

2.4.1 串列加法器和並行加法器 79 2.4.2 算術邏輯單元的功能和結構 82 2.4.3 本節習題精選 83 2.4.4 答案與解析 84 2.5 本章小結 85 2.6 常見問題和易混淆知識點 86 第3章 存儲系統 89 3.1 存儲器的層次結構 90...

2.4.1 串列加法器和並行加法器 71 2.4.2 算術邏輯單元的功能和結構 74 2.4.3 本節習題精選 76 2.4.4 答案與解析 76 2.5 本章小結 77 2.6 常見問題和易混淆知識點 78 第3章 存儲系統 82 3.1...

3.2無符號數的加法125 3.2.1全加器的分解129 3.2.2行波進位加法器129 3.2.3設計實例130 3.3有符號數132 3.3.1負數133 3.3.2加法和減法135 3.3.3加法器和減法器單元138 3.3.4基數補碼方案139 3.3.5算術溢出143 3...

2.4.1 串列加法器和並行加法器 75 2.4.2 算術邏輯單元的功能和結構 79 2.4.3 本節習題精選 80 2.4.4 答案與解析 81 2.5 本章小結 82 2.6 常見問題和易混淆知識點 83 第3章 存儲系統 86 3.1 存儲器的層次結構 87...

3.2.1串列進位加法器71 3.2.2並行進位加法器72 3.2.3帶標誌加法器73 3.2.4算術邏輯部件74 3.3定點數運算75 3.3.1補碼加減運算75 *3.3.2原碼加減運算77 *3.3.3移碼加減運算77 3.3.4原碼乘法運算78 3.3.5補碼乘法...

2.4.1 串列加法器和並行加法器 2.4.2 算術邏輯單元的功能和結構 習題 習題答案 第3章 存儲器層次結構 大綱要求 考點與要點分析 本章知識體系框架圖 知識點講解 3.1 存儲器的分類 3.2 存儲器的層次化結構 3.3 半導體隨機存取...

(10)算術邏輯單元ALU,包括串列加法器和並行加法器的邏輯表示和邏輯圖,算術邏輯單元ALU的功能和機構(即ALU的功能和基本組成)。 9.1 考點歸納與考點分析 120 9.2 進位計數制及其相互轉換 ★4◎5 121 ...