基本介紹

- 中文名:逐位進位

- 外文名:cascaded carry

- 別名:串聯進位

- 相關概念:邏輯電路、加法器、二進制等

基本介紹,相關分析,

基本介紹

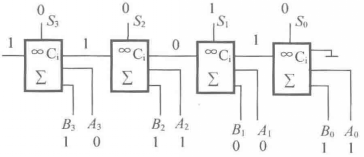

全加器是常用的二進制加法運算電路,能夠實現多位二進制加法運算的電路稱為多位加法器。4位二進制加法器是一種常用的全加器。在一位加法器的基礎上,組成多位加法器時,主要是考慮進位方式問題。進位方式有兩種,即逐位進位(又稱串聯進位)和超前進位(又稱並聯進位)。逐位進位的4位加法全加器如圖1所示,它由4個全加器串聯組成。如輸入的被加數A為0101,加數B為1101,得和數S為(C3=1)0010。這種加法器在進行任一位加法運算時,都必須等到比它低位的加法運算結束送來進位時才能進行。運算的進位,是從低位向高位以串形方式逐位進位。這種串列加法器電路雖然簡單,由於最高位的運算一定要等到所有的低位運算都完成並送來進位信號時才能進行,運算速度慢,一般用於對運算速度要求不高的設備中。要求提高運行速度,應儘量縮短高位形成的全加和的時間,可選取超前進位全加器。現有許多積體電路,如74LS283、CC4008等都是超前進位的全加器。

圖1

圖1相關分析

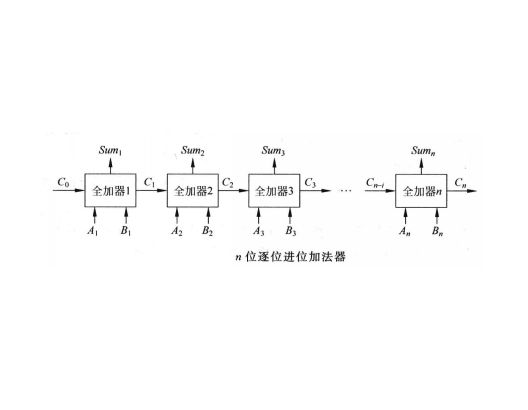

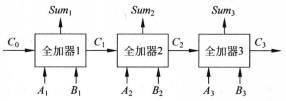

逐位進位加法器屬於串列進位加法器。圖2所示為用全加器構成的n位逐位進位加法器,如果沒有初始進位 ,最低位(全加器1)應改為半加器。

,最低位(全加器1)應改為半加器。

圖2(a)n位逐位進位加法器

圖2(a)n位逐位進位加法器 圖2(b)n位逐位進位加法器

圖2(b)n位逐位進位加法器逐位進位加法器結構簡單,但是由於進位信號是從低位到高位逐位求得,使各位的“和”也是從低位到高位逐位求得,也就是高位需要等它的低位進位運算結果出來後才能進行運算。因此,得到最終的“和”和“進位”輸出結果延遲時間較長。而且隨著加法器的位數增加,延遲時間也在增加。為了減小逐位進位加法器的延遲,在全加器設計中,應儘量減小進位的延遲。通常將晚到的進位信號C控制的MOS管靠近邏輯門的輸出端,以便在C到來之前內部節點依據先到的A和B預先完成充放電。

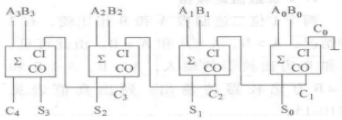

圖3

圖3圖3所示為4位串列進位加法器電路。它由4個全加器構成。最低有效位全加器的進位輸入端C0接地。輸出數碼C4S3S2S1S0表示了二進制數A3A2A1A0和B3B2B1B0之和。顯然,每一位的加法運算必須要等到低一位的進位產生後才能進行,因此,把這種結構的電路稱為串列進位(或逐位進位)加法器。

逐位進位加法器最大缺點是運算速度慢。在最不利的情況下,做一次加法運算需要經過4個全加器的傳輸延遲時間(從輸入加數到輸出狀態穩定建立起來所需要的時間)才能得到穩定可靠的運算結果。但考慮到串列進位加法器的電路結構比較簡單,因而在對運算速度要求不高的設備中,這種加法器仍不失為一種可取的電路。例如TTL積體電路中T692就屬於這種串列進位加法器。

若要提高運算速度,必須設法減小由於進位信號逐級傳遞所耗費的時間,一般採用超前進位(又稱先行進位)的方法,即每一位的進位直接由被加數和加數決定,而不需依賴低位的進位。