串列加法器即加法器執行位串列行操作,利用多個時鐘周期完成一次加法運算,即輸入運算元和輸出結果方式為隨時鐘串列輸入/輸出。在實際生活中,希望減少硬體資源占用率時,就可以使用位串列加法器。

基本介紹

- 中文名:串列加法器

- 外文名:serial adder

- 學科:計算機科學與技術

- 類別:加法器

- 方式:串列

- 優點:減少硬體資源占用率

基本概念

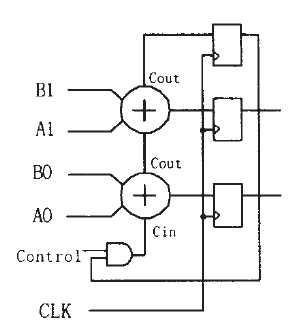

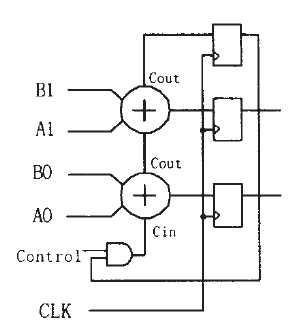

串列加法器設計

1位串列加法器

2位串列加法器

套用

增加了硬體資源的消耗,所以在處理能力滿足的條件下,應該選擇比較小的位寬。

串列加法器即加法器執行位串列行操作,利用多個時鐘周期完成一次加法運算,即輸入運算元和輸出結果方式為隨時鐘串列輸入/輸出。在實際生活中,希望減少硬體資源占用率時,就可以使用位串列加法器。

串列加法器即加法器執行位串列行操作,利用多個時鐘周期完成一次加法運算,即輸入運算元和輸出結果方式為隨時鐘串列輸入/輸出。在實際生活中,希望減少硬體資源占用率時...

串列二進制加法器即加法器執行位串列行操作,利用多個時鐘周期完成一次加法運算,即輸入運算元和輸出結果方式為隨時鐘串列輸入/輸出。...

多位加法器的構成有兩種方式:並行進位和串列進位方式。並行進位加法器設有並行進位產生邏輯,運算速度快;串列進位方式是將全加器級聯構成多位加法器。通常,並行加法...

加法器是產生數的和的裝置。加數和被加數為輸入,和數與進位為輸出的裝置為半加器。若加數、被加數與低位的進位數為輸入,而和數與進位為輸出則為全加器。常用...

8位加法器就是實現兩個 8位二進制相加,其結果的範圍應該在00000000到111111110之間,八位二進制數換算成三位十進制數最大為255,也就是說要輸入兩個000到255之間...

多位加法器是兩個多位數相加時每一位都是帶進位相加的,因而必須使用。...... 1、串列進位加法器。每一位的相加結果都必須等到低一位的進位產生以後才能建立起來...

全加器是能夠計算低位進位的二進制加法電路。與半加器相比,全加器不只考慮本位計算結果是否有進位,也考慮上一位對本位的進位,可以把多個一位全加器級聯後做成...

二進制加法器是一種能產生兩個二進制數算術和的組合邏輯部件。...... 同時並行到達各位的輸入端,而各位全加器的進位輸入則是按照由低位向高位逐級串列傳遞的,各...

超前進位加法器(carry look ahead adder)是對普通的全加器進行改良而設計成的並行加法器,主要是針對普通全加器串聯時互相進位產生的延遲進行了改良。超前進位加法器...

把n個全加器串接起來,就可進行兩個n位數的相加。串列進位又稱行波進位,每一級進位直接依賴於前一級的進位,即進位信號是逐級形成的。 串列進位鏈的總延遲時間與...

實現這一功能的邏輯電路叫全加器 [1] 。2.加法器實現多位二進制數相加的電路稱為加法器。根據進位方式不同,有串列進位加法器和超前進位加法器兩種 [1] 。...

圖2—3四位串列全加器圖2—4四位超前進位全加器 【實驗內容及步驟】 1.半加器邏輯功能的測試 把Ai、Bi連線到電平輸入端,Si、Ci連線到電平顯示端,如圖2-1...

具體內容包括計算機系統概論、運算方法和運算部件、指令系統、控制器部件、存儲系統...2.1.2 串列加法器與並行加法器 182.1.3 算術邏輯單元 202.2 定點數加減...

從上面可以清晰地看出,數乘已經被轉換成了加法運算。如果部分乘積被連續相加,因此一個串列加法器就可以和硬體一起使用。在組合電路中通過並行乘法器將所有的部分乘積...