基本介紹

- 中文名:後道工序

- 外文名:Back end of line

- 英文縮寫:BEOL

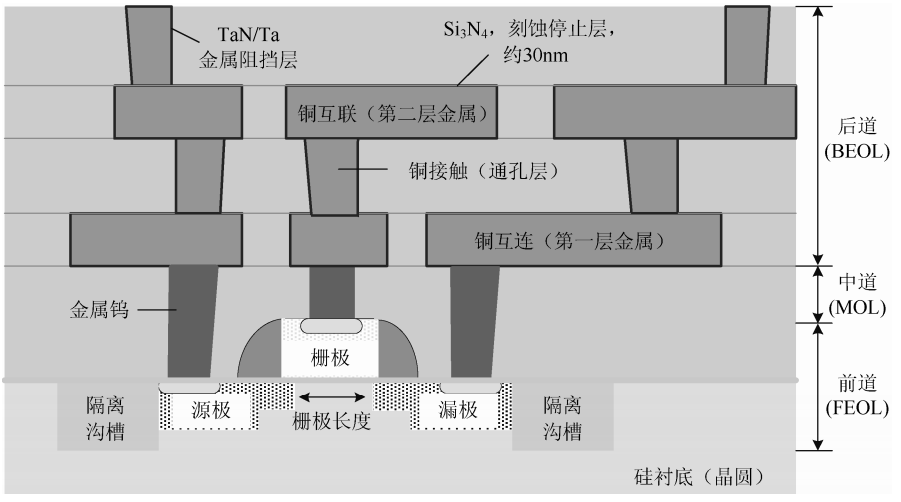

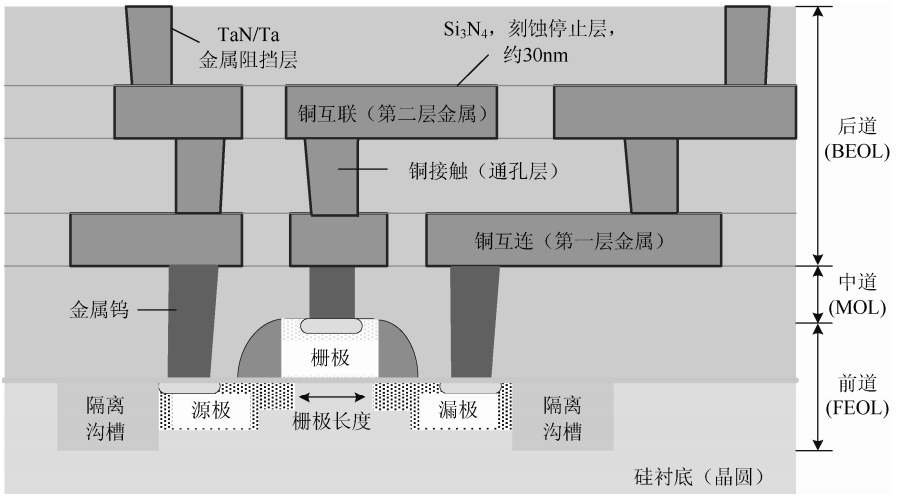

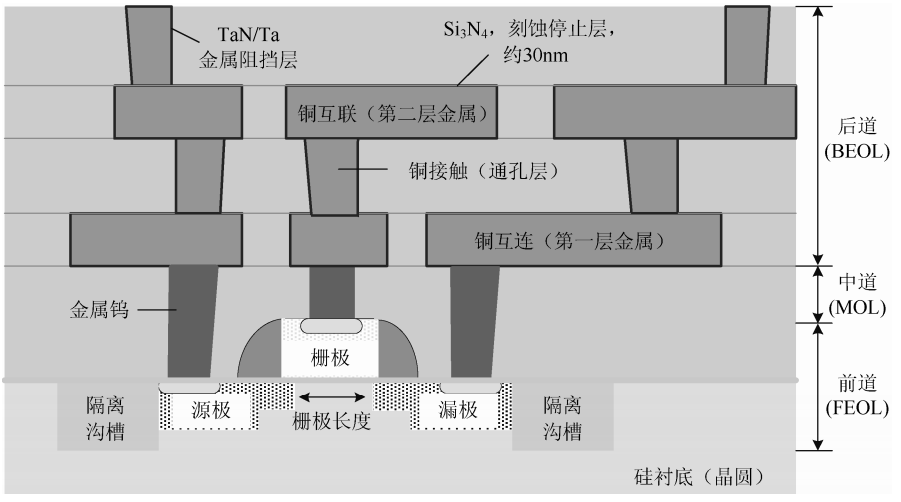

這部分工藝流程是為了在 Si 襯底上實現N型和P型場效應電晶體,又被稱為前道工藝(front end of line,FEOL)。與之相對應的是後道(back end of line,BEOL)...

在產品加工過程中,需要一道以上的工序才能夠完成,那么,除第一道工序外,對於第二、第三...直至最後一道工序,都可以被叫做前一道工序的“後道工序”。同樣,除...

後道hòu dào 中午飯後2--3小時的一道菜或飯食! 上黨地區上世紀八十年代前,六月走夏〈小輩去長輩家〉,七月送羊〈長輩給晚輩送〉,過年時走親訪友或給孩子...

絡筒(又稱絡紗)是織前準備的第一道工序,它的任務是將來自紡部的管紗或絞紗在絡筒機上加工成符合一定要求的筒子。絡筒作為紡紗的最後一道工序和織造的首道...

4)付下道工序有亞大影響的工序。5)加工周期長、原材料貴重、—旦出了問題損失嚴重的工序(特別是後道工序)。(4)編制控制點檔案。控制點的主要控制檔案有:...

印花工藝是用染料或顏料在紡織物上施印花紋的工藝過程。印花有織物印花、毛條印花和紗線印花之分,而以織物印花為主。毛條印花用於製做混色花呢;紗線印花用於織造...

絡筒(又稱絡紗)是織前準備的第一道工序,它的任務是將來自紡部的管紗或絞紗在絡筒機上加工成符合一定要求的筒子。...

推動式生產(Push Production)是指按照MRP的計算邏輯,各個部門都是按照公司規定的生產計畫進行生產。上工序無需為下工序負責,生產出產品後按照計畫把產品送達後工序...

它要求後道工序的工人憑“領料看板”到前一道工序領取必要數量的零件。前一道工序的工人根據“生產看板”生產規定數量的零件;搬運工人憑“送貨看板”在規定的時間內...

對於加工裝配式生產,產品由許多零件構成,每個零件要經過多道工序加工。要組織這樣的生產,可以採用兩種不同的傳送生產指令的方式。一種就是推進式方法。由一個計畫...

光纖余長通常都是在套塑工序中進行調節和控制,後道工序只能是保持余長的穩定。 擠塑過程中余長的變化受到眾多工藝參數的影響,包括了平行鋼絲放線張力、套管放張力...

每一道工序是前道工序的用戶每一道工序是後道工序的供貨商每一道工序只接受前道工序合格的產品每一道工序只生產合格的產品每一道工序只提供合格的產品給後道工序...

平行移動方式指一批零件中的每個零件在每道工序完畢以後,立即轉移到後道工序加工的移動方式。其特點是:一批零件同時在不同工序上平行加工,縮短了生產周期。...

它將傳統生產過程中前道工序向後道工序送貨,改為後道工序根據“看板”向前道工序取貨,看板系統是JIT生產現場控制技術的核心,但JIT不僅僅是看板管理。...

--生產中的節拍可由人工干預、控制,保證生產中的物流平衡(對於每一道工序來說,即為保證對後工序供應的準時化)。--由於採用拉動式生產,生產中的計畫與調度實質上...

推動式生產方式的工作隨著前道工序的結束而前進,不管後道工序是否已經做好準備,或者是否需要;因此,工作可能會堆積在由於設備故障或發現質量問題而落後於進度安排的...

生產中的節拍可由人工干預、控制,但重在保證生產中的物流平衡(對於每一道工序來說,即為保證對後道工序供應的準時化)。由於採用拉動式生產,生產中的計畫與調度...

拉伸性能中的最小強力、最小伸長率等弱環指標可作為後道工序(織造)的參考指標。2目的與要求通過測試,掌握單紗強伸性能的測定方法,了解單紗強力儀的結構和工作原理...

三、拼板聯接: 1.V-CUT聯接:使用分割機分割,這種分割方式斷面平滑,對後道工序無不良影響。2.使用針孔(郵票孔)聯接:需考慮斷裂後的毛刺,及是否影響COB工序的...

平行移動方式是指一批在制品,在上道工序加工完一個零件以後,立即轉入下道工序加工,而無需等待整批加工完後,才向下道工序移動的一種組織生產方式。其優點是生產周期...

減少一切非增值活動,例如檢驗、搬運和等待等造成的浪費,具體方法就是推行“零返修率”,必須做一個零件,在生產的源頭就杜絕不合格零部件、原材料流入生產後道工序。...

豐田公司總經理豐田章一郎指出,他的成功之道就在於:什麼問題都愛倒過來思考。豐田公司所推行的“三及時”原則(時間及時、品種及時、數量及時)明確規定:後道工序在...

退火的目的主要是為了消除和改善前道工序遺留的組織缺陷和內應力,並為後道工序作好組織和性能上的預備,合金結構鋼、保證淬透性結構鋼、冷鐓鋼、軸承鋼、工具鋼、...

通過限定問題,諮詢人員發現,在半軸生產23道工序中,生產能力嚴重失調,其中班產能力為120-190根的有9道工序,主要是機加工設備。班產能力為70-90根的有6道工序,...