效應管,電路符號,工作原理,套用優勢,數字電路,模擬電路,尺寸縮放,尺寸縮小,負面效應,柵極材料,電晶體技術,雙柵極金氧,耗盡式,NMOS邏輯,功率金氧,DMOS,模擬開關,單一開關,雙重開關,

效應管

金屬氧化物半導體場效電晶體(簡稱:

金氧半場效電晶體;英語:

Metal-Oxide-Semiconductor Field-Effect Transistor,

縮寫:

MOSFET),是一種可以廣泛使用在

模擬電路與

數字電路的場效電晶體。金屬氧化物半導體場效應管依照其溝道極性的不同,可分為電子占多數的N溝道型與

空穴占多數的P溝道型,通常被稱為N型金氧半場效電晶體(NMOSFET)與P型金氧半場效電晶體(PMOSFET)。

以金氧半場效電晶體(MOSFET)的命名來看,事實上會讓人得到錯誤的印象。因為MOSFET跟英文單字“metal(

金屬)”的第一個字母M,在當下大部分同類的組件里是不存在的。早期金氧半場效電晶體

柵極使用金屬作為材料,但由於

多晶矽在製造工藝中更耐高溫等特點,許多金氧半場效電晶體柵極採用後者而非前者金屬。然而,隨著半導體特徵尺寸的不斷縮小,金屬作為柵極材料最近又再次得到了研究人員的關注。

金氧半場效電晶體在概念上屬於絕緣柵極場效電晶體(Insulated-Gate Field Effect Transistor,IGFET)。而絕緣柵極場效電晶體的柵極絕緣層,有可能是其他物質,而非金氧半場效電晶體使用的氧化層。有些人在提到擁有多晶矽柵極的場效電晶體組件時比較喜歡用IGFET,但是這些IGFET多半指的是金氧半場效電晶體。

金氧半場效電晶體里的氧化層位於其溝道上方,依照其工作

電壓的不同,這層氧化物的厚度僅有數十至數百

埃(Å)不等,通常材料是

二氧化矽(SiO

2),不過有些新的高級工藝已經可以使用如氮氧化矽(silicon oxynitride, SiON)做為氧化層之用。

今日半導體組件的材料通常以

矽為首選,但是也有些

半導體公司發展出使用其他半導體材料的工藝,當中最著名的例如國際商業機器股份有限公司使用矽與

鍺的混合物所發展的矽鍺工藝(SiGe process)。而可惜的是很多擁有良好電性的半導體材料,如

砷化鎵(GaAs),因為無法在表面長出質量夠好的氧化層,所以無法用來製造金氧半場效電晶體組件。

當一個夠大的電位差施於金氧半場效電晶體的柵極與源極之間時,電場會在氧化層下方的

半導體表面形成感應電荷,而這時就會形成反轉溝道(inversion channel)。溝道的極性與其

漏極(drain)與源極相同,假設漏極和源極是n型,那么溝道也會是n型。溝道形成後,金氧半場效電晶體即可讓電流通過,而依據施於柵極的電壓值不同,可由金氧半場效電晶體的溝道流過的電流大小亦會受其控制而改變。

電路符號

常用於金氧半場效電晶體的電路符號有多種形式,最常見的設計是以一條垂直線代表溝道(Channel),兩條和溝道平行的接線代表源極(Source)與漏極(Drain),左方和溝道垂直的接線代表柵極(Gate),如下圖所示。有時也會將代表溝道的直線以虛線代替,以區分增強型(enhancement mode,又稱增強式)金氧半場效電晶體或是耗盡型(depletion mode,又稱耗盡式)金氧半場效電晶體。

由於

積體電路晶片上的金氧半場效電晶體為四端組件,所以除了源極(S)、漏極(D)、柵極(G)外,尚有一

基極(Bulk或是Body)。金氧半場效電晶體電路符號中,從溝道往右延伸的箭號方向則可表示此組件為n型或是p型的金氧半場效電晶體。箭頭方向永遠從P端指向N端,所以箭頭從溝道指向基極端的為p型的金氧半場效電晶體,或簡稱PMOS(代表此組件的溝道為p型);反之則代表基極為p型,而溝道為n型,此組件為n型的金氧半場效電晶體,簡稱NMOS。在一般分散式金氧半場效電晶體組件中,通常把基極和源極接在一起,故分散式金氧半場效電晶體通常為三端組件。而在積體電路中的金氧半場效電晶體通常因為使用同一個

基極(common bulk),所以不標示出基極的極性,而在PMOS的柵極端多加一個圓圈以示區別。

幾種常見的MOSFET電路符號,加上

結型場效應管一起比較:在金氧半場效電晶體符號中,基極端和源極端均接在一起,一般分立元件的MOSFET幾乎均如此,但在

積體電路中的金氧半場效電晶體則並不一定是這樣連線。通常一顆

積體電路晶片中相同溝道的金氧半場效電晶體都共享同一個基極,故某些情況下的金氧半場效電晶體可能會使得源極和基極並非直接連在一起,例如串疊式電流源(cascode current source)電路中的部分NMOS就是如此。基極與源極沒有直接相連的金氧半場效電晶體會出現

襯底效應(body effect)而部分改變其工作特性,將在後面的章節中詳述。

工作原理

金氧半場效電晶體的核心

金屬—氧化層—半導體結構

場效應管在不同

柵極厚度下的C-V特性曲線。左側為積累,中間為耗盡,右側為反型(反轉)

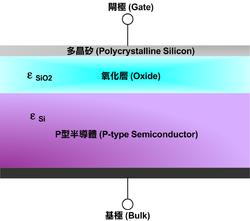

金氧半場效電晶體在結構上以一個

金屬—

氧化物層—

半導體的

電容為核心(現在的金氧半場效電晶體多半以

多晶矽取代金屬作為其柵極材料),氧化層的材料多半是

二氧化矽,其下是作為基極的

矽,而其上則是作為柵極的

多晶矽。這樣的結構正好等於一個

電容器,氧化層為電容器中

介電質,而電容值由氧化層的厚度與二氧化矽的介電係數來決定。柵極多晶矽與基極的

矽則成為MOS電容的兩個端點。

當一個電壓施加在MOS電容的兩端時,半導體的電荷分布也會跟著改變。

累積

考慮一個p型的半導體(

空穴濃度為

NA)形成的MOS電容,當給電容器加負電壓時,電荷增加(如C-V曲線左側所示)。

耗盡

相反,當一個正的電壓

VGB施加在柵極與基極端(如圖)時,空穴的濃度會減少(稱為耗盡,如C-V曲線中間所示),

電子的濃度會增加。

反型

當VGB夠強時,接近柵極端的電子濃度會超過空穴。這個在p-type半導體中,電子濃度(帶負電荷)超過空穴(帶正電荷)濃度的區域,便是所謂的反轉層(inversion layer),如C-V曲線右側所示。

MOS電容的特性決定了金氧半場效電晶體的工作特性,但是一個完整的金氧半場效電晶體結構還需要一個提供

多數載流子(majority carrier)的源極以及接受這些多數載流子的漏極。

MOSFET依照其“通道”的極性不同,可分為n-type與p-type的MOSFET,通常又稱為NMOSFET與pmosFET,其他簡稱尚包括NMOS FET、PMOS FET、nMOSFET、pMOSFET等。

從目前的角度來看MOSFET的命名,事實上會讓人得到錯誤的印象。因為MOSFET里代表“metal”的第一個字母M,在當下大部分同類的組件里是不存在的。早期MOSFET的柵極(gate electrode)使用金屬作為其材料,但隨著半導體技術的進步,現代的MOSFET柵極早已用多晶矽取代了

金屬。

套用優勢

金氧半場效電晶體在1960年由

貝爾實驗室的D. Kahng和Martin Atalla首次實現成功,這種組件的工作原理和1947年蕭克利等人發明的雙載流子接面電晶體截然不同,且因為製造成本低廉與使用面積較小、高集成度的優勢,在

大規模積體電路或是

超大規模積體電路的領域裡,重要性遠超過BJT。

近年來由於金氧半場效電晶體組件的性能逐漸提升,除了傳統上套用於諸如微處理器、微控制器等數位訊號處理的場合上,也有越來越多模擬信號處理的積體電路可以用金氧半場效電晶體來實現,以下分別介紹這些套用。

數字電路

數字科技的進步,如

微處理器運算性能不斷提升,帶給深入研發新一代金氧半場效電晶體更多的動力,這也使得金氧半場效電晶體本身的工作速度越來越快,幾乎成為各種半導體有源組件中最快的一種。金氧半場效電晶體在數位訊號處理上最主要的成功來自互補式金屬氧化物半導體邏輯電路的發明,這種結構最大的好處是理論上不會有靜態的功率損耗,只有在

邏輯門的切換動作時才有電流通過。互補式金屬氧化物半導體邏輯門最基本的成員是互補式金屬氧化物半導體

反相器,而所有互補式金屬氧化物半導體邏輯門的基本工作都如同反相器一樣,同一時間內必定只有一種電晶體(NMOS或是PMOS)處在導通的狀態下,另一種必定是截止狀態,這使得從電源端到接地端不會有直接導通的路徑,大量節省了電流或功率的消耗,也降低了

積體電路的發熱量。

金氧半場效電晶體在數字電路上套用的另外一大優勢是對直流信號而言,金氧半場效電晶體的柵極端阻抗為無限大(等效於開路),也就是理論上不會有電流從金氧半場效電晶體的柵極端流向電路里的接地點,而是完全由電壓控制柵極的形式。這讓金氧半場效電晶體和他們最主要的競爭對手BJT相較之下更為省電,而且也更易於驅動。在CMOS邏輯電路里,除了負責驅動晶片外負載(off-chip load)的

驅動器外,每一級的邏輯門都只要面對同樣是金氧半場效電晶體的柵極,如此一來較不需考慮邏輯門本身的驅動力。相較之下,BJT的邏輯電路(例如最常見的TTL)就沒有這些優勢。金氧半場效電晶體的柵極輸入電阻無限大對於電路設計工程師而言亦有其他優點,例如較不需考慮邏輯門輸出端的

負載效應(loading effect)。

模擬電路

有一段時間,金氧半場效電晶體並非模擬電路設計工程師的首選,因為模擬電路設計重視的性能參數,如電晶體的

跨導或是電流的驅動力上,金氧半場效電晶體不如BJT來得適合模擬電路的需求。但是隨著金氧半場效電晶體技術的不斷演進,今日的CMOS技術也已經可以匹配很多模擬電路的規格需求。再加上金氧半場效電晶體因為結構的關係,沒有BJT的一些致命缺點,如

熱破壞(thermal runaway)。另外,金氧半場效電晶體線上性區的壓控電阻特性亦可在積體電路里用來取代傳統的多晶矽電阻(poly resistor),或是MOS電容本身可以用來取代常用的多晶矽—絕緣體—多晶矽電容(PIP capacitor),甚至在適當的電路控制下可以表現出

電感(inductor)的特性,這些好處都是BJT很難提供的。也就是說,金氧半場效電晶體除了扮演原本電晶體的角色外,也可以用來作為模擬電路中大量使用的被動組件(passive device)。這樣的優點讓採用金氧半場效電晶體實現模擬電路不但可以滿足規格上的需求,還可以有效縮小晶片的面積,降低生產成本。

隨著半導體製造技術的進步,對於集成更多功能至單一晶片的需求也跟著大幅提升,此時用金氧半場效電晶體設計模擬電路的另外一個優點也隨之浮現。為了減少在

印刷電路板上使用的積體電路數量、減少封裝成本與縮小系統的體積,很多原本獨立的模擬晶片與數字晶片被集成至同一個晶片內。金氧半場效電晶體原本在數字積體電路上就有很大的競爭優勢,在模擬積體電路上也大量採用金氧半場效電晶體之後,把這兩種不同功能的電路集成起來的困難度也顯著的下降。另外像是某些

混合信號電路(Mixed-signal circuits),如

模擬數字轉換器,也得以利用金氧半場效電晶體技術設計出性能更好的產品。

近年來還有一種集成金氧半場效電晶體與BJT各自優點的工藝技術:

BiCMOS也越來越受歡迎。BJT組件在驅動大電流的能力上仍然比一般的CMOS優異,在可靠度方面也有一些優勢,例如不容易被

靜電放電破壞。所以很多同時需要復噪聲號處理以及強大電流驅動能力的

積體電路產品會使用BiCMOS技術來製作。

尺寸縮放

過去數十年來,金氧半場效電晶體的尺寸不斷地變小。早期的

積體電路金氧半場效電晶體工藝里,溝道長度約在幾個

微米的檔次。但是到了今日的

積體電路工藝,這個參數已經縮小了幾十倍甚至超過一百倍。2008年初,

Intel開始以45

奈米的技術來製造新一代的

微處理器,實際的組件溝道長度可能比這個數字還小一些。至90年代末,金氧半場效電晶體尺寸不斷縮小,讓積體電路的性能大大提升,而從歷史的角度來看,這些技術上的突破和半導體工藝的進步有著密不可分的關係。

尺寸縮小

MOSFET在概念上屬於“絕緣柵極場效應電晶體”(insulated-Gate Field Effect Transistor, IGFET)。而IGFET的柵極絕緣層,有可能是其他物質,而非MOSFET使用的氧化層。有些人在提到擁有多晶矽柵極的場效應電晶體組件時比較喜歡用IGFET,但是這些IGFET多半指的是MOSFET。

MOSFET里的氧化層位於其通道上方,依照其操作電壓的不同,這層氧化物的厚度僅有數十至數百埃(Å)不等,通常材料是二氧化矽(silicon dioxide, SiO2),不過有些新的高級製程已經可以使用如氮氧化矽(silicon oxynitride, SiON)做為氧化層之用。

今日半導體組件的材料通常以矽(silicon)為首選,但是也有些半導體公司發展出使用其他半導體材料的製程,當中最著名的例如IBM使用矽與鍺(germanium)的混合物所發展的矽鍺製程(silicon-germanium process, SiGe process)。而可惜的是很多擁有良好電性的半導體材料,如砷化鎵(galliumarsenide, GaAs),因為無法在表面長出品質夠好的氧化層,所以無法用來製造MOSFET組件。

當一個夠大的電位差施於MOSFET的柵極與源極(source)之間時,電場會在氧化層下方的半導體表面形成感應電荷,而這時所謂的“反轉通道”(inversion channel)就會形成。通道的極性與其漏極(drain)與源極相同,假設漏極和源極是n-type,那么通道也會是n-type。通道形成後,MOSFET即可讓電流通過,而依據施於柵極的電壓值不同,可由MOSFET的通道流過的電流大小亦會受其控制而改變。

負面效應

雖然金氧半場效電晶體尺寸縮小可以帶來很多好處,但同時也有很多負面效應伴隨而來。

把金氧半場效電晶體的尺寸縮小到一

微米以下對於半導體工藝而言是個挑戰,不過現在的新挑戰多半來自尺寸越來越小的金氧半場效電晶體組件所帶來過去不曾出現的物理效應。

由於金氧半場效電晶體柵極氧化層的厚度也不斷減少,所以柵極電壓的上限也隨之變少,以免過大的電壓造成柵極氧化層

雪崩擊穿(breakdown)。為了維持同樣的性能,金氧半場效電晶體的臨界電壓也必須降低,但是這也造成了金氧半場效電晶體越來越難以完全關閉。也就是說,足以造成金氧半場效電晶體溝道區發生弱反轉的柵極電壓會比從前更低,於是所謂的

亞閾值電流(subthreshold current)造成的問題會比過去更嚴重,特別是今日的

積體電路晶片所含有的電晶體數量劇增,在某些

超大規模積體電路的晶片,次臨限傳導造成的功率消耗竟然占了總功率消耗的一半以上。

不過反過來說,也有些電路設計會因為金氧半場效電晶體的次臨限傳導得到好處,例如需要較高的轉導/電流轉換比(transconductance-to-current ratio)的電路里,利用次臨限傳導的金氧半場效電晶體來達成目的的設計也頗為常見。

傳統上,互補式金屬氧化物半導體邏輯門的切換速度與其組件的柵極電容有關。但是當柵極電容隨著金氧半場效電晶體尺寸變小而減少,同樣大小的晶片上可容納更多電晶體時,連線這些電晶體的金屬導線間產生的寄生電容效應就開始主宰邏輯門的切換速度。如何減少這些寄生電容,成了晶片效率能否向上突破的關鍵之一。

當晶片上的電晶體數量大幅增加後,有一個無法避免的問題也跟著發生了,那就是晶片的發熱量也大幅增加。一般的

積體電路組件在高溫下工作可能會導致切換速度受到影響,或是導致可靠度與壽命的問題。在一些發熱量非常高的

積體電路晶片如

微處理器,目前需要使用外加的散熱系統來緩和這個問題。

在功率電晶體(Power金氧半場效電晶體)的領域裡,溝道電阻常常會因為溫度升高而跟著增加,這樣也使得在組件中

PN結(pn-junction)導致的功率損耗增加。假設外置的散熱系統無法讓功率電晶體的溫度保持在夠低的水準,很有可能讓這些功率電晶體遭到

熱失控的命運。

柵極氧化層隨著金氧半場效電晶體尺寸變小而越來越薄,目前主流的半導體工藝中,甚至已經做出厚度僅有1.2

奈米的柵極氧化層,大約等於5個原子疊在一起的厚度而已。在這種尺度下,所有的物理現象都在

量子力學所規範的世界內,例如電子的

穿隧效應。因為穿隧效應,有些電子有機會越過氧化層所形成的位能障壁(potential barrier)而產生漏電流,這也是今日

積體電路晶片功耗的來源之一。

為了解決這個問題,有一些介電係數比

二氧化矽更高的物質被用在柵極氧化層中。例如

鉿和

鋯的金屬氧化物(二氧化鉿、二氧化鋯)等高介電係數的物質均能有效降低柵極漏電流。柵極氧化層的介電係數增加後,柵極的厚度便能增加而維持一樣的電容大小。而較厚的柵極氧化層又可以降低電子通過穿隧效應穿過氧化層的機率,進而降低漏電流。不過利用新材料製作的柵極氧化層也必須考慮其位能障壁的高度,因為這些新材料的

傳導帶和

價帶和半導體的傳導帶與價帶的差距比

二氧化矽小(二氧化矽的傳導帶和矽之間的高度差約為8

ev),所以仍然有可能導致柵極漏電流出現。

現代的半導體工藝工序複雜而繁多,任何一道工藝都有可能造成積體電路晶片上的組件產生些微變異。當金氧半場效電晶體等組件越做越小,這些變異所占的比例就可能大幅提升,進而影響電路設計者所預期的性能,這樣的變異讓電路設計者的工作變得更為困難。

柵極材料

理論上金氧半場效電晶體的柵極應該儘可能選擇電性良好的導體,

多晶矽在經過重摻雜之後的導電性可以用在金氧半場效電晶體的柵極上,但是並非完美的選擇。目前金氧半場效電晶體使用

多晶矽作為的理由如下:

金氧半場效電晶體的臨界電壓(threshold voltage)主要由柵極與溝道材料的

功函式之間的差異來決定,而因為多晶矽本質上是

半導體,所以可以藉由摻雜不同極性的雜質來改變其功函式。更重要的是,因為

多晶矽和底下作為溝道的

矽之間能隙相同,因此在降低PMOS或是NMOS的臨界電壓時可以藉由直接調整

多晶矽的功函式來達成需求。反過來說,金屬材料的功函式並不像半導體那么易於改變,如此一來要降低金氧半場效電晶體的臨界電壓就變得比較困難。而且如果想要同時降低PMOS和NMOS的臨界電壓,將需要兩種不同的金屬分別做其柵極材料,對於工藝又是一個很大的變數。

矽—

二氧化矽接面經過多年的研究,已經證實這兩種材料之間的缺陷(defect)是相對而言比較少的。反之,金屬—絕緣體接面的缺陷多,容易在兩者之間形成很多表面能階,大為影響組件的特性。

多晶矽的熔點比大多數的金屬高,而在現代的半導體工藝中習慣在高溫下沉積柵極材料以增進組件性能。金屬的熔點低,將會影響工藝所能使用的溫度上限。

不過多晶矽雖然在過去20年是製造金氧半場效電晶體柵極的標準,但也有若干缺點使得未來仍然有部分金氧半場效電晶體可能使用金屬柵極,這些缺點如下:

多晶矽導電性不如金屬,限制了信號傳遞的速度。雖然可以利用摻雜的方式改善其導電性,但成效仍然有限。目前有些融點比較高的金屬材料如:

鎢、

鈦、

鈷或是

鎳被用來和

多晶矽製成合金。這類混合材料通常稱為

金屬矽化物。加上了金屬矽化物的多晶矽柵極有著比較好的導電特性,而且又能夠耐受高溫工藝。此外因為金屬矽化物的位置是在柵極表面,離溝道區較遠,所以也不會對金氧半場效電晶體的臨界電壓造成太大影響。

在柵極、源極與漏極都鍍上金屬矽化物的工藝稱為自我對準金屬矽化物工藝(Self-Aligned Silicide),通常簡稱salicide工藝。

當金氧半場效電晶體的尺寸縮的非常小、柵極氧化層也變得非常薄時,例如現在的工藝可以把氧化層縮到一

奈米左右的厚度,一種過去沒有發現的現象也隨之產生,這種現象稱為多晶矽耗盡。當金氧半場效電晶體的反轉層形成時,有多晶矽耗盡現象的金氧半場效電晶體柵極多晶矽靠近氧化層處,會出現一個耗盡層(depletion layer),影響金氧半場效電晶體導通的特性。要解決這種問題,金屬柵極是最好的方案。目前可行的材料包括

鉭、

鎢、

氮化鉭(Tantalum Nitride),或是

氮化鈦(Titanium Nitride)。這些金屬柵極通常和高介電係數物質形成的氧化層一起構成MOS電容。另外一種解決方案是將多晶矽完全的合金化,稱為FUSI(FUlly-SIlicide polysilicon gate)工藝。

電晶體技術

雙柵極金氧

雙柵極(dual-gate)金氧半場效電晶體通常用在

射頻積體電路中,這種金氧半場效電晶體的兩個柵極都可以控制電流大小。在射頻電路的套用上,雙柵極金氧半場效電晶體的第二個柵極大多數用來做增益、混頻器或是頻率轉換的控制。

耗盡式

一般而言,耗盡式(depletion mode)金氧半場效電晶體比前述的加強式(enhancement mode)金氧半場效電晶體少見。耗盡式金氧半場效電晶體在製造過程中改變摻雜到溝道的雜質濃度,使得這種金氧半場效電晶體的柵極就算沒有加電壓,溝道仍然存在。如果想要關閉溝道,則必須在柵極施加負電壓(對NMOS而言)。耗盡式金氧半場效電晶體是屬於“常閉型”(normally-closed,ON)的開關,而相對的,加強式金氧半場效電晶體則屬於“常斷型”(normally-open,OFF)的開關。

NMOS邏輯

同樣驅動能力的NMOS通常比PMOS所占用的面積小,因此如果只在邏輯門的設計上使用NMOS的話也能縮小晶片面積。不過NMOS邏輯雖然占的面積小,卻無法像CMOS邏輯一樣做到不消耗靜態功率,因此在1980年代中期後已經漸漸退出市場,目前以CMOS為主流。

功率金氧

功率電晶體單元的截面圖。通常一個市售的功率電晶體都包含了數千個這樣的單元。

主條目:功率金氧半場效電晶體

功率金氧半場效電晶體(Power MOSFET)和前述的金氧半場效電晶體組件在結構上就有著顯著的差異。一般

積體電路里的金氧半場效電晶體都是平面式(planar)的結構,電晶體內的各端點都離晶片表面只有幾個

微米的距離。而所有的功率組件都是垂直式(vertical)的結構,讓組件可以同時承受高電壓與高電流的工作環境。一個功率金氧半場效電晶體能耐受的電壓是雜質摻雜濃度與n-type外延層(epitaxial layer)厚度的函式,而能通過的電流則和組件的溝道寬度有關,溝道越寬則能容納越多電流。對於一個平面結構的金氧半場效電晶體而言,能承受的電流以及擊穿電壓的多寡都和其溝道的長寬大小有關。對垂直結構的金氧半場效電晶體來說,組件的面積和其能容納的電流大約成正比,外延層厚度則和其擊穿電壓成正比。

值得一提的是採用平面式結構的功率金氧半場效電晶體也並非不存在,這類組件主要用在高級的音響放大器中。平面式的功率金氧半場效電晶體在飽和區的特性比垂直結構的對手更好。垂直式功率金氧半場效電晶體則多半用來做開關切換之用,取其導通電阻(turn-on resistance)非常小的優點。

DMOS

DMOS是雙重擴散金氧半場效電晶體(Double-Diffused金氧半場效電晶體)的縮寫,大部分的功率金氧半場效電晶體都是採用這種製作方式完成的。

模擬開關

金氧半場效電晶體在導通時的溝道電阻低,而截止時的電阻近乎無限大,所以適合作為模擬信號的開關(信號的能量不會因為開關的電阻而損失太多)。金氧半場效電晶體作為開關時,其源極與漏極的分別和其他的套用是不太相同的,因為信號可以從金氧半場效電晶體柵極以外的任一端進出。對NMOS開關而言,電壓最負的一端就是源極,PMOS則正好相反,電壓最正的一端是源極。金氧半場效電晶體開關能傳輸的信號會受到其柵極—源極、柵極—漏極,以及漏極到源極的電壓限制,如果超過了電壓的上限可能會導致金氧半場效電晶體燒毀。

金氧半場效電晶體開關的套用範圍很廣,舉凡需要用到採樣持有電路(sample-and-hold circuits)或是截波電路(chopper circuits)的設計,例如模擬數字轉換器(A/D converter)或是切換電容濾波器(switch-capacitor filter)上都可以見到金氧半場效電晶體開關的蹤影。

單一開關

當NMOS用來做開關時,其源極接地,柵極為控制開關的端點。當柵極電壓減去源極電壓超過其導通的臨界電壓時,此開關的狀態為導通。柵極電壓繼續升高,則NMOS能通過的電流就更大。NMOS做開關時工作線上性區,因為源極與漏極的電壓在開關為導通時會趨向一致。

PMOS做開關時,其源極接至電路里電位最高的地方,通常是電源。柵極的電壓比源極低、超過其臨界電壓時,PMOS開關會打開。

NMOS開關能容許通過的電壓上限為(Vgate-Vthn),而PMOS開關則為(Vgate+Vthp),這個值通常不是信號原本的電壓振幅,也就是說單一金氧半場效電晶體開關會有讓信號振幅變小、信號有損的缺點。

雙重開關

為了改善前述單一金氧半場效電晶體開關造成信號有損的缺點,於是使用一個PMOS加上一個NMOS的CMOS開關(Transmission gate)成為目前最普遍的做法。CMOS開關將PMOS與NMOS的源極與漏極分別連線在一起,而基極的接法則和NMOS與PMOS的傳統接法相同(PMOS的基極接到最高電壓,即VDD;NMOS的基極接到最低電壓,即VSS或GND)。要令開關導通時,則把PMOS的柵極接低電位(VSS或GND),NMOS的柵極接高電位(VDD)。當輸入電壓在(VDD-Vthn)到(VSS+Vthp)時,PMOS與NMOS都導通,而輸入小於(VSS+Vthp)時,只有NMOS導通,輸入大於(VDD-Vthn)時只有PMOS導通,這樣做的好處是在大部分的輸入電壓下,PMOS與NMOS皆同時導通,如果任一邊的導通電阻上升,則另一邊的導通電阻就會下降,所以開關的電阻幾乎可以保持定值,減少信號有損。