基本介紹

- 中文名:可程式序邏輯陣列

- 外文名:Programmable Logic Array

- 簡稱:PLA

- 特點:結構規整、使用靈活等

- 組成:與、或陣列

- 套用:實現組合電路、時序電路

PLA的結構原理

PLA的故障類型

編程式的方法

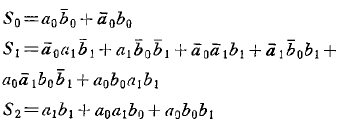

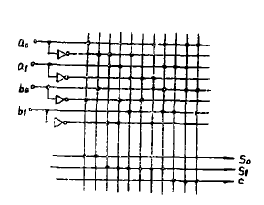

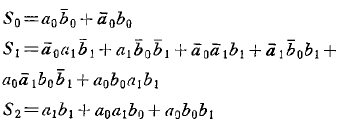

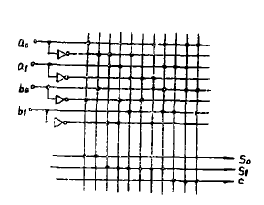

用PLA實現組合電路

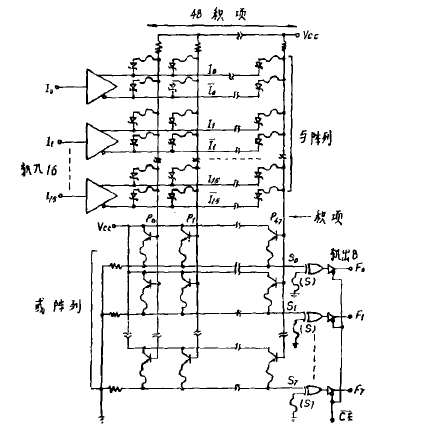

可程式序邏輯陣列(Programmable Logic Array),簡稱PLA,是可程式邏輯器件的一種,它是與、或陣列均可程式的、包含有記憶元件的大規規模積體電路,它能實現任意邏輯函式的組合電路以及實現時序電路。PLA...

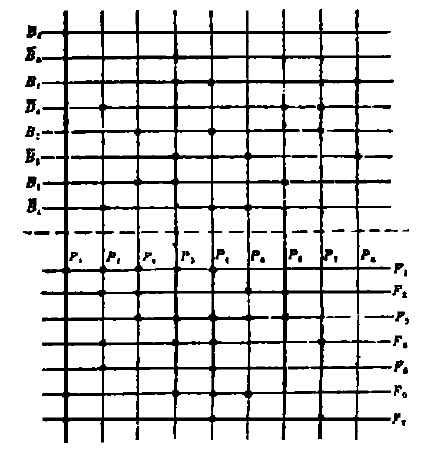

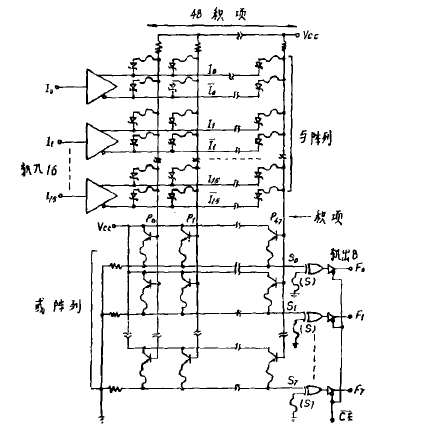

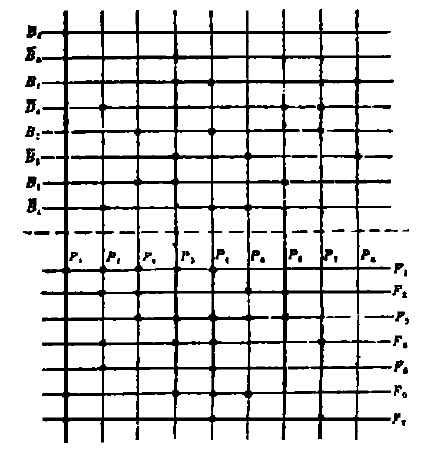

可程式邏輯陣列簡稱PLA,是一種可程式化的裝置,可用來實現組合邏輯電路。PLA具有一組可程式化的AND階,AND階之後連線一組可程式化的OR階,如此可以達到:只在合乎設定條件時才允許產生邏輯訊號輸出。原理 PLA如此的邏輯閘布局能用來規劃...

可程式陣列邏輯,英語縮寫PAL(programmable array logic)。由可程式的與陣列、固定的或陣列和輸出反饋單元組成的一種可程式邏輯器件。PAL器件由可程式的與陣列、固定的或陣列和輸出反饋單元組成。不同型號有不同的輸出和反饋結構,適用於...

FPGA是“可程式化邏輯門陣列”英文縮寫。是一個含有可編輯元件的半導體設備,可供使用者現場程式化的邏輯門陣列元件。“可程式化邏輯門陣列”又稱“元件可程式邏輯門陣列”。概要 目前以硬體描述語言(Verilog或VHDL)所完成的電路設計,...

與邏輯陣列作為輸入矩陣,接收輸入信號;或邏輯陣列作為輸出矩陣,傳送輸出信號。存儲在兩個矩陣中的程式或信息,可以通過掩模設計來編制,也可以使用可程式唯讀存儲器(PROM)一次寫入。只要能列出問題的真值表或邏輯函式,就能設計出相應的...

可程式陣列邏輯電路(programmable array logic)是2018年全國科學技術名詞審定委員會公布的計算機科學技術名詞。定義 由可程式的與門陣列連線固定不可程式的或門陣列構成的可程式邏輯陣列。出處 《計算機科學技術名詞 》第三版 ...

通用陣列邏輯,英語縮寫GAL(genericarray logic)。在可程式陣列邏輯的基礎上強化修改而成的一種可程式邏輯器件。編程非常方便,且具有電可擦除功能,能多次編程、多次擦除。採用了輸出邏輯宏單元的設計,使得電路的邏輯設計更加靈活。定義...

現場可程式門陣列是一種程式驅動邏輯器件, 就像一個微處理器, 其控制程式存儲在記憶體中, 加電後,程式自動裝載到晶片執行。 現場可程式門陣列一般由2 個可程式模組和存儲SRAM構成。CLB是可程式邏輯塊,是現場可程式門陣列的核心組成...

(程式)稱為“邏輯編譯器,logic compiler”,它與程式開發撰寫時所用的軟體編譯器相類似,而要編譯之前的原始代碼(也稱:原始碼)也得用特定的編程語言(也稱:程式語言、程式語言)來撰寫,此稱之為hardware description language(硬體描述語言)...

《可程式偏振編碼光並行陣列邏輯門研究》是依託浙江大學,由余飛鴻擔任項目負責人的青年科學基金項目。項目摘要 完整地用BPLA理論表示了兩輸入數陣列16種邏輯運算,並擴展到三輸入邏輯門,最後用BPLA理論進行兩輸入邏輯門的期望設計及可程式...

對於非標準的特殊電路還可以使用可程式序邏輯陣列電路,通過編程的方法實現任意的邏輯功能。套用 數字電路與數字電子技術廣泛的套用於電視、雷達、通信、電子計算機、自動控制、航天等科學技術領域。數字電路的分類:包括數字脈衝電路和數字邏輯...

3.3 在系統可程式邏輯器件套用設計 3.3.1 可預置十進制減法計數器 3.3.2 脈衝分配器 3.3.3 序列信號發生器 3.3.4 簡易周期信號測試儀 第四章 VHDL程式設計及套用 4.1 VHDL語言 4.1.1 VHDL的程式結構 4.1.2 VHDL的...

將PCA0MD 中ECF 位設定為邏輯1 即可允許CF 標誌產生中斷請求。當CPU 轉向中斷服務程式時,CF 位不能被硬體自動清除,必須用軟體清0。(注意:要使CF 中斷得到回響,必須先總體允許PCA0 中斷)。通過將EA 位(IE.7 )和EPCA0 (...

該書是計算機科學、計算機工程和電氣工程等專業的學生學習邏輯設計的入門教程。學習本教程不需要任何先決條件,雖然先學習一門工程導論課或者初級程式設計課會有所幫助。本書強調基礎知識。通過大量實例進行講授。作者認為,學習邏輯設計的惟一...

4.3 兩種常用的HDPLD可程式邏輯器件 164 4.3.1 按集成度分類的可程式邏輯器件 164 4.3.2 CPLD可程式器件 165 4.3.3 FPGA可程式器件 169 習題 173 第5章 VHDL基礎 175 5.1 VHDL簡介 175 5.2 VHDL程式結構 ...

4 電平異步時序電路的設計 8.5 邏輯電路的競爭與險象 第九章 可程式序邏輯器件PLD 9.1 可程式序邏輯器件PLD電路表示法 9.2 可程式唯讀存儲器RPOM 9.3 可程式邏輯陣列PLA 9.4 可程式陣列邏輯PAL 9.5 通用陣列邏輯GAL 習題 ...

FPGA設計的主要難點是熟悉硬體系統以及內部資源,保證設計的語言能夠實現元器件之間的有效配合,提高程式的可讀性以及利用率。這也對設計人員提出了比較高的要求,需要經過多個項目的經驗積累才可以達到相關的要求。在算法設計時需要重點考慮...

二、利用邏輯門設計典型組合邏輯電路 79 §4-3中大規模標準組合模組電路 84 一、二進制解碼器 84 二、二進制編碼器 86 三、數據選擇器 88 四、數據分配器 90 五、移位器 91 六、唯讀存儲器(ROMS) 92 七、可程式序邏輯陣列(...

2.2 時序邏輯電路19 2.2.1 觸發器19 2.2.2 暫存器和移位暫存器21 2.2.3 計數器21 2.3 陣列邏輯電路22 2.3.1 唯讀存儲器(ROM)23 2.3.2 可程式序邏輯陣列(PLA)24 2.3.3 可程式序陣列邏輯(PAL)26 2.3.4 通用...

利用已有的可程式序邏輯陣列 (PLA)電路也可改制為所需的定製積體電路。由於可程式序邏輯陣列電路的掩模版是可程式序的,定製這類積體電路時,只須按要求改變一塊連線線的掩模版,再進行後步工序加工即可。此項工作也可藉助於計算機輔助...

2.使用控制邏輯的實現技術(使用CAD工具等)來實現其他組成部分.CPU架構設計的邏輯 在CPU設計中包括的一般邏輯為:1.非結構化的隨機邏輯 2.有限狀態機 3.微程式設計(常見於1965年到1985年)4.可程式邏輯陣列(常見於80年代,比較罕見)...

有時工程師會使用某些腳本語言(如Perl、Tcl)來編寫驗證程式,藉助電腦程式的高速處理來實現更大的測試覆蓋率。現代的硬體驗證語言可以提供一些專門針對驗證的特性,例如帶有約束的隨機化變數、覆蓋等等。作為硬體設計、驗證統一語言,System...

7.4組合邏輯控制器179 7.4.1組合邏輯控制器的特徵179 *7.4.2組合邏輯控制器設計原理179 *7.4.3可程式序邏輯陣列控制器183 7.5微程式控制器184 7.5.1微程式設計的基本原理184 7.5.2微指令方案187 *7.5.3微程式設計的...

本書內容自成體系,因而只需具備計算機高級語言程式設計的基礎知識即可閱讀。在選材廣度上包括計算機信息和數字邏輯的基礎知識,在深度上則為學生進一步學習和將來從事計算機專職工作打下堅實基礎。寫作一本“計算機組織”教材的難點之一是關於...

2.1.4算術邏輯單元30 2.1.5解碼器34 2.1.6數據選擇器35 2.2時序邏輯電路36 2.2.1觸發器36 2.2.2暫存器和移位暫存器39 2.2.3計數器41 2.3陣列邏輯電路43 2.3.1隻讀存儲器(ROM)43 2.3.2可程式序邏輯陣列(PLA)45 ...

6.3.1 Testbench 程式基本結構 103 6.3.2 激勵信號的產生 104 6.3.3 VHDL Testbench 測試基準實例111 本章小結 119 習題119 第7 章 EDA 軟體介紹120 7.1 Multisim12.0 軟體介紹120 7.1.1 Multisim12.0 軟體基本界面121 ...

但是,FPGA具有很多優點,比如可以快速成品,而且其內部邏輯可以被設計者反覆修改,從而改正程式中的錯誤,此外,使用FPGA進行除錯的成本較低。廠商也可能會提供便宜、但是編輯能力有限的FPGA產品。因為這些晶片有的可編輯能力較差,所以這些...

7.3.6 RISC SPM: 程式執行 7.4 設計實例: UART 7.4.1 UART的操作 7.4.2 UART傳送器 7.4.3 UART接收器 參考文獻 習題 第8章 可程式邏輯及存儲器件 8.1 可程式邏輯器件 8.2 存儲器件 8.2.1 唯讀存儲器 8.2.2 ...

4.9測試程式135 4.10總結138 習題138 面試問題145 第5章數字模組146 5.1引言146 5.2算術電路146 5.2.1加法146 5.2.2減法151 5.2.3比較器152 5.2.4算術邏輯單元153 5.2.5移位器和循環移位器154 5.2.6乘法*155 5.2...