可程式邏輯陣列法 (programmable logic array) 是對製造廠家提供的可程式的與邏輯陣列和或邏輯陣列兩部分構成的電路晶片,由設計者根據所需功能把它們連線起來實現特定邏輯的一種半定製設計方法,簡稱PLA。用PLA可實現組合邏輯電路和時序邏輯電路。

基本介紹

- 中文名:可程式邏輯陣列法

- 外文名:programmable logic array

- 簡稱:PLA

基本構成

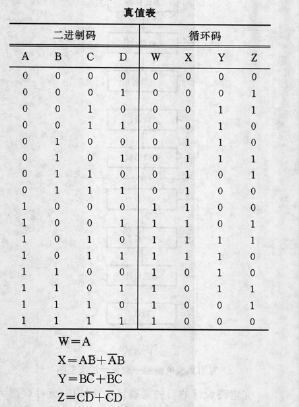

表

表 原理圖

原理圖可程式邏輯陣列法 (programmable logic array) 是對製造廠家提供的可程式的與邏輯陣列和或邏輯陣列兩部分構成的電路晶片,由設計者根據所需功能把它們連線起來實現特定邏輯的一種半定製設計方法,簡稱PLA。用PLA可實現組合邏輯電路和時序邏輯電路。

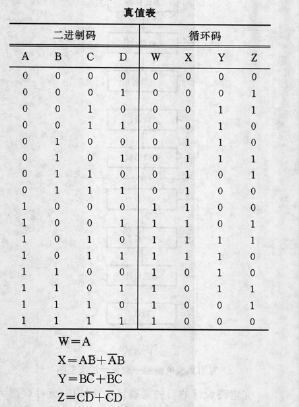

表

表 原理圖

原理圖可程式邏輯陣列法 (programmable logic array) 是對製造廠家提供的可程式的與邏輯陣列和或邏輯陣列兩部分構成的電路晶片,由設計者根據所需功能把它們連線起來實現特定...

可程式陣列邏輯,英語縮寫PAL(programmable array logic)。由可程式的與陣列、固定的或陣列和輸出反饋單元組成的一種可程式邏輯器件。PAL器件由可程式的與陣列、固定...

可程式邏輯陣列簡稱PLA,是一種可程式化的裝置,可用來實現組合邏輯電路。PLA具有一組可程式化的AND階,AND階之後連線一組可程式化的OR階,如此可以達到:只在合乎...

現場可程式邏輯陣列(FPGA)是可以反覆地編程、擦除、使用以及在外圍電路不動的情況下用不同軟體就可實現不同功能的一種門陣列晶片,可以在一定程度上靈活地擴展業務...

可程式序邏輯陣列(Programmable Logic Array),簡稱PLA,是可程式邏輯器件的一種,它是與、或陣列均可程式的、包含有記憶元件的大規規模積體電路,它能實現任意邏輯...

PAL(Programmable Array Logic)可程式陣列邏輯,是70年代末由MMI公司率先推出的一種低密度,一次性可程式邏輯器件,第一個具有典型實際意義的可程式邏輯器件(PLD-...

Programmable logic arrays(PLA) 是一種可程式邏輯裝置,它的與陣列(AND array)和或陣列(OR array)均為可程式,輸出電路為不可組態.又叫做FPLA(field-programmable ...

可程式邏輯器件 英文全稱為:programmable logic device 即 PLD。PLD是做為一種通用積體電路產生的,他的邏輯功能按照用戶對器件編程來確定。一般的PLD的集成度很高,...

通用陣列邏輯,英語縮寫GAL(genericarray logic)。在可程式陣列邏輯的基礎上強化修改而成的一種可程式邏輯器件。編程非常方便,且具有電可擦除功能,能多次編程、多次...

《可程式邏輯設計技術及套用》是人民郵電出版社2004年7月1日出版的圖書。...... 1.4 可程式通用陣列邏輯GAL1.4.1 GAL器件的基本結構1.4.2 GAL器件的控制字...

CPLD採用CMOS EPROM、EEPROM、快閃記憶體和SRAM等編程技術,從而構成了高密度、高速度和低功耗的可程式邏輯器件。...

本書主要介紹計算機邏輯分析和設計的基本理論和方法,包括開關理論基礎、邏輯器件、...2.8.1 可程式邏輯陣列(PLA) 572.8.2 可程式陣列邏輯 (PAL) 59...

現代生物醫學儀器正在向著微型化、多功能化、系列化等方向發展 ,系統中的數字部分越來越重要。現場可程式門陣 列是一種新型可程式邏輯器件, 性能優良,套用於生物...

可程式中控系統採用32位內嵌式處理器,最高主頻可達257MHZ,8M的SDRAM記憶體空間,8M的存儲FLASH,可以高速運算複雜的邏輯指令,其內置強大的可程式接口;可任意編程,適用於...

FPLA(Field Programmable Logic Array) 現場可程式邏輯陣列是可程式邏輯器件(PLD)的一種,是一種半導體器件含有可程式邏輯元件的所謂“邏輯塊” ,和可程式互連。 ...