CPU 設計是指設計中央處理器(CPU)的工程學,是計算機硬體(設計)的一部分,它是計算機工程和電氣工程中的一個分支。

基本介紹

- 中文名:CPU架構設計

- 外文名:CPU architecture design

- 學科:計算機硬體設計

細節

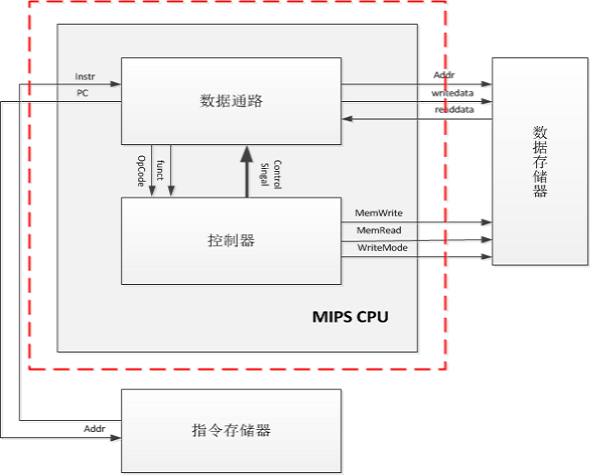

- 數據路徑(如ALU和計算管道)

- 控制單元:邏輯控制的數據路徑

- 記憶體元件,如暫存器檔案快取

- 時脈電路,如時脈驅動器,PLL,時鐘分配網路

- 墊收發器電路

- 邏輯門電路的實現

CPU 設計是指設計中央處理器(CPU)的工程學,是計算機硬體(設計)的一部分,它是計算機工程和電氣工程中的一個分支。

CPU 設計是指設計中央處理器(CPU)的工程學,是計算機硬體(設計)的一部分,它是計算機工程和電氣工程中的一個分支。細節CPU設計關注數據路徑(如ALU和計算管道)控制單元:邏輯控制的數據路徑記憶體元件,如暫存器檔案緩...

(Von Neumann architecture),也稱普林斯頓結構,是一種將程式指令存儲器和數據存儲器合併在一起的電腦設計概念結構。圖1是馮·諾伊曼結構圖:本結構隱約指導了將儲存裝置與中央處理器分開的概念,因此依本結構設計出的計算機又稱儲存程式...

相較於英特爾在2010年進入新製程,AMD則是要到2011年開始進入32納米製程,屆時將採用新的Bulldozer核心架構設計,包括效能級12至16核心的Interlagos,以及強調能源效益6至8核心的Valencia。8核心的CPU 現在不可能對應現在的主機板所以不可能大張...

ARM架構,曾稱進階精簡指令集機器(Advanced RISC Machine)更早稱作Acorn RISC Machine,是一個32位精簡指令集(RISC)處理器架構。還有基於ARM設計的派生產品,重要產品包括Marvell的XScale架構和德州儀器的OMAP系列。ARM家族占比所有32位...

多核心處理器架構是指晶片設計工程師在單個處理器中集成兩個或多個基於英特爾奔騰處理器的“執行核心(即計算引擎)”。多核心處理器可直接插入到單一處理器基座中。但是,作業系統會把它的每個執行核心作為獨立的邏輯處理器,為其分配相應...

毫無疑問,英特爾的這一創舉將是在處理器核心架構設計上具有里程碑意義的。2.全新的整數與浮點單元 從P6到NetBurst架構,整數與浮點單元的變化還是相當明顯,不過Core微架構的變化也同樣不小,只是部分關鍵技術又改回P6架構時代的設計。

Core微架構是由Intel位於以色列海法的研發團隊負責設計的。該以色列團隊早在2003年就因為設計出兼具高性能與低功耗的 Banias 處理器而聞名天下,Core 微架構也是他們在 Yonah 微架構之後的最新傑作。Core 微架構很早就出現在 Intel 的計畫...

對英特爾而言, IA-64(英特爾的64位架構)是下一個10到15年的架構。新的ISA將使英特爾擺脫X86架構的限制,從而設計出超越所有現有RISC CPU和X86 CPU的新型處理器。那么EPIC的先進之處在什麼地方呢?為什麼英特爾會放棄使它成為晶片巨人...

加州大學伯克利分校的計算機科學教授David Patterson說:“認識到x86體系架構並非一種凝固的設計這一點很重要。30多年來,它們每月都會增加一個說明。現在x86指令集的說明已經達到500多個。每一代都會增加20到100多個。前後兼容很重要,它也...

改進設計 “Zen”處理器核心在架構上有諸多先進設計,旨在提高AMD未來產品的性能、吞吐能力和能效。處理器主要架構改進如下:·SMT多執行緒,每個核心可支持2個執行緒 ·8MB L3快取 ·容量更大、更統一的L2快取 ·微操作快取(Micro-op ...

Core微架構是Intel全平台(台式機、筆記本和伺服器)處理器首次採用相同的微架構設計,也是Intel鑒於NetBurst微架構的高頻低效高能耗的缺點,徹底拋棄以往頻率至上的理念,轉而注重能效比的第一次成功嘗試。無數的評測已經證明,Core微架構...

1981年,史丹福大學教授約翰·軒尼詩領導他的團隊,實作出第一個MIPS架構的處理器。他們原始的想法是通過指令管線化來增加CPU運算的速度。1984年,約翰·軒尼詩教授離開史丹福大學,創立MIPS科技公司。於1985年,設計出R2000晶片,1988年,將...

CPU出現於大規模積體電路時代,處理器架構設計的疊代更新以及積體電路工藝的不斷提升促使其不斷發展完善。從最初專用於數學計算到廣泛套用於通用計算,從4位到8位、16位、32位處理器,最後到64位處理器,從各廠商互不兼容到不同指令集...

(3)PA-RISC處理器 (4)MIPS處理器 (5)Alpha處理器 VLIW型處理器 VLIW是英文“Very Long Instruction Word”的縮寫,中文意思是“超長指令集架構”,VLIW架構採用了先進的EPIC(清晰並行指令)設計,我們也把這種構架叫做“IA-64架構”...

可擴充處理器結構(SPARC,Scalable Processor Architecture)是RISC微處理器架構之一。它最早於1987年由Sun電腦所設計,也是SPARC國際公司的註冊商標之一。可擴展處理器結構是Sun Microsystems的一種32位及64位微處理器結構,它基於精簡指令集...

微架構又稱為微體系結構/微處理器體系結構。是在計算機工程中,將一種給定的 指令集架構在處理器中執行的方法。一種給定指令集可以在不同的微架構中執行。實施中可能因應不同的設計目的和技術提升而有所不同。計算機架構是微架構和指令...

中央處理器存儲器又叫CPU存儲器,CPU存儲器是微處理器中存放數據和各種程式的裝置。CPU存儲器是微處理器的一個重要的組成部分,由存儲單元集合體,地址暫存器,解碼驅動電路,讀出放大器以及時序控制電路等幾部分組成。基本概念 中央處理器...

世界上具有嵌入式功能特點的處理器已經超過1000種,流行體系結構包括MCU,MPU等30多個系列。鑒於嵌入式系統廣闊的發展前景,很多半導體製造商都大規模生產嵌入式處理器,並且公司自主設計處理器也已經成為了未來嵌入式領域的一大趨勢,其中從...

中央處理器(CPU,Central Processing Unit)是一塊超大規模的積體電路,是一台計算機的運算核心(Core)和控制核心( Control Unit)。它的功能主要是解釋計算機指令以及處理計算機軟體中的數據。CPU從邏輯上可以劃分成3個模組,分別是控制...

AMD64指令集被套用在Athlon 64、Athlon 64 FX、Athlon 64 X2、Turion 64、Turion 64 X2、Opteron及較新款的Sempron、Phenom、AMD APU、AMD Ryzen等處理器上。架構特色 在x86-64出現以前,英特爾與惠普聯合設計出IA-64架構;惟IA-64...

英特爾酷睿微體系結構,是一款領先節能的新型微架構,設計的出發點是提供卓然出眾的性能和能效,提高每瓦特性能,也就是所謂的能效比。英特爾酷睿微體系結構面向伺服器、台式機和筆記本電腦等多種處理器進行了多核最佳化,其創新特性可帶來更...

IA-64架構是EPIC(Explicitly Parallel Instruction Computing,顯式並行指令運算)的64位架構。EPIC是基於超長指令字VLIW(Very Long Instruction Word)的設計,通過將多條指令放入一個指令字,有效的提高了CPU各個計算功能部件的利用效率,...

換言之,Sandy Bridge、Ivy Bridge只是這種進化中的頭兩個基礎性步驟,Haswell將成為“新的最佳化點”,使用新架構推動Ultrabook概念的普及。在筆記本中,35W熱設計功耗是移動處理器的一個標準,但是後年的Haswell會將這個數值降低50%以上,...

許多現代的處理器具有多個指令解碼器,每一個都有自己的流水線。這樣便存在多個指令流,也就是說每個時鐘周期可以完成多條指令。但是這種技術實現起來非常複雜,因此需要使用大量的電晶體。處理器設計的發展趨勢主要是:完全32位的ALU(內置...

所以,ARM11核心在運行於極高頻率的同時,也能非常容易的被集成在SoC設計中。同時,ARM11處理器提供的向上兼容性,使OEM可以放心的選用任何基於ARM的產品。發展演變 ARM11處理器是ARMv6架構的第一代實現,ARM的合作夥伴可以從不同的方面...

另外,x86處理器製造廠商AMD也在該公司最新K10架構的Phenom處理器中,加入4條新的SSE4A指令集。注意,SSE4與SSE4A無法彼此兼容。64位架構 到2002年,由於32位特性的長度,x86的架構開始到達某些設計的極限。這個導致要處理大量的信息儲存...