發展簡介

主存儲器一般採用半導體存儲器,與輔助存儲器相比有容量小、讀寫速度快、價格高等特點。計算機中的主存儲器主要由存儲體、控制線路、地址暫存器、數據暫存器和地址解碼電路五部分組成。

從70年代起,主

存儲器已逐步採用

大規模積體電路構成。用得最普遍的也是最經濟的動態

隨機存儲器晶片(DRAM)。1995年集成度為64Mb(可

存儲400萬個漢字)的DRAM晶片已經開始商業性生產,16MbDRAM晶片已成為市場主流產品。DRAM晶片的存取速度適中,一般為50~70ns。有一些改進型的DRAM,如EDO DRAM(即擴充

數據輸出的DRAM),其性能可較普通DRAM提高10%以上,又如SDRAM(即同步DRAM),其性能又可較EDO DRAM提高10%左右。1998年SDRAM的後繼產品為SDRAMⅡ(或稱DDR,即雙倍數據速率)的品種已上市。在追求速度和可靠性的場合,通常採用價格較貴的

靜態隨機存儲器晶片(SRAM),其存取速度可以達到了1~15ns。無論主存採用DRAM還是SRAM晶片構成,在斷電時

存儲的信息都會“丟失”,因此

計算機設計者應考慮發生這種情況時,設法維持若干毫秒的供電以保存主存中的重要信息,以便供電恢復時計算機能恢復正常運行。鑒於上述情況,在某些套用中主存中

存儲重要而相對固定的程式和數據的部分採用“非易失性”

存儲器晶片(如EPROM,快閃

存儲晶片等)構成;對於完全固定的程式,數據區域甚至採用

唯讀存儲器(ROM)晶片構成;主存的這些部分就不怕暫時供電中斷,還可以防止病毒侵入。

技術指標

指標含義表現單位

存取時間啟動到完成一次

存儲器操作所經歷的時間 主存的速度 ns

存儲周期連續啟動兩次操作所需間隔的最小時間 主存的速度 ns

存儲器頻寬單位時間裡存儲器所存取的信息量, 它是衡量

數據傳輸速率的重要技術指標,單位是b∕s( 位/秒)或B∕S(位元組/秒)。

位是

位元組,則該計算機稱為按位元組編址的計算機。一個機器字可以包含數個位元組,所以一個

存儲單元也可以包含數個能夠單獨編址的位元組地址。例如,

PDP-11系列

計算機,一個16位

二進制的字

存儲單元可存放兩個位元組,可以按字地址定址,也可以按位元組地址定址。當用位元組地址定址時,16位的

存儲單元占兩個位元組地址。

電鍍金工藝的記憶體金手指

電鍍金工藝的記憶體金手指容量

在一個

存儲器中容納的

存儲單元總數通常稱為該存儲器的存儲容量。

存儲容量用字數或位元組數(B)來表示,如64K字,512KB,10MB。外存中為了表示更大的存儲容量,採用

MB,GB,TB等單位。其中1KB=2^10B,1MB=2^20B,1GB=2^30B,1TB=2^40B。B表示

位元組,一個位元組定義為8個

二進制位,所以

計算機中一個字的

字長通常為8的倍數。

存儲容量這一概念反映了

存儲空間的大小。

時間

又稱

存儲器訪問時間或讀∕寫時間,是指從啟動一次存儲器操作到完成該操作所經歷的時間。具體講,從一次讀操作

命令發出到該操作完成,將數據讀入

數據緩衝暫存器為止所經歷的時間,即為

存儲器存取時間。

周期

是指連續啟動兩次獨立的

存儲器操作(如連續兩次讀操作)所需間隔的最小時間。通常,存儲周期略大於存儲時間,其時間單位為ns

產品分類

RAM是構成記憶體的主要部分,其內容可以根據需要隨時按地址讀出或寫入,以某種電觸發器的狀態存儲,斷電後信息無法保存,用於暫存數據,又可分為DRAM和SRAM兩種。RAM一般使用動態半導體存儲器件(DRAM)。因為CPU工作的速度比RAM的讀寫速度快,所以CPU讀寫RAM時需要花費時間等待,這樣就使CPU的工作速度下降。人們為了提高CPU讀寫程式和數據的速度,在RAM和CPU之間增加了高速快取(Cache)部件。Cache的內容是隨機存儲器(RAM)中部分存儲單元內容的副本。

ROM是唯讀存儲器,出廠時其內容由廠家用掩膜技術寫好,只可讀出,但無法改寫。信息已固化在存儲器中,一般用於存放系統程式BIOS和用於微程式控制。

PROM是可程式ROM,只能進行一次寫入操作(與ROM相同),但是可以在出廠後,由用戶使用特殊電子設備進行寫入。

EPROM是可擦除的PROM,可以讀出,也可以寫入。但是在一次寫操作之前必須用紫外線照射,以擦除所有信息,然後再用EPROM編程器寫入,可以寫多次。

EEPROM是電可擦除PROM,與EPROM相似,可以讀出也可寫入,而且在寫操作之前,不需要把以前內容先擦去,能夠直接對定址的位元組或塊進行修改。

閃速存儲器(Flash Memory),其特性介於EPROM與EEPROM之間。閃速存儲器也可使用電信號進行快速刪除操作,速度遠快於EEPROM。但不能進行位元組級別的刪除操作,其集成度高於EEPROM。

連線控制

容量擴展

晶片片選

CPU要實現對

存儲單元的訪問,首先要選擇

存儲晶片,即進行片選;然後再從選中的晶片中依地址碼選擇出相應的存儲單元,以進行數據的存取,這稱為字選。片內的字選是由CPU送出的N條低位

地址線完成的,地址線直接接到所有

存儲晶片的地址輸入端,而存儲晶片的

片選信號則大多是通過高位地址解碼後產生的。

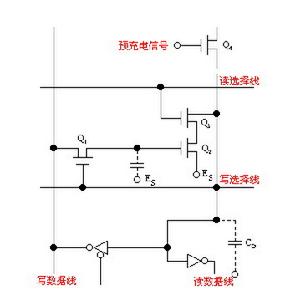

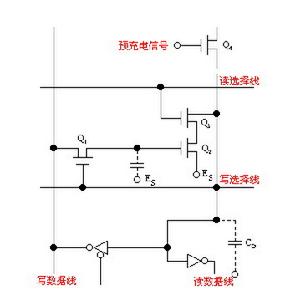

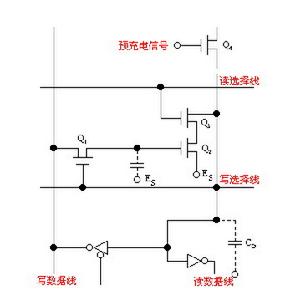

構造圖

構造圖 線選法:

線選法就是用除片內定址外的高位

地址線直接分別接至各個

存儲晶片的

片選端,當某地址線信息為0時,就選中與之對應的存儲晶片。這些

片選地址線每次定址時只能有一位有效,不允許同時有多位有效,這樣才能保證每次只選中一個晶片。線選法不能充分利用系統的

存儲器空間,把

地址空間分成了相互隔離的區域,給編程帶來了一定困難。

全解碼法:

全

解碼法將除片內

定址外的全部高位

地址線都作為地址

解碼器的輸入,解碼器的輸出作為各晶片的

片選信號,將它們分別接到

存儲晶片的片選端,以實現對存儲晶片的選擇。全

解碼法的優點是每片晶片的地址範圍是唯一確定的,而且是連續的,也便於擴展,不會產生地址重疊的

存儲區,但全解碼法對解碼

電路要求較高。

部分

解碼法:所謂部分解碼法即用除片內定址外的高位地址的一部分來解碼產生

片選信號,部分解碼法會產生地址重疊。

連線方法

主存與CPU之間的

硬連線:主存與CPU的硬連線有三組連線:

地址匯流排(AB)、

數據匯流排(DB)和

控制匯流排(CB)。把主存看作一個黑盒子,存儲器地址暫存器(MAR)和存儲器數據暫存器(MDR)是主存和CPU之間的接口。MAR可以接收由

程式計數器(PC)的指令地址或來自

運算器的

運算元的地址,以確定要訪問的單元。MDR是向主存寫入數據或從主存讀出數據的緩衝部件。MAR和MDR從功能上看屬於主存,但通常放在CPU內。

CPU對主存的基本操作:CPU對主存進行讀寫操作時,首先CPU在地址匯流排上給出地址信號,然後發出相應的讀寫

命令,並在數據匯流排上交換信息。讀寫基本操作如下:

模擬圖

模擬圖讀:讀操作是指從CPU送來的地址所指定的

存儲單元中取出信息,再送給CPU,其操作過程如下:

地址——>MAR——ABCPU將地址信號送至地址匯流排

發讀命令

M(MAR)——>DB——>MDR讀出信息經數據匯流排至CPU

寫:寫操作是指將要寫入的信息存入CPU所指定的

存儲單元中,其操作過程是:

地址——>MAR——>ABCPU將地址信號送至地址匯流排

數據——>MDR——>DBCPU將要寫入的數據送至數據匯流排

發寫命令

WaitForMFC等待存儲器工作完成信號

CPU與主存之間的速度匹配:同步

存儲器讀取和異步存儲器讀取。

異步存儲器讀取:CPU和主存間沒有統一的時鐘,由主存工作完成信號(MFC)通知CPU“主存工作已完成”。

同步存儲器讀取:CPU和主存採用統一時鐘,同步工作,因為主存速度較慢,所以CPU與之配合必須放慢速度,在這種存儲器中,不需要主存工作完成信號。

套用技術

快速讀寫

快速頁式工作技術(動態存儲器的快速讀寫技術):讀寫動態存儲器同一行的數據時,其

行地址第一次讀寫時鎖定後保持不變,以後讀寫該行多列中的數據時,僅鎖存列地址即可,省去了鎖存行地址的時間,加快了主

存儲器的讀寫速度。

EDO(ExtendedDataOut)技術:在快速頁式工作技術上,增加了

數據輸出部分的數據鎖存線路,延長輸出數據的有效保持時間,從而地址信號改變了,仍然能取得正確的讀出數據,可以進一步縮短地址送入時間,更加快了主存儲器的讀寫速度。

並行讀寫

是指在主

存儲器的一個工作周期(或較長)可以讀出多個主存字所採用的技術。

方案1:一體多字結構,即增加每個主存單元所包括的

數據位,使其同時

存儲幾個主存字,則每一次讀操作就同時讀出了幾個主存字。

方案2:多體交叉

編址技術,把主

存儲器分成幾個能獨立讀寫的、

字長為一個主存字的主體,分別對每一個存儲體進行讀寫;還可以使幾個存儲體協同運行,從而提供出比單個存儲體更高的讀寫速度。

有兩種方式進行讀寫:

1在同一個讀寫周期同時啟動所有主存體讀或寫。

2讓主存體順序地進行讀或寫,即依次讀出來的每一個

存儲字,可以通過數據匯流排依次傳送走,而不必設定專門的

數據緩衝暫存器;其次,就是採用交叉編址的方式,把連續地址的幾個存儲字依次分配在不同的存儲體中,因為根據程式運行的局部性特性,短時間內讀寫地址相鄰的主存字的機率更大。

主存儲器

主存儲器數據傳送

所謂成組數據傳送就是地址匯流排傳送一次地址後,能連續在數據匯流排上傳送多個數據。而原先是每傳送一次數據要使用兩個

時鐘周期:先送一次地址,後跟一次數據傳送,即要傳送N個數據,就要用2N個匯流排時鐘周期,成組數據傳送方式只用N+1個匯流排時鐘周期。

實現成組

數據傳送方式,不僅CPU要支持這種運行方式,主存也能提供足夠高的數據讀寫速度,這往往通過主存的多體結構、

動態存儲器的EDO支持等措施來實現。

動靜態

靜態

(1)

靜態存儲器的存儲原理和晶片內部結構(P207)

地址匯流排:記為AB15~AB0,統一由

地址暫存器AR驅動,地址暫存器AR只接收ALU輸出的信息。

(1)記憶體寫周期用MMW信號標記

(2)記憶體讀周期用MMR信號標記

(5)記憶體在工作用MMREQ信號標記

(6)外設在工作用IOREQ信號標記

(7)寫控存周期用SWA信號標記

數據匯流排:分為內部數據匯流排IB與外部數據匯流排DB兩部分。主要完成

計算機各功能部件之間的

數據傳送。設計匯流排的核心技術是要保證在任何時刻只能把一組數據傳送到匯流排上,卻允許一個和多個部件同時接受匯流排上的信息。所用的

電路通常為三態門電路。

系統時鐘及時序:教學機晶振1.8432MHz,3分頻後用614.4KHz的時鐘作為系統主時鐘,使CPU、記憶體、IO同步運行。CPU內部的有些

暫存器用時鐘結束時的上升沿完成接受數據,而

通用暫存器是用低電平接收的。記憶體或I/O讀寫操作時,每個匯流排周期由兩個時鐘組成,第一個時鐘,稱為地址時間,用於傳送地址;第二個時鐘,稱為數據時間,用於讀寫數據

教學計算機的內

存儲器用靜態存儲器晶片實現,由2K字的ROM區和2K字RAM區組成。記憶體

字長16位,按字定址。ROM由74LS2716

唯讀存儲器ROM(每片2048個

存儲單元,每單元為8位

二進制位)兩片完成

字長的擴展。地址分配在:0~2047RAM由74LS6116

隨機存儲器RAM(每片2048個

存儲單元,每單元為8位

二進制位)兩片完成

字長的擴展。地址分配在:2048~4095。

靜態存儲器地址分配:

為訪問2048個

存儲單元,要用11位地址,把地址匯流排的低11位地址送到每個存儲器晶片的地址

引腳;對地址匯流排的高位進行

解碼,解碼信號送到各存儲器晶片的/CS引腳,在按字定址的存儲器系統中實現按

位元組讀寫。

動態

動態存儲器的定期刷新:在不進行讀寫操作時,DRAM存儲器的各單元處於斷電狀態,由於漏電的存在,保存在電容CS上的電荷會慢慢地漏掉,為此必須定時予以補充,稱為刷新操作。

(1)

動態存儲器的組成:由單個MOS管來存儲一位

二進制信息。信息

存儲在MOS管的源極的寄生電容CS中。

寫數據時:字線為高電平,T導通。

寫“1”時,位線(

數據線)為低電平,VDD(

電源)將向電容充電

寫“0時,位線(

數據線)為高電平,若電容

存儲了電荷,則將會使電容完成放電,就表示存儲了“0”。

讀數據時:先使位線(數據線)變為

高電平,當字線高電平到來時T導通,若電容原

存儲有電荷(是“1”),則電容就要放電,就會使數據線電位由高變低;若電容沒有存儲電荷(是“0”),則數據線電位不會變化。檢測

數據線上電位的變化就可以區分讀出的數據是1還是0。

注意

①讀操作使電容原

存儲的電荷丟失,因此是破壞性讀出。為保持原記憶內容,必須在讀操作後立刻跟隨一次寫入操作,稱為預充電延遲。

②向

動態存儲器的

存儲單元提供地址,是先送行地址再送列地址。原因就是對

動態存儲器必須定時刷新(如2ms),刷新不是按字處理,而是每次刷新一行,即為連線在同一行上所有

存儲單元的電容補充一次能量。

⑤RAS、CAS、WE、Din、Dout時序關係

主存最佳化

市場上並不缺少提高數據

存儲效率的新技術,然而這些新技術絕大多數都是關注備份和存檔的,而非主存儲。但是,當企業開始進行主

存儲數據縮減時,對他們來說,了解主存儲最佳化所要求的必要條件十分重要。

主

存儲,常常被稱為1級存儲,其特徵是存儲活躍數據――即經常被存取並要求高性能、低時延和高可用性的數據。主

存儲一般用於支持關鍵任務套用,如資料庫、

電子郵件和交易處理。大多數關鍵套用具有隨機的數據取存模式和不同的取存要求,但它們都生成機構用來運營它們的業務的大量的數據。因此,機構製作數據的許多份拷貝,複製數據供分布使用,庫存數據,然後為安全保存備份和存檔數據。

絕大多數數據是起源於主數據。隨著數據存在的時間增加,它們通常被遷移到二級和三級

存儲保存。因此,如果機構可以減少主數據

存儲占用空間,將能夠在數據生命期中利用這些節省下來的

容量和費用。換句話說,更少的主

存儲占用空間意味著更少的數據複製、庫存、存檔和備份。

直到不久前,由於性能問題,

數據壓縮一直沒有在主

存儲套用中得到廣泛套用。然而,Storwize等廠商提供利用實時、

隨機存取壓縮/解壓技術將數據占用空間壓縮15:1的

解決方案。更高的壓縮率和實時性能使壓縮解決方案成為主

存儲數據縮減的可行的選擇。

在備份套用中廣泛採用的數據去重技術也在被套用到主

存儲。目前為止,數據去重面臨著一大挑戰,即數據去重處理是離線處理。這是因為確定數量可能多達數百萬的檔案中的多餘的

數據塊需要大量的時間和存儲

處理器做大量的工作,因此非常活躍的數據可能受到影響。當前,推出數據去重技術的主要廠商包括NetApp、Data Domain和Ocarina

Networks。

主存部署

零性能影響

與備份或存檔

存儲不同,活躍數據集的性能比能夠用某種形式的數據縮減技術節省的存儲容量更為關鍵。因此,選擇的數據縮減技術必須不影響到性能。它必須有效和簡單;它必須等價於“撥動一個

開關,就消耗更少的

存儲”。

活躍

存儲縮減解決方案只在需要去重的數據達到非活躍狀態時才為活躍存儲去重。換句話說,這意味著實際上只對不再被存取但仍保存在活躍

存儲池中的檔案――近活躍存儲級――進行去重。

去重技術通過建議只對輕I/O工作負載去重來避免性能瓶頸。因此,IT基礎設施的關鍵組件的

存儲沒有得到最佳化。資料庫排在關鍵組件清單之首。由於它們是1級

存儲和極其活躍的組件並且幾乎始終被排除在輕工作負載之外,去重處理從來不分析它們。因此,它們在主

存儲中占據的空間沒有得到最佳化。

另一方面,實時壓縮系統實時壓縮所有流經壓縮系統的數據。這導致節省存儲容量之外的意外好處:存儲性能的提高。當所有數據都被壓縮時,每個I/O請求提交的數據量都有效地增加,硬碟空間增加了,每次寫和讀操作都變得效率更高。

實際結果是占用的硬碟

容量減少,總體

存儲性能顯著提高。

主

存儲去重的第二個好處是所有數據都被減少,這實現了包括資料庫在內的所有數據的

容量節省。儘管Oracle環境的實時數據壓縮可能造成一些性能問題,但迄今為止的測試表明性能提高了。

另一個問題是對

存儲控制器本身的性能影響。人們要求今天的

存儲控制器除了做伺服硬碟外,還要做很多事情,包括管理不同的協定,執行複製和管理快照。再向這些功能增加另一個功能可能會超出控制器的承受能力――即使它能夠處理額外的工作負載,它仍增加了一個

存儲管理人員必須意識到可能成為潛在I/O瓶頸的過程。將壓縮工作交給外部專用設備去做,從性能問題中消除了一個變數,而且不會給

存儲控制器造成一點影響。

高可用性

許多關注二級

存儲的數據縮減解決方案不是高可用的。這是由於它們必須立即恢復的備份或存檔數據不像一級

存儲中那樣關鍵。但是,甚至在二級

存儲中,這種概念也逐漸不再時興,高可用性被作為一種選擇添加到許多二級存儲系統中。

可是,高可用性在主

存儲中並不是可選的選項。從數據縮減格式(被去重或被壓縮)中讀取數據的能力必須存在。在數據縮減解決方案中(其中去重被集成到

存儲陣列中),

冗餘性是幾乎總是高可用的存儲陣列的必然結果。

在

配件市場去重系統中,解決方案的一個組件以數據的原始格式向客戶機提供去重的數據。這個組件就叫做讀出器(reader)。讀出器也必須是高可用的,並且是無縫地高可用的。一些解決方案具有在發生故障時在標準

伺服器上載入讀出器的能力。這類解決方案經常被用在近活躍的或更合適的存檔數據上;它們不太適合非常活躍的數據集。

多數在線上壓縮系統被插入系統中和網路上,放置(邏輯上)在

交換機與

存儲之間。因此,它們由於網路基礎設施級上幾乎總是設計具有的高可用性而取得

冗餘性。沿著這些路徑插入在線上專用設備實現了不需要IT管理人員付出額外努力的無縫的故障切換;它利用了已經在網路上所做的工作。

節省空間

部署這些解決方案之一必須帶來顯著的

容量節省。如果減少占用

容量的主

存儲導致低於標準的用戶性能,它沒有價值。

主數據不具有備份數據通常具有的高

冗餘存儲模式。這直接影響到總體

容量節省。這裡也有兩種實現主數據縮減的方法:數據去重和壓縮。

數據去重技術尋找近活躍檔案中的

冗餘數據,而能取得什麼水平的數據縮減將取決於環境。在具有高

冗餘水平的環境中,數據去重可以帶來顯著的ROI(投資回報),而另一些環境只能取得10%到20%的縮減。

壓縮對所有可用數據都有效,並且它在可以為高

冗餘數據節省更多的存儲容量的同時,還為主存儲套用常見的更隨機的數據模式始終帶來更高的節省。

實際上,數據模式冗餘度越高,去重帶來的空間節省就越大。數據模式越隨機,壓縮帶來的空間節省就越高。

獨立於套用

真正的好處可能來自所有跨數據類型(不管產生這些數據是什麼套用或數據有多活躍)的數據縮減。雖然實際的縮減率根據去重數據的水平或數據的壓縮率的不同而不同,但所有數據都必須合格。

當涉及存檔或備份時,套用特有的數據縮減具有明確的價值,並且有時間為這類數據集定製縮減過程。但是對於活躍數據集,套用的特殊性將造成性能瓶頸,不會帶來顯著的

容量縮減的好處。

獨立於存儲

在混合的廠商IT基礎設施中,跨所有平台使用同樣的數據縮減

工具的能力不僅將進一步增加數據縮減的ROI好處,而且還簡化了部署和管理。每一個

存儲平台使用一種不同的數據縮減方法將需要進行大量的培訓,並造成管理級上的混亂。

互補

在完成上述所有最佳化主

存儲的工作後,當到了備份主存儲時,最好讓數據保持最佳化的格式(被壓縮或去重)。如果數據在備份之前必須擴展恢復為原始格式,這將是浪費資源。

為備份擴展數據集將需要:

構造圖

構造圖 模擬圖

模擬圖 主存儲器

主存儲器

構造圖

構造圖 模擬圖

模擬圖 主存儲器

主存儲器