基本簡介 SRAM不需要刷新電路即能保存它內部存儲的數據。而DRAM(Dynamic Random Access Memory) 每隔一段時間,要刷新充電一次,否則內部的數據即會消失,因此SRAM具有較高的性能,但是SRAM也有它的缺點,即它的集成度較低,功耗較DRAM大,相同容量的DRAM記憶體可以設計為較小的體積,但是SRAM卻需要很大的體積。同樣面積的矽片可以做出更大容量的DRAM,因此SRAM顯得更貴。

主要規格 一種是置於cpu與主存間的

高速快取 ,它有兩種規格:一種是固定在主機板上的高速快取(Cache Memory);另一種是插在卡槽上的COAST(Cache On A Stick)擴充用的高速快取,另外在

CMOS晶片 1468l8的電路里,它的內部也有較小容量的128位元組SRAM,存儲我們所設定的配置數據。還有為了加速CPU內部數據的傳送,自80486CPU起,在CPU的內部也設計有高速快取,故在Pentium CPU就有所謂的L1 Cache(一級高速快取)和L2Cache(二級高速快取)的名詞,一般L1 Cache是建在CPU的內部,L2 Cache是設計在CPU的外部,但是Pentium Pro把L1和L2 Cache同時設計在CPU的內部,故Pentium Pro的體積較大。

Pentium Ⅱ又把L2 Cache移至CPU核心之外的黑盒子裡。SRAM顯然速度快,不需要刷新操作,但是也有另外的缺點,就是價格高,體積大,所以在主機板上還不能作為用量較大的主存。

主要用途 SRAM主要用於二級

高速快取 (Level2 Cache)。它利用電晶體來存儲數據。與DRAM相比,SRAM的速度快,但在相同面積中SRAM的容量要比其他類型的記憶體小。

圖1.SRAM SRAM的速度快但昂貴,一般用小容量的SRAM作為更高速CPU和較低速DRAM 之間的

快取 (cache).SRAM也有許多種,如AsyncSRAM (Asynchronous SRAM,異步SRAM)、Sync SRAM (Synchronous SRAM,同步SRAM)、PBSRAM (Pipelined Burst SRAM,流水式突發SRAM),還有INTEL沒有公布細節的CSRAM等。

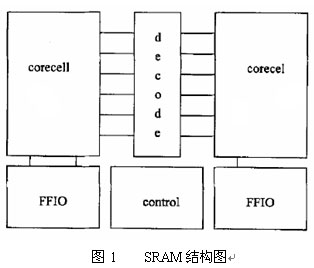

基本的SRAM的架構如圖1所示,SRAM一般可分為五大部分:存儲單元陣列(core cells array),行/列地址

解碼器 (decode),靈敏放大器(Sense Amplifier),控制電路(control circuit),緩衝/驅動電路(FFIO)。SRAM是

靜態存儲方式 ,以雙穩態電路作為

存儲單元 ,SRAM不像DRAM一樣需要不斷刷新,而且工作速度較快,但由於存儲單元器件較多,集成度不太高,功耗也較大。

工作原理 SRAM的工作原理:

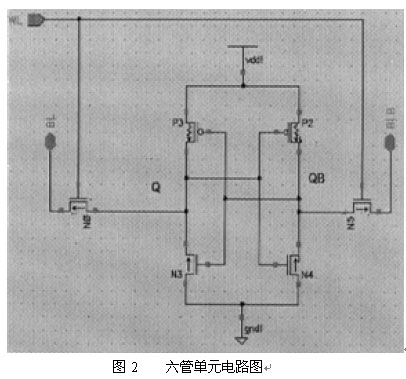

圖2.六管單元電路圖 假設準備往圖2的6T

存儲單元 寫入“1”,先將某一組地址值輸入到行、列

解碼器 中,選中特定的單元,然後使寫使能信號WE有效,將要寫入的數據“1”通過寫入電路變成“1”和“0”後分別加到選中單元的兩條位線BL,BLB上,此時選中單元的WL=1,電晶體N0,N5打開,把BL,BLB上的信號分別送到Q,QB點,從而使Q=1,QB=0,這樣數據“1”就被鎖存在電晶體P2,P3,N3,N4構成的

鎖存器 中。寫入數據“0”的過程類似。

SRAM的讀過程以讀“1”為例,通過解碼器選中某列位線對BL,BLB進行預充電到電源電壓VDD,預充電結束後,再通過行解碼器選中某行,則某一

存儲單元 被選中,由於其中存放的是“1”,則WL=1、Q=1、QB=0。電晶體N4、N5導通,有電流經N4、N5到地,從而使BLB電位下降,BL、BLB間電位產生電壓差,當電壓差達到一定值後打開靈敏度放大器,對電壓進行放大,再送到輸出電路,讀出數據。

SRAM的類型 非揮發性SRAM 非揮發性SRAM (Non-volatile SRAM,nvSRAM)具有SRAM的標準功能,但在失去電源供電時可以保住其數據。非揮發性SRAM用於網路、航天、醫療等需要關鍵場合—保住數據是關鍵的而且不可能用上電池。

異步SRAM 異步SRAM(Asynchronous SRAM)的容量從4 Kb到64 Mb。SRAM的快速訪問使得異步SRAM適用於小型的cache很小的嵌入式處理器的主記憶體,這種處理器廣泛用於工業電子設備、測量設備、硬碟、網路設備等等。

根據電晶體類型分類 雙極性結型電晶體(用於

TTL 與

ECL )—非常快速但是功耗巨大

根據功能分類 異步 —獨立的時鐘頻率,讀寫受控於地址線與控制使能信號。

同步 —所有工作是時鐘脈衝邊沿開始,地址線、數據線、控制線均與時鐘脈衝配合。

根據特性分類 零匯流排翻轉(Zero bus turnaround,ZBT)—SRAM匯流排從寫 到讀 以及從讀 到寫 所需要的時鐘周期是0

同步突發SRAM(synchronous-burst SRAM,syncBurst SRAM)—

DDR SRAM—同步、單口讀/寫,雙數據率I/O

QDR SRAM(Quad Data Rate (QDR) SRAM)—同步,分開的讀/寫口,同時讀寫4個字(word)。

根據觸發類型 結構原理 SRAM (Static RAM),即靜態RAM.它也由電晶體組成。接通代表1,斷開表示0,並且狀態會保持到接收了一個改變信號為止。這些電晶體不需要刷新,但停機或斷電時,它們同DRAM一樣,會丟掉信息。SRAM的速度非常快,通常能以20ns或更快的速度工作。一個DRAM

存儲單元 僅需一個電晶體和一個小電容.而每個SRAM單元需要四到六個電晶體和其他零件。所以,除了價格較貴外,SRAM晶片在外形上也較大,與DRAM相比要占用更多的空間。由於外形和電氣上的差別,SRAM和DRAM是不能互換的。

SRAM的高速和靜態特性使它們通常被用來作為Cache

存儲器 。計算機的主機板上都有Cache插座。

如圖所示的是一個SRAM的結構框圖。由上圖看出SRAM一般由五大部分組成,即

存儲單元 陣列、地址

解碼器 (包括行解碼器和列解碼器)、靈敏放大器、控制電路和緩衝/驅動電路。在圖中,A0-Am-1為地址輸入端,CSB. WEB和OEB為控制端,控制讀寫操作,為

低電平有效 ,1100-11ON-1為數據輸入輸出端。

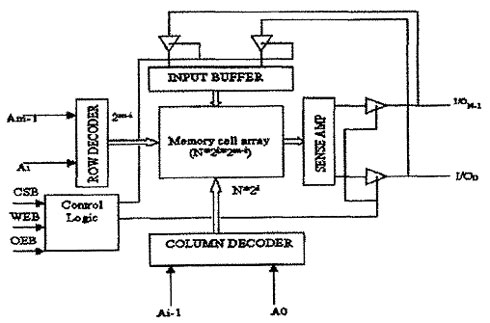

存儲陣列 中的每個存儲單元都與其它單元在行和列上共享電學連線,其中水平方向的連線稱為“

字線 ”,而垂直方向的數據流入和流出存儲單元的連線稱為“位線”。通過輸入的地址可選擇特定的字線和位線,字線和位線的交叉處就是被選中的存儲單元,每一個存儲單元都是按這種方法被唯一選中,然後再對其進行讀寫操作。有的

存儲器 設計成多位數據如4位或8位等同時輸入和輸出,這樣的話,就會同時有4個或8個

存儲單元 按上述方法被選中進行讀寫操作。

圖3.SRAM 在SRAM 中,排成

矩陣 形式的存儲單元陣列的周圍是

解碼器 和與外部信號的接口電路。存儲單元陣列通常採用正方形或矩陣的形式,以減少整個晶片面積並有利於數據的存取。以一個存儲容量為4K位的SRAM為例,共需12條

地址線 來保證每一個存儲單元都能被選中(

=4096)。如果

存儲單元 陣列被排列成只包含一列的長條形,則需要一個12/4K位的

解碼器 ,但如果排列成包含64行和64列的正方形,這時則只需一個6/64位的行解碼器和一個6/64位的列解碼器,行、列解碼器可分別排列在存儲單元陣列的兩邊,64行和64列共有4096個交叉點,每一個點就對應一個存儲位。因此,將存儲單元排列成正方形比排列成一列的長條形要大大地減少整個晶片地面積。存儲單元排列成長條形除了形狀奇異和面積大以外,還有一個缺點,那就是單排在列的上部的存儲單元與數據輸入/輸出端的連線就會變得很長,特別是對於容量比較大得

存儲器 來說,情況就更為嚴重,而連線的延遲至少是與它的長度成線性關係,連線越長,線上的延遲就越大,所以就會導致讀寫速度的降低和不同存儲元連線延遲的不一致性,這些都是在設計中需要避免的。

套用與使用 特性 SRAM是比DRAM更為昂貴,但更為快速、低功耗(僅空閒狀態)。因此SRAM首選用於頻寬要求高。SRAM比起DRAM更為容易控制,也更是隨機訪問。由於複雜的內部結構,SRAM比DRAM的占用面積更大,因而不適合用於更高儲存密度低成本的套用,如PC記憶體。

時鐘頻率與功耗

SRAM功耗取決於它的訪問頻率。如果用高頻率訪問SRAM,其功耗比DRAM大得多。有的SRAM在全頻寬時功耗達到幾個瓦特量級。另一方面,SRAM如果用於溫和的時鐘頻率的微處理器,其功耗將非常小,在空閒狀態時功耗可以忽略不計—幾個微瓦特級別。

SRAM用於:

集成於晶片內

嵌入式套用

工業與科學用的很多子系統,汽車電子等等都用到了SRAM。現代設備中很多都嵌入了幾千位元組的SRAM。實際上幾乎所有實現了電子用戶界面的現代設備都可能用上了SRAM,如玩具。數位相機、手機、音響合成器等往往用了幾兆位元組的SRAM。 實時信號處理電路往往使用雙口(dual-ported)的SRAM。

用於計算機

SRAM用於PC、工作站、路由器以及外設:內部的CPU高速快取,外部的突發模式使用的SRAM快取,硬碟緩衝區,路由器緩衝區,等等。LCD顯示器或者印表機也通常用SRAM來快取數據。SRAM做的小型緩衝區也常見於

CDROM 與CDRW的驅動器中,通常為256 KiB或者更多,用來緩衝音軌數據。

線纜數據機 及類似的連線於計算機的設備也使用了SRAM。

愛好者

搭建自己的處理器的業餘愛好者更願意選用SRAM,這是由於其易用性的工作界面。沒有DRAM所需的刷新周期;地址匯流排與數據匯流排直接訪問而不是像DRAM那樣

多工 分別訪問。SRAM通常只需3個控制信號:Chip Enable (CE), Write Enable (WE)與Output Enable(OE)。對於同步SRAM,還需要時鐘信號(Clock,CLK)。

參見 DRAM ,包括PSRAM (pseudo-static RAM)

圖1.SRAM

圖1.SRAM 圖2.六管單元電路圖

圖2.六管單元電路圖 圖3.SRAM

圖3.SRAM