基本介紹

- 中文名:DSP系統設計開發工具

- 外文名:DSP Builder

主要功能

DSP Builder設計流程

DSP Builder設計流程

DSP Builder設計流程

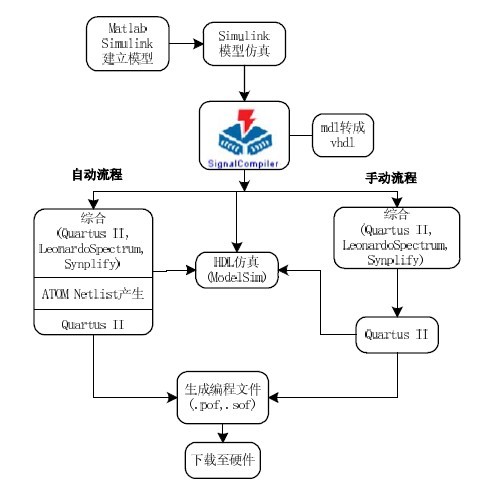

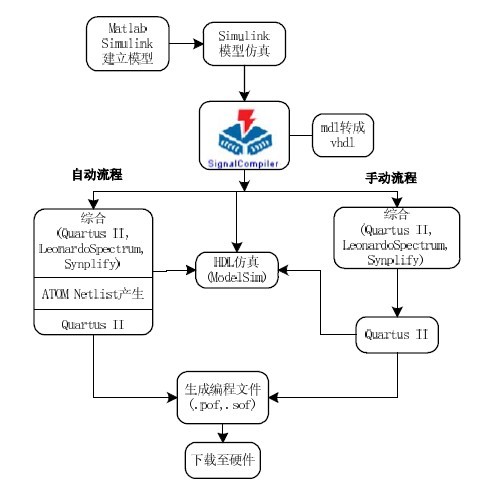

DSP Builder設計流程Altera可程式邏輯器件(PLD)中的DSP系統設計需要高級算法和HDL開發工具。Altera DSP Builder將The MathWorks MATLAB和Simulink系統級設計工具的算法開發、仿真和驗證功能...

《現代DSP技術》是2003年8月1日西安電子科技大學出版社出版的圖書。...... 全書深入、系統地介紹了基於MATLAB環境下DSP Builder/SignalCompiler對現代DSP系統開發的基...

8.1DSPBuilder及其設計流程1898.2利用DSPBuilder設計實例190習題8194參考文獻195 [2] 參考資料 1. DSP技術與套用實踐教程 .1[引用日期2017-12-13] 2. 1 .1...

有了dspbuiler,那么視頻信號處理這一實時性要求較高的功能完全可以用dspbuilder直接生成,然後用nios代替傳統dsp處理器的數據後處理和通訊功能,同時在集成pci接口和其他...

第7章 基於fpga的dsp開發設計7.1 概述7.2 dsp builder功能簡介與設計流程7.2.1 dsp builder功能簡介7.2.2 dsp builder設計流程...

MathWorks公司發布的基於Simulink HDL Coder&Filter Builder的開發FP-GA的最新解決方案、基於標準模組庫的DSP Builder設計方法,基於高級模組庫的DSP Builder設計方法...

實驗11-2基於DSPBuilder的DDS套用模型設計 330實驗11-3編解碼器設計實驗 332實驗11-4HIL硬體環仿真實驗 332實驗11-5DSPBuilder狀態機套用實驗 333...

1.4.2 安裝DSP Builder 44第2章 FPGA設計流程 462.1 QuartusⅡ設計流程概述 462.2 設計輸入 512.3 設計約束和分配 542.4 設計綜合 56...

基於Verilog的有限狀態機設計技術、基於VHDL的16位實用CPU設計技術及創新實踐項目、基於ModelSim的Test Bench仿真技術、基於MATLAB和DSPBuilder平台的EDA設計技術及大量...

第三篇介紹IP核設計套用,包括基於Simulink環境的系統級設計軟體DSP Builder、PCI編譯器和FFT兆核函式。第四篇介紹Quartus Ⅱ軟體FPGA設計中的特殊技術,包括邏輯鎖定...

MathWorks公司發布的基於Simulink HDL Coder&Filter Builder的開發FP-GA的最新解決方案、基於標準模組庫的DSP Builder設計方法,基於高級模組庫的DSP Builder設計方法、...

Altera公司新一代的PLD開發軟體Quartus II使用入門與進階、第三方工具軟體、LogicLock設計方法、DSP Builder設計工具、SOPCBuilder與Nios II嵌入式處理器核的軟硬體開發...

另外還介紹了使用MATLAB和DSP Builder進行基於FPGA的DSP開發技術,並提供了一些典型的實驗。本書可作為高等院校電子信息類各專業本科生、研究生的教材,也可以作為相關...

第1章:概述第2章:Quartus基本使用方法第3章:適配與時序最佳化設定第4章:邏輯鎖定技術第5章:Matlab/DSP Builder設計嚮導第6章:DSP與數字通信模組設計第7章:SOPC...

使用Altera DSP Builder和SOPC Builder系統設計工具,很容易集成您自己的定製DSP功能庫和Altera提供的功能。四.Altera 視頻系列 1)使用Altera視頻智慧財產權(IP)、參考...

ISE開發流程及ModelSim仿真套用;第三部分重點講述VHDL語言基礎、描述方法及設計實例;第四部分主要介紹DSP Builder、SOPC Builder、NiosⅡ套用及實例;第五部分介紹實驗及...