簡介

英文全稱:System On a Programmable Chip. SOPC實驗板中文譯名:可程式

片上系統 實驗板

實驗板SOPC它是用可程式邏輯技術把整個系統放到一塊矽片上,來用於

嵌入式系統的研究和電子信息處理. SOPC是一種特殊的嵌入式系統,它是片上系統(SOC),即由單個晶片完成整個系統的主要邏輯功能但它不是簡單的SOC,它也是可程式系統,具有靈活的設計方式,可裁減、可擴充、可升級,並具備軟硬體在系統可程式的功能。

技術內容

SOPC設計技術涵蓋了

嵌入式系統設計技術的全部內容,除了以處理器和

實時多任務作業系統(RTOS)為中心的

軟體設計技術、以PCB和

信號完整性分析為基礎的高速電路設計技術以外,SOPC還涉及以引起普遍關注的

軟硬體協同設計技術。由於SOPC的主要

邏輯設計是在

可程式邏輯器件內部進行,而BGA封裝已被廣泛套用在微封裝領域中,傳統的

調試設備,如:邏輯分析儀和數字示波器,已很難進行直接測試分析,因此,必將對以仿真技術為基礎的軟硬體協同設計技術提出更高的要求。同時,新的調試技術也已不斷湧現出來,如Xilinx公司的片內邏輯分析儀Chip Scope ILA就是一種價廉物美的片內實時調試工具。

特點

SOPC結合了SOC和PLD、FPGA各自的優點,一般具備以下基本特徵:

具有小容量片內高速RAM資源;

豐富的IP Core資源可供選擇;

足夠的片上可程式邏輯資源;

可能包含部分可程式模擬電路;

單晶片、低功耗、微封裝。

簡單流程

完整的基於

NiosII的SOPC系統是一個軟硬體複合的系統,因此在設計時可分為硬體和軟體兩部分。NiosII的硬體設計是為了定製合適的

CPU和

外設,在SOPCBuider和

QuartusII中完成。在這裡可以靈活定製NiosII CPU的許多特性甚至指令,可使用

Altera公司提供的大量

IP核來加快開發NiosII外設的速度,提高外設性能,也可以使用第三方的IP核或

VHDL來自行定製外設。完成NiosII的

硬體開發後,SOPCBuider可自動生成與自定義的NiosIICPU和外設系統、

存儲器、外設地址映射等相應的軟體開發包SDK,在生成的

SDK基礎上,進入軟體開發流程。用戶可使用彙編或C,甚至C++來進行嵌入式程式設計,使用

GNU工具或其它第三方工具進行程式的編譯連線以及

調試。

第一步:打開QuartusII軟體,點擊tool按鍵

第二步:點擊用紅色標記的SOPCBuilder

第二步

第二步第三步:定製CPU

第四步:完成並下載之nios電路板中

第三步

第三步支持晶片

1)Cyclone系列

2)Cyclone II系列

3)Cyclone III系列

4)Stratix系列

5)Stratix II系列

6)Stratix III系列

套用

SOPC系統的總體設計方案

本系統採用加拿大 SBS公司的 TSUNAMI A40系列

開發板,其核心的 FPGA模組是

Altera公司的 StratixEP1S40晶片。

2.1 系統算法的基本原理

系統算法實現流程。首先,針對本系統圖像處理的要求與算法實現特點進行軟硬體劃分。圖像

預處理部分所需要處理的數據量比較大,但算法相對簡單,可以通過 FPGA自定義相應的 IP模組,採用硬體的方式實現;後續處理部分由於算法相對複雜,用硬體實現比較困難,而且其數據處理量不大,所以採用在 Nios II

軟核中以軟體的方式實現。最後編寫系統控制軟體對整個系統進行控制使軟硬體協同工作。

圖

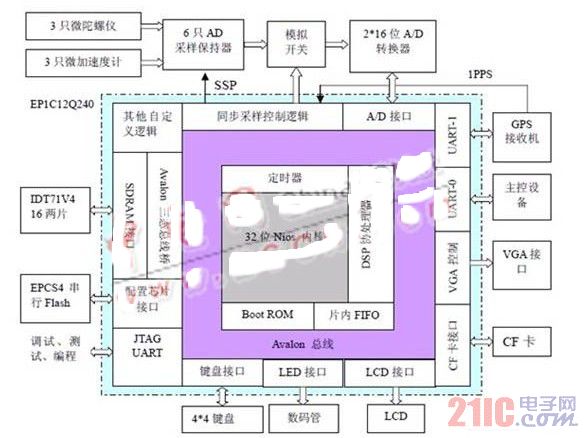

圖2.2 系統硬體的設計方案

如圖 所示,本系統

硬體開發板通過 PCI橋與 PC機相連,原始圖片保存在 PC機中。 PCI-Avalon橋是 PC機與 FPGA開發板的通信

接口,圖像數據經過 PCI-Avalon橋進入系統處理模組。

Sdram管理控制器用來管理和控制 Sdram中的數據存取。控制電路用來控制與協調各個

外設的運行,實現狀態控制與數據傳輸等基本操作,包括讀取 Sdram中保存的圖像數據,控制圖像處理各模組。 Sdram用來保存圖像數據。原始圖像數據最初由 PC機下載到 Sdram中,再通過 Sdram管理控制器傳輸給各處理模組依次處理。處理後的圖像數據仍然通過 Sdram管理控制器返回 Sdram中保存。最後通過 PCI橋把最終圖像返回到 PC機。

2.3 系統軟體的設計

本系統的控制流程相對簡單,因此在 Nios II

軟核中沒有內嵌作業系統,而是通過 IO操作調用中斷的方式實現運行狀態的控制、數據通信、協調外設等基本操作,

控制系統各硬體模組,使系統軟硬體協同工作。整個系統搭建成功之後,在 PC機上編寫應用程式對整個SOPC系統的運行進行控制。

3 系統算法的具體實現

3.1 濾波模組

根據所採集到的圖像的特點,本文採用 3×3的模板實現

中值濾波,這種方法不僅可以濾除圖像中的噪聲,而且可以將邊緣信息很好的保留下來。一般求取中值的方法是採用取冒泡法排序,但這種算法並不適合硬體實現。考慮到硬體實現的特點和效率,本文採用了一種全新的求取中值的算法,其原理如圖 3所示。其中 max、mid、min分別表示三輸入的最大值、中值和最小值

比較器。最後經幾輪比較後求得中值。

3.2 邊緣提取模組及二值化模組

邊緣提取採用 Roberts運算元。 Roberts邊緣檢測運算元利用局部差分運算元尋找邊緣。

由於待處理圖像特徵明顯,採用經驗閾值法對圖像進行二值化,算法簡單、實現方便。

3.3 邊緣細化模組

本文的邊緣是建立在二值化之後的,因此處理的圖像都是二值化的,邊緣非常清晰,不需要太複雜的算法。這裡採用兩個 3×3模板作乘積,如圖所示, X為待處理像素。如果模板乘積不為 0,於是中心象素為 1,反之為 0,即點的周圍有灰度為 0的象素,則保留此點,否則剔除。如此很容易得到二值化後點的單象素邊緣。

3.4 後續處理部分

後續處理部分由於其數據處理量並不大且算法比較複雜,所以在本系統中,這部分算法在NiosⅡ中以軟體的方法實現。

4 系統測試結果的分析與總結

經測試,本系統所有算法用 C語言在 PC機(配置: Pentium( R) 4

CPU3.00GHz, 512MB記憶體)上實現,所需時間為 2'12",而本系統僅需 30",其中主要耗時為 NiosII軟體處理部分,系統的硬體算法部分所耗時間不到 1"。

三個方向

1)基於FPGA嵌入IP

硬核的套用。這種SOPC系統是指在FPGA中預先植入處理器。這使得FPGA靈活的硬體設計與處理器的強大軟體功能有機地結合在一起,高效地實現SOPC系統。

2)基於FPGA嵌入IP

軟核的套用。這種SOPC系統是指在FPGA中植入

軟核處理器,如:NIOS II核等。用戶可以根據設計的要求,利用相應的EDA工具,對NIOS II及其

外圍設備進行構建,使該

嵌入式系統在硬體結構、功能特點、資源占用等方面全面滿足用戶系統設計的要求。

3)基於HardCopy技術的套用。這種SOPC系統是指將成功實現於FPGA器件上的SOPC系統通過特定的技術直接向ASIC轉化。把大容量FPGA的靈活性和ASIC的市場優勢結合起來,實現對於有較大批量要求並對成本敏感的電子產品,避開了直接設計ASIC的困難。

前景

SOPC是PLD和

ASIC技術融合的結果,0.13微米的ASIC產品製造價格仍然相當昂貴,相反,集成了

硬核或

軟核CPU、DSP、

存儲器、外圍I/O及

可程式邏輯的SOPC晶片在套用的靈活性和價格上有極大的優勢。SOPC被稱為“半導體產業的未來”。

個人理解

很多人把主要精力放到了nios的定製上,認為可定製的CPU這一靈活的功能就是sopc的靈魂,實現了nios後,把fpga作為一個傳統的mcu來使用,這實際上是一種大材小用的行為,試想,相對於mcu系統來說,僅僅為了那一點點靈活性,就要憑空在

系統設計中增添一項定製工作而得到一個並不是非常穩定可靠的

cpu,然後用一個並不是很成熟的開發環境去進行和mcu系統類似的開發,這實在不是產品開發之道。當然,可以把邏輯電路也一同用fpga來實現,這就有那么一點sopc的味道了。我個人對sopc的看法如下:

1:sopc應該是nios系統+硬實時部分+邏輯電路的一個組合體,其中nios負責數據管理,通訊,人機互動等實時性相對較低的任務,硬實時部分則是獨立於nios系統,充分利用現有IP,用hdl語言實現的某些實時性可靠性要求較高的關鍵部分,它可以和nios系統通過自定義的

接口通訊。至於邏輯電路,這本就是fpga的強項,沒啥可說的,做一些接口以及邏輯處理吧。

2:對於nios系統,

ALTERA已經推出了相對比較完整的方案,nios在功能上來講,已經非常全面了,並且也有多種os可供選擇,據說年底要推出帶有mmu的nios,到時候,linux應該會在nios上大行其道。

3:對於我認為最關鍵的硬實時部分,我認為這才是sopc系統的精華所在,但由於純粹要用hdl語言實現,最多是結合一些現有的ip,因此難度較高,我覺得這也正是ALTERA一直鼓吹sopc但效果卻並不理想的根本原因,不過ALTERA自有妙計,於是推出了dspbuilder。

4:至於dspbuilder,純粹是為了降低系統硬實時部分編碼過於困難的一個工具,

ALTERA推出的參考方案多是音視頻等

信號處理領域,但是由於靠上了matlab這個大牛(控制領域事實上的標準),自然是要在控制領域多下工夫,只是還不支持浮點,並且相應的IP也不齊備,但是基於matlab的直接

代碼生成,肯定是一個方向,相信dsp builder會馬上支持浮點的,並且應該會在控制領域有所動作。實際上,dspbuilder或者說

XILINX的SYSTEMgenerator的推出,就是為了降低開發難度,配合nios實現sopc系統,以此來和傳統的dsp處理器市場。

5:舉一個例子說明一下sopc的作用,以pci匯流排的視頻卡來講,一般來說都是dsp處理器完成視頻

信號處理(實時性要求較高)、數據後處理、與pc通訊等功能,系統中如果採用fpga,大都是實現pci的橋接器以及其他邏輯功能,有了dspbuiler,那么視頻信號處理這一實時性要求較高的功能完全可以用dspbuilder直接生成,然後用nios代替傳統dsp處理器的數據後處理和通訊功能,同時在集成pci

接口和其他邏輯功能,如此則sopc大事成矣。

6:在控制領域,關鍵問題是controller的實現,首先在控制領域,我認為nios2直接做控制器還難當大任,而且就算拋開可靠性、成熟性等因素,控制領域一般都是需要硬實時(hard real-time),同時一般還會有大量的浮點處理,我個人估計nios2恐怕難以實現,這些已經決定了controller必須用硬體實現,也就是用

vhdl寫控制器,這樣做的話,對於系統中所需要的

浮點運算,最好用相應的ip實現,否則恐怕很難。

實驗板

實驗板 第二步

第二步 第三步

第三步 圖

圖

實驗板

實驗板 第二步

第二步 第三步

第三步 圖

圖