基本介紹

- 中文名:C-V特性曲線

- 學科:電子工程

套用,金屬-氧化物-半導體結構的C-V特性,累積,耗盡,反型,摻雜 (半導體),

套用

金屬-氧化物-半導體結構的C-V特性

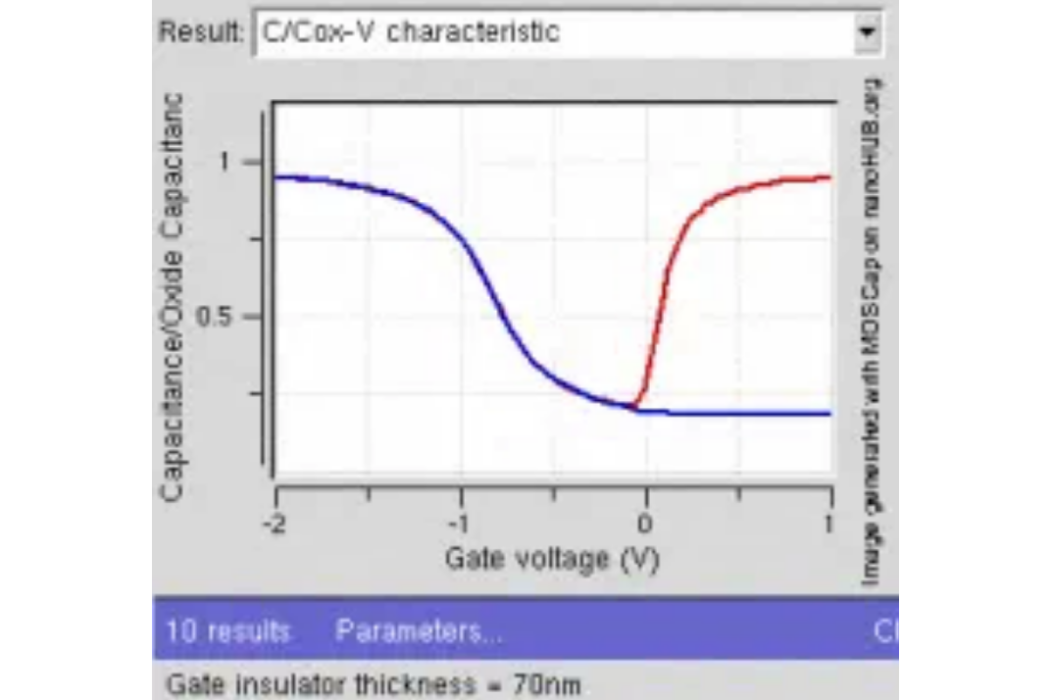

對於一個n溝道MOSFET來說,該結構的工作特性可分為三個部分,分別與圖1對應:

圖1 場效應管在不同柵極厚度下的C-V特性曲線。

累積

考慮一個p型的半導體(電洞濃度為NA)形成的MOS電容,當給電容器加負電壓時,電荷增加(如C-V曲線右側所示)。

耗盡

相反,當一個正的電壓VGB施加在閘極與基極端時,電洞的濃度會減少(稱為耗盡,如C-V曲線中間所示),電子的濃度會增加。

反型

當VGB夠強時,接近閘極端的電子濃度會超過電洞。這個在p-type半導體中,電子濃度(帶負電荷)超過電洞(帶正電荷)濃度的區域,便是所謂的反轉層(inversion layer),如C-V曲線右側所示。

MOS電容的特性決定了金氧半場效電晶體的操作特性,但是一個完整的金氧半場效電晶體結構還需要一個提供多數載流子(majority carrier)的源極以及接受這些多數載子的汲極。

摻雜 (半導體)

摻雜(英語:doping)是半導體製造工藝中,為純的本徵半導體引入雜質,使之電氣屬性被改變的過程。引入的雜質與要製造的半導體種類有關。輕度和中度摻雜的半導體被稱作是雜質半導體,而更重度摻雜的半導體則需考慮費米統計律帶來的影響,這種情況被稱為簡併半導體。

摻雜之後的半導體能帶會有所改變。依照摻雜物的不同,本徵半導體的能隙之間會出現不同的能階。施體原子會在靠近導帶的地方產生一個新的能階,而受體原子則是在靠近價帶的地方產生新的能階。假設摻雜硼原子進入矽,則因為硼的能階到矽的價帶之間僅有0.045電子伏特,遠小於矽本身的能隙1.12電子伏特,所以在室溫下就可以使摻雜到矽里的硼原子完全解離化。

摻雜物對於能帶結構的另一個重大影響是改變了費米能階的位置。在熱平衡的狀態下費米能階依然會保持定值,這個特性會引出很多其他有用的電特性。舉例來說,一個p-n結的能帶會彎折,起因是原本p型半導體和n型半導體的費米能階位置各不相同,但是形成p-n結後其費米能階必須保持在同樣的高度,造成無論是p型或是n型半導體的導帶或價帶都會被彎曲以配合界面處的能帶差異。