C-V測量是半導體特徵分析與測試的基礎。

概念,三種測量技術,方法與套用,局限性,測量誤差,技術連線,技術分享,

概念

電容-電壓測試長期以來被用於判斷多種不同器件和結構的各種半導體參數,範圍從MOSCAP、MOSFET、雙極結型電晶體[1]和JFET到III-V族化合物器件、光伏(太陽能)電池[2]、MEMS器件、有機薄膜電晶體(TFT)顯示器、光電二極體和碳納米管[3]。研發實驗室廣泛利用C-V測量技術評測新材料、工藝、器件和電路。負責產品和良率增強的工程技術人員利用它們最佳化工藝和器件性能;可靠性工程師利用這類測量技術對供貨商的材料進行資格檢驗,監測工藝參數,分析失效機理。

三種測量技術

半導體C-V測試目前可以採用三種不同的電容測量技術:常用的交流阻抗電容計、準靜態電容測量以及射頻技術(採用矢量網路分析儀和射頻探測器)。接下來我們簡要介紹一下每種技術。

1、交流阻抗電容計及參數的測量方法

交流阻抗表[4],也稱為LCR表[5](電感[L]、電容[C]、電阻[R]),利用一個自動平衡電橋保持電容的檢測端交流假接地,從而測量復阻抗。這類電錶通常的頻率範圍為1kHz到10MHz。

交流電源、交流伏特計、交流安培計

圖1.交流阻抗表 圖1

圖1

圖1

圖1這類電錶(如圖1所示)工作原理相對簡單。它通過在高電流輸出端(HCUR)施加一個交流電壓來測量交流阻抗[6]。通過低電流端(LCUR)測量流過器件的電流,通過高低電位端(HPOT和LPOT)測量器件上的電壓降。電壓和電流的測量採用了能夠精確判斷二者之間相位角的鎖相方式[7]。通過測量幅值和相位角,就可以計算出任意所需的交流阻抗參數。

Z、θ ——阻抗與相位角 圖2

圖2

圖2

圖2R+jX ——電阻與電抗

Cp-Gp ——並聯電容和電導

Cs-Rs ——串聯電容和電阻

Cp-D ——並聯電容和耗散因子

Cs-D ——串聯電容和耗散因子

R+jX ——電阻與電抗

Cp-Gp ——並聯電容和電導

Cs-Rs ——串聯電容和電阻

Cp-D ——並聯電容和耗散因子

Cs-D ——串聯電容和耗散因子

圖2. 基本的交流阻抗參數

要得到基本交流阻抗參數就必須測量阻抗的幅值,在圖2中表示為“Z”。還需要測量電流和電壓之間的相位角,表示為θ。因此,在極坐標方式下,這一阻抗就是相角為θ的Z。但我們還可以從數學上將其轉化為直角坐標的形式,即表示為R+jX。其中R是實數部分,即同相阻抗矢量,jX是虛數部分,即相位阻抗矢量偏轉90°,它也是電容矢量。我們甚至可以從數學上將極坐標和直角坐標形式轉化為實際的電容和電阻值。

有兩種常用的交流阻抗模型:並聯模型和串聯模型。在並聯模型中,結果表示為並聯電容(Cp)和並聯電導(Gp)。在串聯模型中,結果表示為串聯電容(Cs)和串聯電阻(Rs)。耗散因子(D),即實阻抗與虛阻抗的比值,是從數學上推導出的另外一個常用參數。當測量晶圓上的電容時,我們通常要看耗散因子,因為它是判斷最終C-V測量質量的最佳指標。無論採用哪種交流阻抗模型,耗散因子都很容易計算出來。

2、基於數字源表的準靜態電容測量

在準靜態電容測量[8]中,我們通過測量電流和電荷來計算電容值。這種“斜率”方法使用簡單,但是它的頻率範圍有限(1 ~10Hz),因而只能用於一些特殊情況下。

圖3. 準靜態C-V“斜率”測量方法

斜率測量方法只需要使用兩台數字源表(SMU)[9]。通過第一台SMU將一個恆定電流載入到待測器件(DUT)的一個節點上。這台SMU還負責測量該節點上的電壓和時間。同時,第二台SMU測量DUT另一個節點輸出的電流。然後可以利用下列公式計算出電容:

I = C dV/dt or C = I / (dV/dt)

這種方法通常可用於測量大小為100~400pF斜率為0.1~1V/S的電容。

3、利用射頻技術[10]測量電容

傳輸線的電容測量通常採用射頻技術。其中利用矢量網路分析儀測量散射參數(S參數),即入射波的反射和傳輸係數。

方法與套用

交流阻抗技術是最常用的電容測量技術[11]。它最適合於一般的低功率門電路,也適用於大多數測試結構和大多數探針。其優勢在於所需的設備相對便宜,大多數電子實驗室都可以直接找到。但是,它也有一些缺點,例如它的校正方法不如射頻測量中使用的校正方法那樣精確。另外一個明顯的缺點是要求交流阻抗的測試頻率必須接近DUT的工作頻率,否則必須內插一些測量結果。

儘管準靜態C-V是最所有測量方法中最廉價的,其中只需要使用一對SMU,但是它適用的技術範圍是有限的,例如低漏流[12]高k材料、有機器件或顯示器領域。不幸的是,在準靜態C-V測量中,測量誤差[13]很容易破壞測量結果,尤其對於具有少量漏流器件的特徵分析是不準確的。

射頻C-V測量是超薄柵、漏電電介質特徵分析的最佳選擇。它還適用於射頻器件的建模。射頻探針[14]的矯正方法很容易理解和實現。射頻方法的不足之處在於它需要非常昂貴的設備、測試結構和射頻探針;此外,它只適用於特徵阻抗為50歐姆左右的傳輸線。如果器件阻抗並不是十分接近50歐姆,這種方法就不準確了。對於某些套用和用戶而言,射頻測量的配置和分析過程可能太複雜了;在這些情況下,經典的交流阻抗測量方法可能更適合。

局限性

在探討C-V測試系統的配置方法之前,了解半導體C-V測量技術[15]的局限性是很重要的:

· 電容:從<10fF到1微法

· 電阻:從<0.1歐姆到100M歐姆

· 小電感:從<1nH到10mH

· 柵介質:可以提取的等價柵氧厚度範圍從不到10納米到幾百納米。可以檢測出的電介質玷污濃度從每平方厘米5e9個離子到約1e13個離子,界面阱範圍從約1e10/cm/ev到1e13/cm電荷左右(取決於器件結構)。現代儀器和探針台的超低電容測量功能能夠測量更厚的疊層電介質。

· MOS摻雜:可以提取MOSFET的摻雜分布情況,靈敏度範圍從約1e14/cm 到1e18/cm,摻雜深度從0.01µm到10µm。少數載流子壽命從1µs到10ms。可從C-V測量中測得10µs的壽命時間。

· PN和肖特基結摻雜:可在0.1µm 到100µm的深度範圍內測出約1e 13/cm t到1e18/cm的二極體載流子濃度。

· FET和BJT建模參數:除了測量器件和材料特性之外,C-V測試還可進行直接測量用於構建FET和BJT電晶體[16]中的參數。

重要的是要注意很多因素都會影響這些參數提取範圍,例如最大電壓值、器件尺寸和柵氧厚度。幸運的是,已有很多文獻能夠幫助廣大研究人員和工程師判斷所需的測量範圍是否與現在的C-V測量技術所具有的功能很好的匹配。

測量誤差

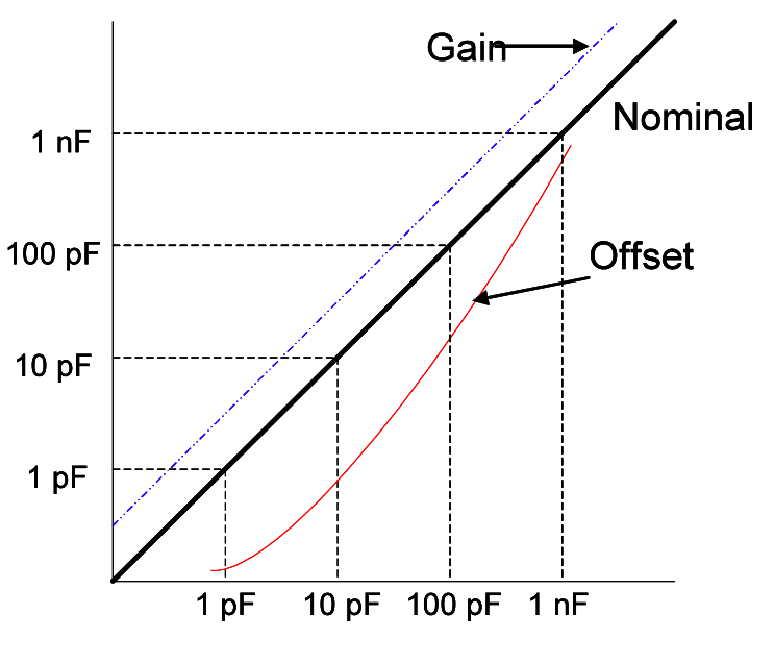

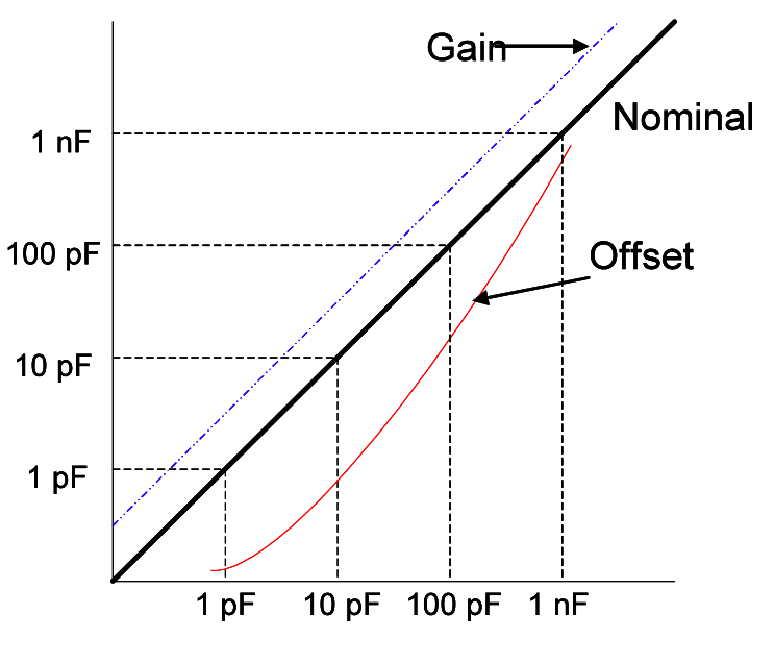

X軸以對數標度的方式給出了電容的真實值,大小範圍從皮法到納法。Y軸表示系統實際測量的值,包含測量誤差。如果測量系統是理想的,那么所測出的值將與真實值完全匹配,可以畫成一條具有45度角的直線,如圖4中黑色的線所示。實際上,增益和偏移誤差(藍線和紅線)總是會出現,必須進行校正。

增益、額定值、偏移量

圖4. 電容測量中的增益和偏移誤差[20] 圖4

圖4

圖4

圖4由於坐標軸是對數形式的,因此藍線所示的偏移誤差就表示小電容上的小誤差以及大電容上的大誤差。由於偏移誤差變化這么大,校正這種誤差必須注意兩個方面。當測量很小的電容(<10pF),即大阻抗時,最好的校正方法是“開路校正”。當測量較大的電容(高達10nF),即小阻抗時,最好採用“短路校正”。

圖4中還給出了增益誤差,以紅線所示。增益誤差的變化取決於所測電容的大小,它們相比偏移誤差更難以校正。“負載校正”是校正增益誤差的一種方法,實際上不適用於一般的實驗室套用。

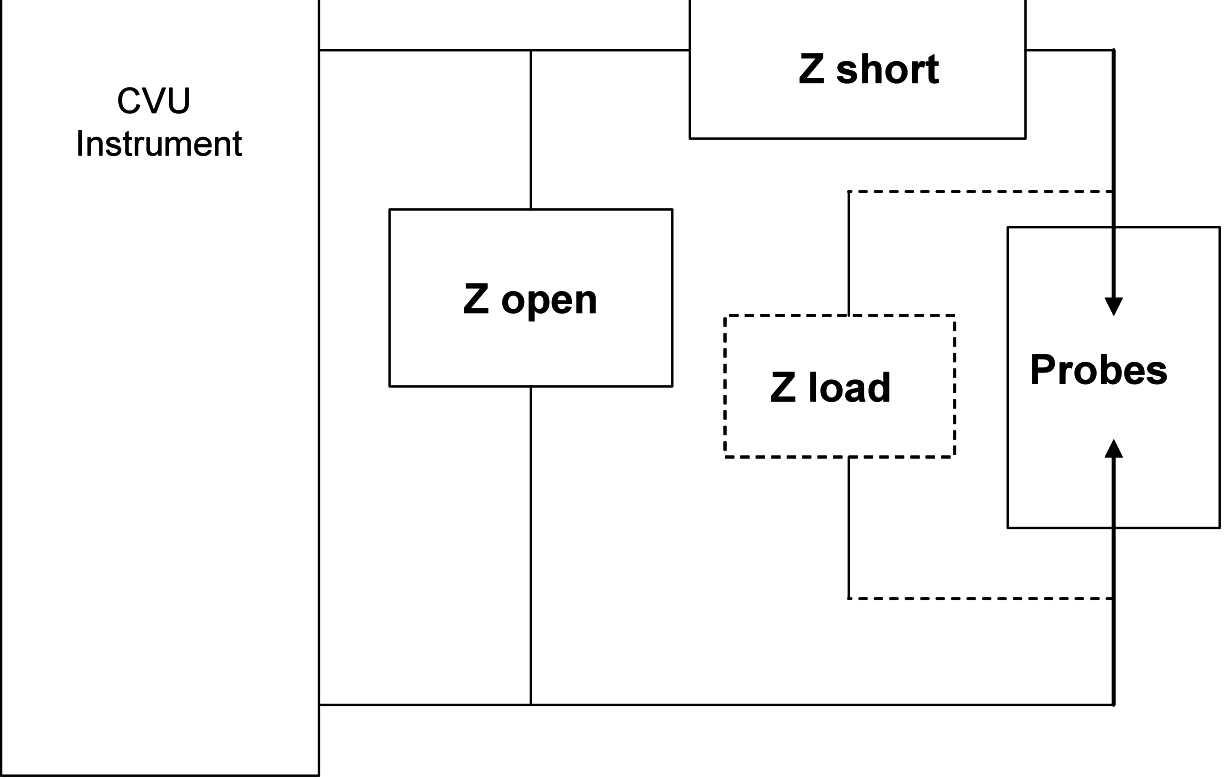

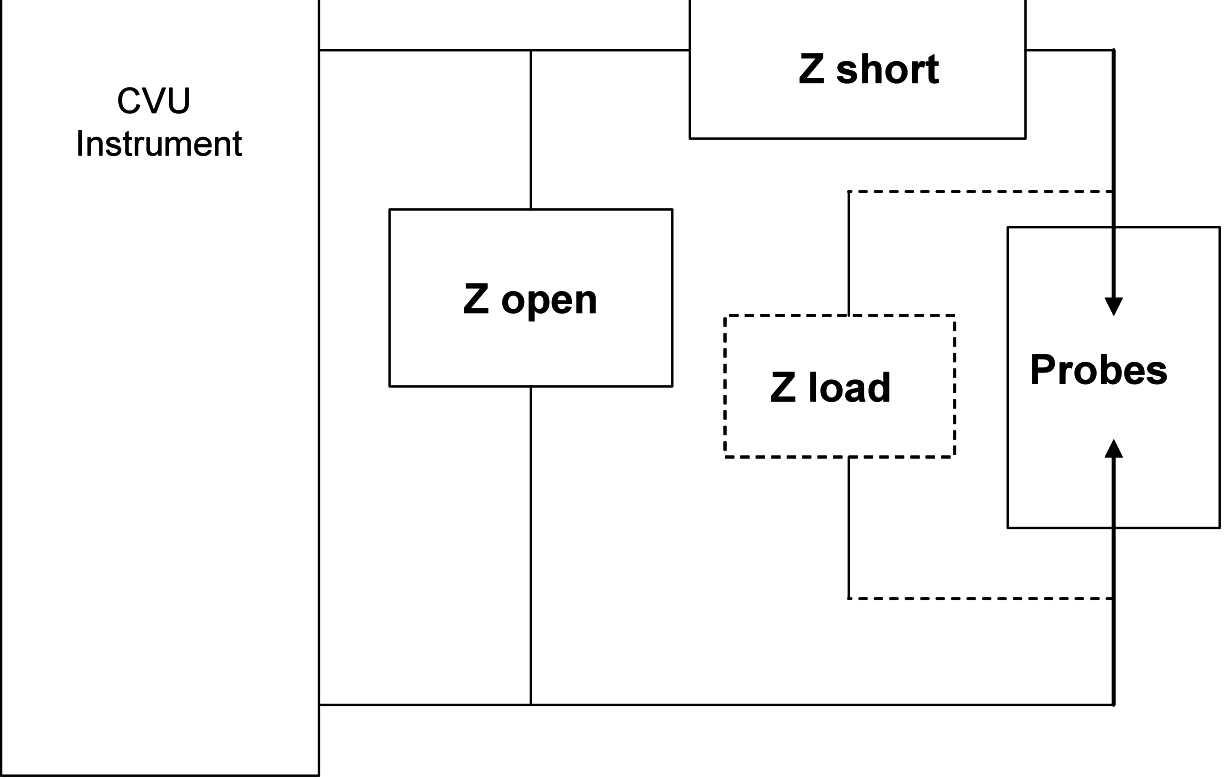

CVU儀器[21] 、Z短路、Z開路、Z負載 、探針

圖5. 圖5

圖5

圖5

圖5開路、短路和負載校正實際上是在乾什麼?圖8給出了一個交流阻抗測試[22]系統的簡化模型,其中添加了集總元件表示開路、短路和負載誤差項。測量系統的所有組成部分——所有線纜、所有探針和所有卡盤——已集總在一起,表示為Z開路(開路阻抗誤差)、Z短路(短路電路阻抗誤差)和Z負載(負載校正組件)。在這個測試系統上進行校正的第一步是在探針之間形成短路,通常做法是將兩個探針頭放在同一個接觸pad上。然後用電容計測量電容值,並將其保存為剩餘短路阻抗。第二步是抬起探針,使其保持在接近測量實際器件時應有的方向。然後電容計測量電容值,將其保存為剩餘開路阻抗。如果需要,可以在探針之間加一個已知的阻抗負載,用電容計測量其值,將其保存為負載校正。

不同的線纜類型和線纜阻抗[23]也會帶來問題。

技術連線

直流I-V測量[25]最好採用低噪聲同軸線纜和遠程探測線。C-V測量需要使用具有遠程探測線的同軸線纜,而且線纜長度要控制的非常精確。超快I-V測試需要50歐姆的同軸線纜,但是遠程探測線卻給超快I-V測試帶來了阻抗失配的問題。射頻C-V測量需要使用特殊的射頻線纜和“地-信號-地”結構的探針以及校準基座。但不幸的是,這些接線方法與其它方法都不兼容。

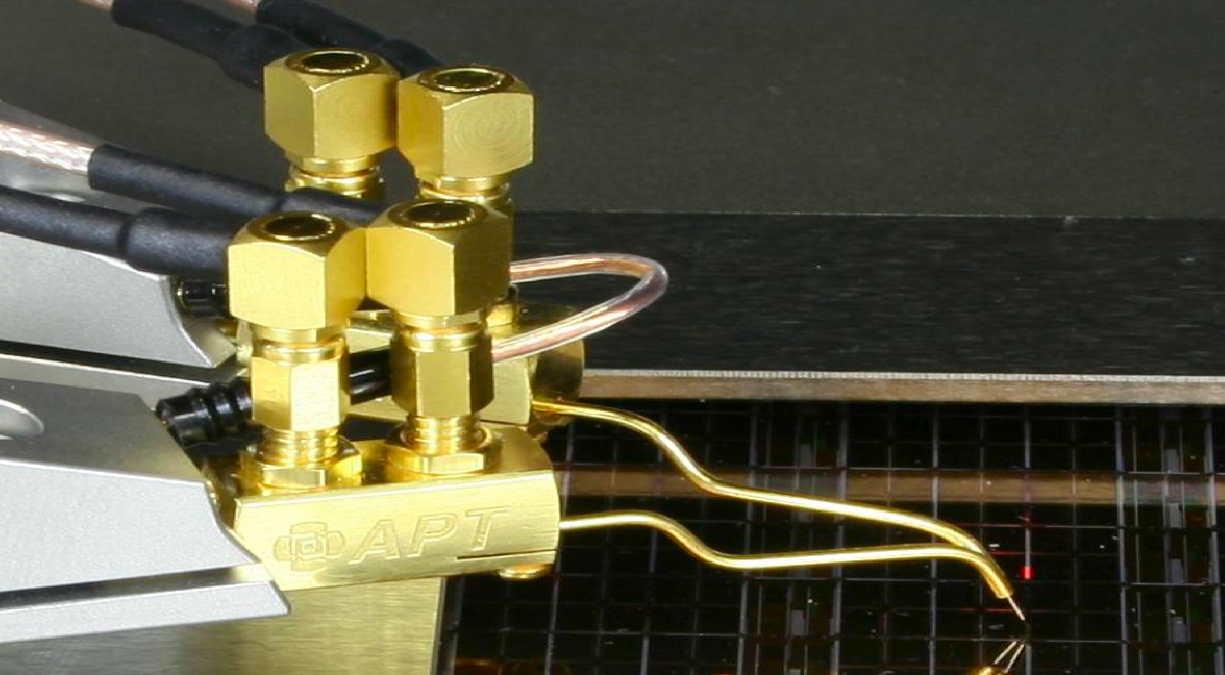

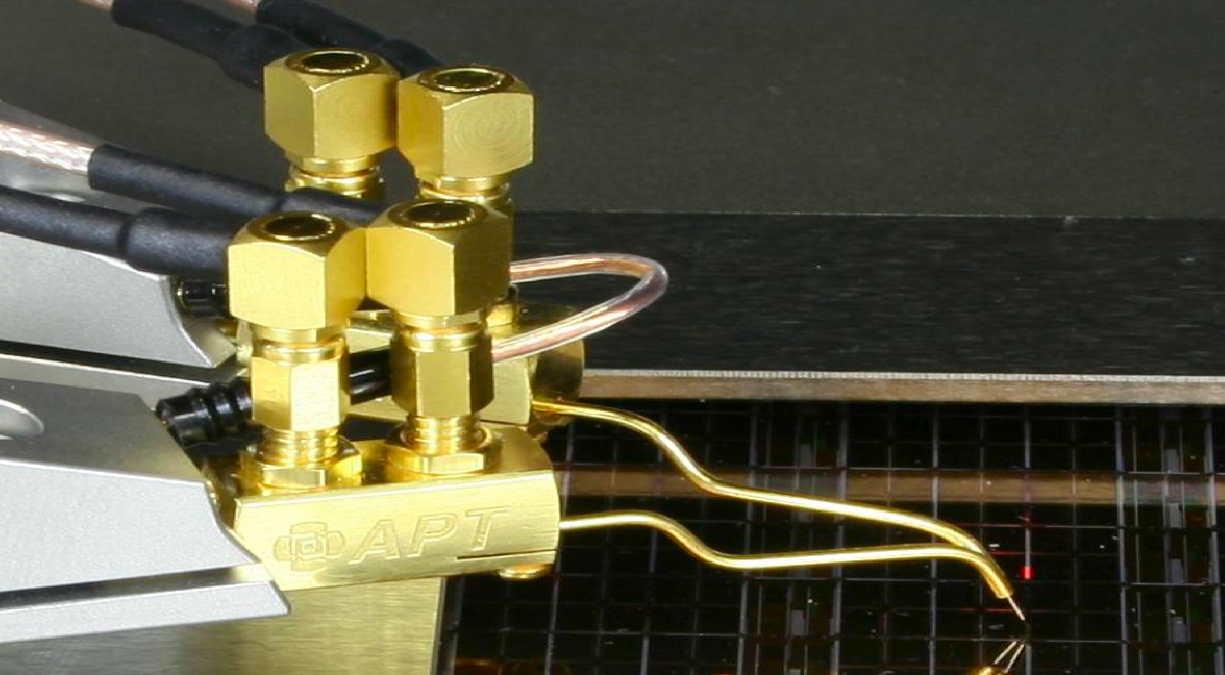

圖6. American Probe & Technologies的探頭配置 圖6

圖6

圖6

圖6通過吉時利[26]實驗室中的實驗,我們選擇了American Probe & Technologies公司提供的探頭配置(73系列或74系列)(如圖6所示),它的優勢在於大多數探針台供貨商都有供貨。這種特製的探頭是同軸的,帶有一個開氏連線。其主體和禁止層都是浮空的,因此可用作I-V測量的驅動保護,或者通過跳接實現C-V和超快I-V測量的短接地路徑。這類探針上的接頭稱為SSMC。有三類線纜可用於實現與這類探針的高品質連線:SSMC到三軸線纜連線適用於直流I-V測量和一般性套用(直接或間接連線),SSMC到同軸線纜連線可用於C-V或超快I-V測試[27](間接連線),而更特殊的SSMC到SMA線纜連線能夠實現最佳的C-V測量性能,尤其是在較高頻率下(直接連線)。圖6給出了進行C-V測量的雙探針配置方案;每個探針連線了一對同軸線纜,實現遠程開氏檢測連線。注意兩個探頭體之間的跳線很短。這種跳線確保了探針之間具有良好的接地連線,這對於高頻測量是很重要的。

技術分享

C-V吉時利全新接線技術

圖7. 跳接同軸線[28]禁止層示意圖 圖7

圖7

圖7

圖7好的C-V測量取決於接地跳線的質量。隨著頻率的提高,好的接地跳線變得愈發重要。探頭體必須跳接在一起,因為同軸線纜的禁止層實際上是C-V測試系統測量通路的一部分。如果禁止層沒有靠近連線在一起,就會形成一個很大的迴路,從而在測量通路中直接產生較大的電感,給電容測量帶來很大的誤差。

當有人想要採用與C-V測量系統相同的探針和線纜系統配置進行直流I-V測量時,按這種方式(如圖7所示)跳接探針體[29]的缺點就顯而易見了。

圖8. 新方法簡化了I-V、C-V和超快I-V測試連線配置 圖8

圖8

圖8

圖8吉時利研究出了一種新的接線技術(如圖6所示)能夠減少在I-V、C-V和超快I-V測試之間轉換所需的重新連線時間。這種技術採用一種特殊的三軸線纜直接連線探頭,但是內部禁止層保持浮空或者與C-V同軸禁止層絕緣。這實際上是將外部禁止層跳接在了一起,保持內部禁止層浮空為直流I-V的驅動保護。這種三軸接頭實現了一種簡便而直接的與直流I-V三軸輸出端的連線方式。C-V輸出從同軸轉換為三軸,保護端仍然斷開,從而同一條線纜很容易從直流I-V轉換到C-V測試端。這種特製的三軸線纜具有100歐姆的匹配阻抗,因此同樣的線纜可以採用T型連線方式連線在一起,直接與超快I-V測試儀器[30]連線。這種配置使得禁止層跳線始終保持連線,能夠快速而簡便地實現直流I-V、C-V和超快I-V測試之間的轉換。

半導體C-V測量的精確性取決於高精度的測試儀器、精心設計的布線結構以及對這些底層測量原理的準確理解。在掌握這些方面之後,您就可以設計出能夠滿足測試套用需求的硬體和布線結構。