非阻塞賦值操作符用小於等於號(即<=)表示,由時鐘節拍決定,在時鐘上升到來時,執行賦值語句右邊,然後將begin-end之間的所有賦值語句同時賦值到賦值語句的左邊。非阻塞賦值允許其他的Verilog語句同時進行操作。

基本介紹

- 中文名:非阻塞賦值

- 外文名:nonblocking assignment

- 特點:允許其他的Verilog語句同時操作

- 操作費用:小於等於號(即

- 使用場景:描述時序邏輯的always塊

- 套用學科:機械工程、儀器科學、計算機科學

非阻塞賦值操作符用小於等於號(即<=)表示,由時鐘節拍決定,在時鐘上升到來時,執行賦值語句右邊,然後將begin-end之間的所有賦值語句同時賦值到賦值語句的左邊。非阻塞賦值允許其他的Verilog語句同時進行操作。

非阻塞賦值操作符用小於等於號(即<=)表示,由時鐘節拍決定,在時鐘上升到來時,執行賦值語句右邊,然後將begin-end之間的所有賦值語句同時賦值到賦值語句的左邊。非阻塞賦值允許其他的Verilog語句同時進行操作...

對組合邏輯器件的賦值採用阻塞賦值“=”時序邏輯器件的賦值語句採用非阻塞賦值“語法上,沒有關鍵字“assign”;左側被賦值的數據類型必須是暫存器類型的變數(reg);過程性連續賦值語句只能出現在過程塊中;過程性連續賦值語句主要用來對...

在數據流描述方式中,還必須藉助於HDL提供的一些運算符,如按位邏輯運算符:邏輯與(&),邏輯或(|)等。對數據流的建模方式主要有連續賦值語句、阻塞賦值語句、非阻塞賦值語句等。實例 wire [3:0] Z, Preset, Clear; //線網說明...

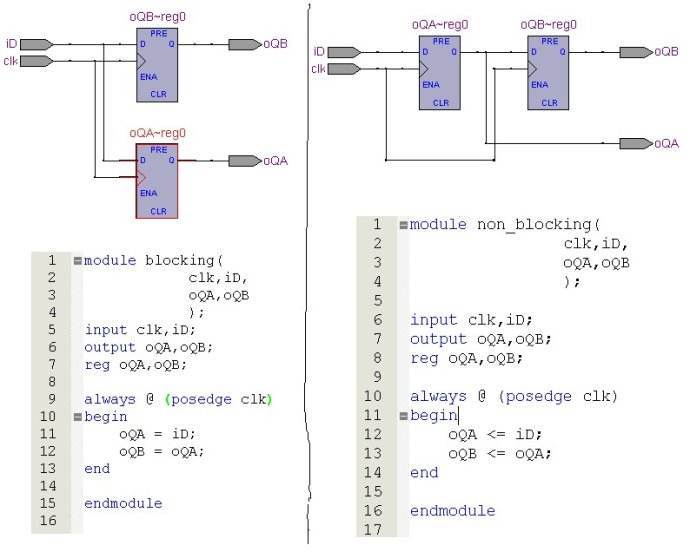

在Verilog中,有兩種賦值運算,一種叫做阻塞賦值(blocking assignment),其運算符為=;另一種叫做非阻塞賦值(non-blocking assignment),其運算符為 帶有兩個觸發器輸出端的簡單示例如下 always @ (posedge reset or posedge clock)beg...

阻塞賦值;計算非阻塞賦值語句右邊的表達式;連續賦值;執行$display命令;計算原語的輸入和輸出的變化。停止運行的事件佇列 停止運行的事件佇列:#0延時阻塞賦值。非阻塞事件佇列 非阻塞事件佇列:更新非阻塞賦值語句LHS(左邊變數)的值。監控...

14.6 阻塞賦值及一些簡單的例子 14.7 時序反饋移位暫存器建模 14.8 組合邏輯建模時應使用阻塞賦值 14.9 時序和組合的混合邏輯——使用非阻塞賦值 14.10 其他阻塞和非阻塞混合使用的原則 14.11 對同一變數進行多次賦值 14.12 常見...

5.3.2阻塞賦值與非阻塞賦值 5.4條件語句 5.4.1ifelse語句 5.4.2case語句 5.5循環語句 5.5.1for語句 5.5.2repeat、while、forever語句 5.6編譯指示語句 5.7任務與函式 5.7.1任務 5.7.2函式 5.8Verilog2001語言...

5.15 阻塞和非阻塞賦值 5.16 函式的綜合 5.17 任務的綜合 5.18 任意值/高阻的綜合 第6章 設計驗證 6.1 后綜合設計驗證 6.1.1 基於仿真的驗證 6.1.2 形式化驗證 6.2 面向驗證的編碼風格 6.2.1 功能正確性 6...

4.7.2 非阻塞性賦值語句 72 4.8 套用實例 74 實例4-1—4位全加器的行為級建模 74 實例4-2—簡易ALU電路的行為級建模 75 實例4-3—下降沿觸發D觸發器的行為級建模 77 實例4-4—十進制計數器的行為級建模 78 4....

6-1 阻塞賦值與非阻塞賦值 6-2 不完整條件語句與時序電路的關係 6-3 If與case 6-4 三態的Verilog描述 6-5 雙向連線埠設計 6-6 庫元件和UDP用法 08 實驗2:正弦波信號發生器 能夠使用ROM模組設計一個正弦波信號發生器,能夠使用...

5.6 賦值語句 5.6.1 常用的賦值語句 5.6.2 阻塞賦值和非阻塞賦值的區別 5.7 條件語句 5.7.1 if-else語句 5.7.2 case語句 5.7.3 使用條件語句的注意事項 5.8 循環語句 5.8.1 for語句 5.8.2 repeat語句 5.8.3 ...

5.1 阻塞賦值和非阻塞賦值 120 5.2 觸發器電路設計 124 5.2.1 時序電路概念 124 5.2.2 D觸發器 124 5.3 計數器電路設計 127 5.3.1 基本同步計數器 127 5.3.2 具有復位連線埠的計數器 128 5.3.3 具有置...

第13章 阻塞賦值與非阻塞賦值 13.1 理論學習 13.2 阻塞賦值 13.3 非阻塞賦值 13.4 章末總結 第14章 計數器 14.1 理論學習 14.2 實戰演練 14.3 章末總結 第15章 分頻器 15.1 理論學習 15.2 實戰演練一 15....

6.3 賦值語句 148 6.3.1 持續賦值與過程賦值 148 6.3.2 阻塞賦值與非阻塞賦值 149 6.4 條件語句 151 6.4.1 if-else語句 151 6.4.2 case語句 152 6.5 循環語句 157 6.5.1 for語句 157 6.5.2 repeat...

6.3 賦值語句 122 6.3.1 持續賦值與過程賦值 122 6.3.2 阻塞賦值與非阻塞賦值 123 6.4 條件語句 125 6.4.1 if-else語句 125 6.4.2 case語句 126 6.5 循環語句 130 6.5.1 for語句 131 6...

5.4 賦值語句 5.4.1 持續賦值與過程賦值 5.4.2 阻塞賦值與非阻塞賦值 5.5 條件語句 5.5.1 if-else語句 5.5.2 case語句 5.5.3 條件語句使用要點 5.6 循環語句 5.6.1 for語句 5.6.2 repeat語句 5.6.3 while和...

6.3 賦值語句144 6.3.1 持續賦值與過程賦值144 6.3.2 阻塞賦值與非阻塞賦值145 6.4 條件語句146 6.4.1 if-else語句147 6.4.2 case語句148 6.5 循環語句152 6.5.1 for語句153 6.5.2 repeat、while、forever語句154 ...

7.5.1 連續賦值語句 163 7.5.2 阻塞賦值語句 163 7.5.3 非阻塞賦值語句 164 7.5.4 數據流建模具體實例 165 7.6 行為建模 166 7.6.1 簡介 166 7.6.2 順序語句塊 166 7.6.3 過程賦值語句 166 7.7 可綜合設計 ...

5.7.1阻塞賦值和非阻塞賦值 5.7.2組合邏輯環 5.7.3異步信號的誤用 5.7.4門控時鐘的誤用 5.7.5導出時鐘的使用 5.8習題和思考題 第6章有限狀態機設計原理 6.1有限狀態機 6.1.1米利狀態機和摩爾狀態機 6.1.2邊沿檢測...

4.1.5觸發器設計中的非阻塞賦值語句109 4.1.6實驗內容111 4.2暫存器實驗111 4.2.1暫存器112 4.2.2移位暫存器113 4.2.3實驗內容113 4.3計數器實驗115 4.3.1加法計數器115 4.3.2減法計數器115 4.3.3實驗內容116 4.4...

6.3 賦值語句 147 6.3.1 持續賦值與過程賦值 147 6.3.2 阻塞賦值與非阻塞賦值 148 6.4 條件語句 149 6.4.1 if-else語句 150 6.4.2 case語句 151 6.5 循環語句 155 6.5.1 for語句 156 6.5.2 repeat、while、...

7.2隱含連續賦值 7.3延遲 7.4習題第8章行為級建模 8.1過程化結構 8.1.1initial語句 8.1.2always語句 8.2過程賦值 8.2.1等號右邊的延遲 8.2.2等號左邊的延遲 8.2.3阻塞賦值 8.2.4非阻塞賦值 8.3條件語句 8.4case...

第六講 深入理解阻塞和非阻塞賦值的不同 概述 6.1 深入理解阻塞和非阻塞賦值的不同 6.2 Verilog模組編程要點 6.3 Verilog的層次化事件佇列 6.4 自觸發always塊 6.5 移位暫存器模型 6.6 阻塞賦值及一些簡單的例子 6.7 時序反饋...

圖7.2非阻塞賦值方式的設計結果185 圖7.3阻塞賦值方式的設計結果185 圖8.1開發的基本過程圖223 圖8.2釋放安裝檔案224 圖8.3Quartus Ⅱ 9.0 Setup界面225 圖8.4License Agreement界面225 圖8.5填寫個人信息226 圖8.6選擇安裝...

4.3.1阻塞賦值、非阻塞賦值和連續賦值67 4.3.2暫存器電路建模68 4.3.3組合邏輯建模70 4.3.4雙向連線埠與三態信號建模72 4.3.5mux建模73 4.3.6存儲器建模74 4.3.7簡單的時鐘分頻電路75 4.3.8串並轉換建模77 4.3.9同步...

7.1.3未指定延時的非阻塞式賦值 175 7.1.4指定了延時的非阻塞式賦值 176 7.1.5深入認識阻塞式與非阻塞式賦值的特點 177 7.1.6不同的賦初值方式導致不同綜合結果的示例 179 7.2過程語句深入探討 181 7.2.1過程語句套用總結...

4.5.4阻塞賦值和非阻塞賦值124 4.6有限狀態機127 4.7數據類型*130 4.7.1SystemVerilog130 4.7.2VHDL131 4.8參數化模組*133 4.9測試程式135 4.10總結138 習題138 面試問題145 第5章數字模組146 5.1引言146 5.2算術電路...