在數字電路系統工作過程中,把正在處理的二進制數據或代碼暫時存儲起來的操作叫做暫存,暫存器電路就是實現暫存功能的電路,是數字邏輯電路的基礎模組。

基本介紹

- 中文名:暫存器電路

- 外文名:register circuit

- 拼音:jì cún qì diàn lù

- 定義:實現暫存功能的電路

- 屬性:數字邏輯電路的基礎模組

- 套用學科:計算機

套用領域

基本暫存器電路

定義

特點

工作原理

在數字電路系統工作過程中,把正在處理的二進制數據或代碼暫時存儲起來的操作叫做暫存,暫存器電路就是實現暫存功能的電路,是數字邏輯電路的基礎模組。

在數字電路系統工作過程中,把正在處理的二進制數據或代碼暫時存儲起來的操作叫做暫存,暫存器電路就是實現暫存功能的電路,是數字邏輯電路的基礎模組。套用領域任何現代的數字電路系統,特別是一些大型的數字處理系統,往往不可能一次性...

暫存器的存儲電路是由鎖存器或觸發器構成的,因為一個鎖存器或觸發器能存儲1位二進制數,所以由N個鎖存器或觸發器可以構成N位暫存器。暫存器是中央處理器內的組成部分。暫存器是有限存儲容量的高速存儲部件,它們可用來暫存指令、數據和...

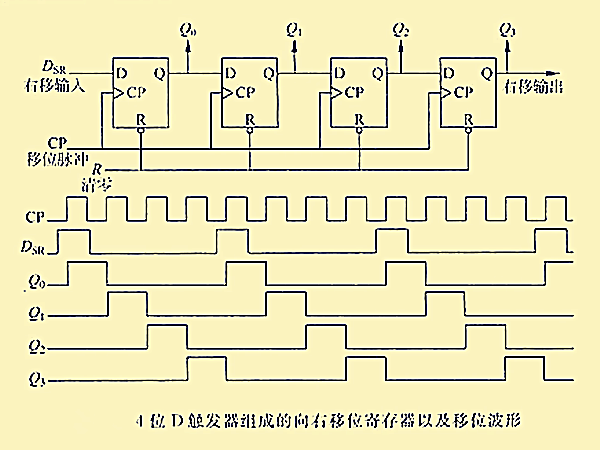

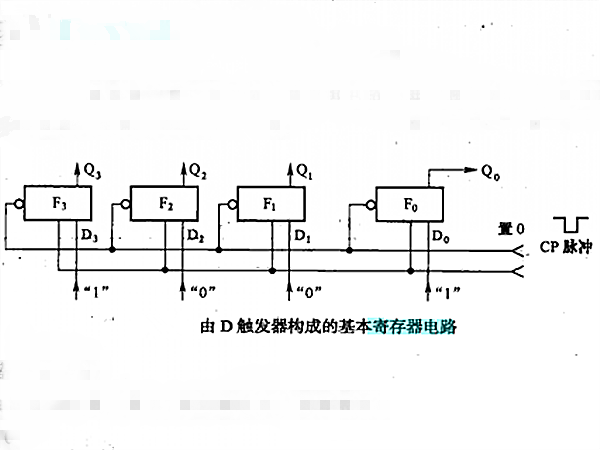

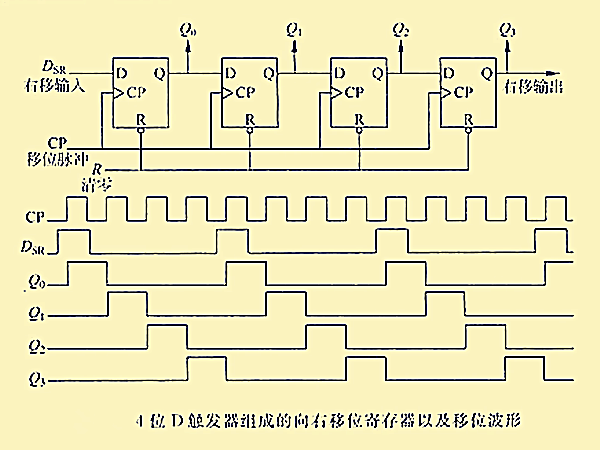

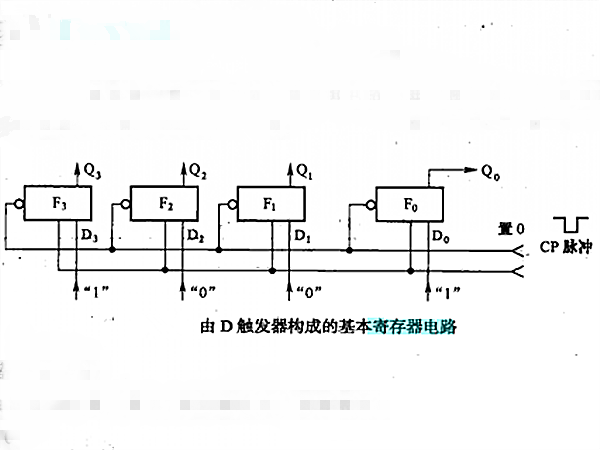

暫存器 暫存器:在實際的數字系統中,通常把能夠用來存儲一組二進制代碼的同步時序邏輯電路稱為暫存器。由於觸發器內有記憶功能,因此利用觸發器可以方便地構成暫存器。由於一個觸發器能夠存儲一位二進制碼,所以把n個觸發器的時鐘連線埠連線...

《一種移位暫存器單元及柵極驅動電路》是京東方科技集團股份有限公司和鄂爾多斯市源盛光電有限責任公司於2013年4月10日申請的專利,該專利的公布號為CN103226981A,申請號為2013101224151,授權公布日為2013年7月31日,發明人是李付強、李成...

《一種移位暫存器、柵極驅動電路和相關顯示裝置》是京東方科技集團股份有限公司、鄂爾多斯市源盛光電有限責任公司於2015年8月27日申請的專利,該專利的公布號為CN105185287A,授權公布日為2015年12月23日,發明人是張毅、馮宇、朱健超。《一...

在數位電路設計中,暫存器傳輸級(英語:register-transfer level, RTL)是一種對同步數位電路的抽象模型,這種模型是根據數位訊號在硬體暫存器、存儲器、組合邏輯裝置和匯流排等邏輯單元之間的流動,以及其邏輯代數運作方式來確定的。簡介 暫存...

在數字電路中,用來存放二進制數據或代碼的電路稱為暫存器。暫存器是由具有存儲功能的觸發器組合起來構成的。一個觸發器可以存儲一位二進制代碼,存放N位二進制代碼的暫存器,需用n個觸發器來構成。按功能可分為:基本暫存器和移位暫存器。

常用數字集成電路集錦是各種常用數字積體電路的匯集。常用數字積體電路包括門電路、觸發器、時基延時分頻電路、計數器、解碼器、模擬開關數據選擇器、暫存器、運算電路、編碼電路編解碼配對電路、遙控電路、頻率合成電路。門電路 四2輸入或非門...

數字電路中,信號大小為不連續並定量化的電壓狀態。多數採用布爾代數邏輯電路對定量後信號進行處理。典型數字電路有,振盪器、暫存器、加法器、減法器等。運算不連續性定量電信號。·積體電路亦稱為IC (Integrated Circuit )。·運用集成...

這種延時電路廣泛套用於雷達、通信和各種控制系統的定時裝置,可利用各種脈衝電路來實現。常用的有鋸齒波延時電路和移位暫存器延時電路。鋸齒波延時電路 圖1為這種電路的原理框圖和波形。電路工作時,輸入脈衝Ui的前沿啟動鋸齒電壓發生器,使...

暫存器是有限存貯容量的高速存貯部件,它們可用來暫存指令、數據和地址。暫存器分配程式是指對暫存器的分配、回收以及提供在存儲層次間的數據移動的管理機制的程式。暫存器,是集成電路中非常重要的一種存儲單元,通常由觸發器組成。在積體電路...

介紹了40mn工藝下一款16x36b7讀6寫的暫存器檔案全定製設計,採用讀寫陣列分離策略,支持32位和36位兩種寫入操作。為了解決多個讀連線埠讀同一地址時讀出過慢的問題,提出了一種基於與或非邏輯搭建的16選1讀出電路。讀寫陣列分離的套用,...

此外,帶緩衝器的門電路還有輸出波形對稱、交流電壓增益大、頻寬窄、輸入電容比較小等優點。不過,由於附加了緩衝級,也帶來了一些缺點。例如傳輸延遲時間加大,因此,帶緩衝器的門電路不適宜用在高速電路系統中。背景知識 緩衝暫存器又稱...

SCON串列口控制暫存器通常在晶片或設備中為了監視或控制接口狀態,都會引用到接口控制暫存器。SCON 就是51 晶片的串列口控制暫存器。它的定址地址是98H,是一個可以位定址的暫存器,作用就是監視和控制51 晶片串列口的工作狀態。51 晶片的...

DX(data)數據。可以作為通用暫存器使用。一般在作雙字長運算時把DX和AX組合在一起存放一個雙字長數,DX用來存放高位數。對於某些I/O操作,DX可用來存放I/O的連線埠地址。暫存器 暫存器,是集成電路中非常重要的一種存儲單元,通常由觸發...

時序邏輯電路中最常見的是暫存器、移位暫存器、計數器、順序脈衝發生器和序列信號發生器,時序邏輯電路的設計方法是建立在組合邏輯電路漫計方法的基礎之上的。在設計時序邏輯電路時,要求設計者根據給出的具體邏輯問題,求出實現這一邏輯功能...

所謂時序邏輯電路是指在數字電路中,凡是任一時刻的穩態輸出不僅取決於該時刻的輸入,而且還和電路原來狀態有關。例如計算機的計數器、暫存器、順序脈衝發生器等均屬於時序邏輯電路。組合邏輯電路的設計方法 電路的設計過程:1、假設兩個相加...

2.暫存器 暫存器是存放數碼、運算結果或指令的電路,移位暫存器不但可存放數碼,而且在移位脈衝作用下,暫存器中的數碼可根據需要向左或向右移位。暫存器和移位暫存器是數字系統和計算機中常用的基本邏輯部件,套用很廣。一個觸發器可存儲一位二...

電路分類 電路類型TTL數字積體電路約有400多個品種,大致可以分為以下幾類:門電路 解碼器/驅動器 觸發器 計數器 移位暫存器 單穩、雙穩電路和多諧振盪器 加法器、乘法器 奇偶校驗器 碼制轉換器 線驅動器/線接收器 多路開關 存儲器 ...

三態輸出電路邏輯表如下表所示:匯流排結構 在微型計算機中,各部件之間的信息傳送都是經過匯流排來傳輸的。匯流排是若干條公用的線,它可以被各部件分時使用,從而實現各部件之間的信息傳送。在這裡,我們將以暫存器為例,說明暫存器之間的數據...

由於在記憶體和CPU之間存在著操作速度上的差別,所以必須使用地址暫存器來保持地址信息,直到記憶體的讀/寫操作完成為止。數據暫存器DR用來暫存微處理器與存儲器或輸人/輸出接口電路之間待傳送的數據。地址暫存器AR和數據暫存器DR在微處理器的內部...

(2)用T觸發器構成的同步二進制加法計數器,其電路結構有兩條規則:(3)同步計數器工作速度快,這種計數器的最高工作頻率可達:暫存器和移位暫存器 暫存器 暫存器用途:暫時存放二進制數碼。暫存器作為一個邏輯部件來使用,一般都包含有...

邊界掃描暫存器電路僅在進行JTAG 測試時有效,在積體電路正常工作時無效,不影響積體電路的功能。接口解讀 JTAG接口解讀 通常所說的JTAG大致分兩類,一類用於測試晶片的電氣特性,檢測晶片是否有問題;一類用於Debug;一般支持JTAG的CPU內都...

套用電路圖 採用DAC0832實現D/A轉換。DAC0832引腳功能說明:DI0~DI7:數據輸入線,TTL電平。ILE:數據鎖存允許控制信號輸入線,高電平有效。CS:片選信號輸入線,低電平有效。WR1:為輸入暫存器的寫選通信號。XFER:數據傳送控制信號輸入...

//***定義ISD1700狀態暫存器及各標誌位***// uchar bdata SR0_L;//SR0暫存器低位、高位 uchar bdata SR0_H;uchar bdata SR1;//SR1暫存器 uchar APC_L = 0, APC_H = 0;//APC暫存器 uchar PLAYADDL = 0, PLAYADDH ...

時序邏輯電路其任一時刻的輸出不僅取決於該時刻的輸入,而且還與過去各時刻的輸入有關。常見的時序邏輯電路有觸發器、計數器、暫存器等。時序邏輯電路在邏輯功能上的特點是任意時刻的輸出不僅取決於當時的輸入信號,而且還取決於電路原來的...