基本介紹

- 中文名:時序邏輯系統

- 外文名:sequential logic system

- 學科:計算機科學與技術

- 類別:數字邏輯系統

- 分類:同步、異步

- 套用:計數器、暫存器

基本概念

時序邏輯電路

時序邏輯電路其任一時刻的輸出不僅取決於該時刻的輸入,而且還與過去各時刻的輸入有關。常見的時序邏輯電路有觸發器、計數器、暫存器等。時序邏輯電路在邏輯功能上的特點是任意時刻的輸出不僅取決於當時的輸入信號,而且還取決於電路原來...

時序邏輯被用來描述為表現和推理關於時間限定的命題的規則和符號化的任何系統,主要用於形式驗證。20世紀60年代Arthur Prior提出介入的基於模態邏輯的特殊的時間邏輯系統,這一理論後來被艾米爾 伯努利等邏輯學家進一步發展。後來,Pnueli在...

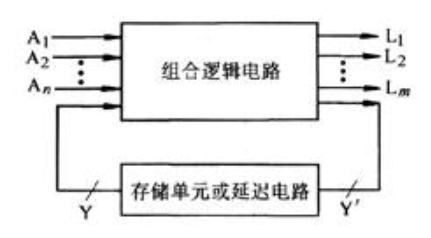

雖然每個數字電路系統可能包含有組合電路,但是在實際套用中絕大多數的系統還包括存儲元件,我們將這樣的系統描述為時序電路。時序電路,是由最基本的邏輯門電路加上反饋邏輯迴路(輸出到輸入)或器件組合而成的電路,與組合電路最本質的區別...

時序邏輯是指輸出不但和當前輸入的邏輯值有關,而且和在此以前曾經輸入過的邏輯值有關的邏輯系統。異步時序邏輯是電路的工作節奏不一致,不存在單一的主控時鐘,主要是用於產生地址解碼器、FIFO和異步RAM的讀寫控制信號脈衝。除可以使用帶...

順序脈衝是指在每個循環周期內,在時間上按一定先後順序排列的脈衝信號。產生順序脈衝信號的電路稱為順序脈衝發生器。在數字系統中,常用以控制某些設備按照事先規定的順序進行運算或操作。特點 時序邏輯電路其任一時刻的輸出不僅取決於該時刻...

行為時序邏輯(The Temporal Logic of Actions)是由萊斯利·蘭伯特(Leslie Lamport)發展的用於規範和推理並發自反應系統的時間邏輯。 主要套用於計算機科學,程式驗證。萊斯利·蘭波特 萊斯利·蘭波特(英語:Leslie Lamport,1941年2月7日-...

時序電路是計算機及其它電子系統中常用的一種電路。它和組合電路是完全不同的兩種類型電路。時序電路分為兩大類:同步時序邏輯電路和異步時序邏輯電路。在同步時序邏輯電路中有一個公共的時鐘信號,電路中各記憶元件受它統一控制,只有在該...

《時序邏輯程式設計與軟體工程(下)》是科學出版社出版的圖書,作者是唐稚 松 內容簡介 《時序邏輯程式設計與軟體工程(下)》旨在介紹一種面向軟體工程的時序邏輯語言(XYZ/E)及以該語言為基礎的支撐軟體開發全過程的軟體工程系統(XYZ...

《框架時序邏輯程式設計》是依託西安電子科技大學,由段振華擔任項目負責人的重點項目。中文摘要 定義框架時序邏輯的語法和語義,建立該邏輯系統的模型理論,公理系統;基於該邏輯系統,開發一個簡潔、實用的、具有類似於C,C++ 和Java語言的...

數字積體電路有各種門電路、觸發器以及由它們構成的各種組合邏輯電路和時序邏輯電路。一個數字系統一般由控制部件和運算部件組成,在時脈的驅動下,控制部件控制運算部件完成所要執行的動作。通過模擬數字轉換器、數字模擬轉換器,數字電路可以...

(1) 由實際邏輯問題列出真值表;(2) 由真值表寫出邏輯表達式;(3) 化簡、變換輸出邏輯表達式;(4) 畫出邏輯圖。運算單元 在數字系統中算術運算都是利用加法進行的,因此加法器是數字系統中最基本的運算單元。由於二進制運算可以用邏輯...

為此,我們在建模、仿真和驗證語言(MSVL)的基礎上引入類型的概念,並定義多種類型,得到一種多類型時序邏輯程式設計語言:多類型MSVL。研究多類型MSVL的類型系統、模型語義、操作語義、公理語義、類型安全性和語義之間等價性。開發多類型...

數字邏輯不考慮特殊條件下動作或穩定的物理現象和從一個狀態過渡到另一個狀態的細節。數字邏輯 數字邏輯的部分理論建立在數理邏輯,特別是布爾代數和時序機的理論基礎上。數字邏輯可分為組合邏輯和時序邏輯。在一個邏輯系統中,輸出結果僅...

一種典型的環形脈衝發生器及其解碼邏輯,它採用循環移位暫存器形式。時序產生器套用 用於測試系統 基於向量測試法的測試系統的原理、結構組成以及各功能模組的工作過程。有關技術人員在總結多年的實際測試經驗並參考國外同類測試系統的基礎上...

用數位訊號完成對數字量進行算術運算和邏輯運算的電路稱為數字電路,或數字系統。由於它具有邏輯運算和邏輯處理功能,所以又稱數字邏輯電路。現代的數字電路由半導體工藝製成的若干數字集成器件構造而成。邏輯門是數字邏輯電路的基本單元。存儲...

本書從數字電路的基礎知識出發,介紹數制和編碼、邏輯代數、門電路、組合邏輯、時序邏輯、硬體描述語言(VHDL)、可程式器件(PLD、CPLD、HDPLD和FPGA)、在系統編程技術(ISP)及EDA技術的設計思想等內容。用VHDL硬體描述語言來描述電路的...

8.5.3 單片機系統中常用的存儲器擴展 技術 273 8.6 ROM和RAM綜合套用舉例 274 8.6.1 用存儲器實現組合邏輯函式 274 8.6.2 用存儲器實現時序邏輯功能 277 8.7 本章小結 278 習題 278 第9章 可程式邏輯器件簡介 281 9.1 ...

應避免引線過長,以防止信號之間的竄擾和 對信號傳輸的延遲。此外要把電源線設計得寬一些,地線要進行大面積接地,這樣可減少接地噪聲干擾。 在CMOS邏輯系統設計中,應儘量減少電容負載。電容負載會降低CMOS積體電路的工作速度和增加功耗。

在數字電路系統工作過程中,把正在處理的二進制數據或代碼暫時存儲起來的操作叫做暫存,實現暫存功能的電路稱為暫存器。暫存器是一種最基本的時序邏輯電路,在各種數字電路系統中幾乎是無所不在,使用非常廣泛。常用的積體電路暫存器按能夠暫存...