時序邏輯電路其任一時刻的輸出不僅取決於該時刻的輸入,而且還與過去各時刻的輸入有關。常見的時序邏輯元件有觸發器、計數器、暫存器等。由於時序邏輯電路具有存儲或記憶的功能,檢修起來就比較複雜。

基本介紹

- 中文名:時序邏輯元件

- 外文名:sequential logic element

- 學科:電子、通信與自動控制技術

- 類別:時序邏輯電路

- 分類:觸發器、計數器、暫存器

- 特點:輸出與以前的輸入有關

基本概念

計數器

異步計數器

同步計數器

時序邏輯電路其任一時刻的輸出不僅取決於該時刻的輸入,而且還與過去各時刻的輸入有關。常見的時序邏輯元件有觸發器、計數器、暫存器等。由於時序邏輯電路具有存儲或記憶的功能,檢修起來就比較複雜。

時序邏輯電路其任一時刻的輸出不僅取決於該時刻的輸入,而且還與過去各時刻的輸入有關。常見的時序邏輯元件有觸發器、計數器、暫存器等。由於時序邏輯電路具有存儲或記憶的功能,檢修起來就比較複雜。基本概念數字電路根據邏輯功能的不同...

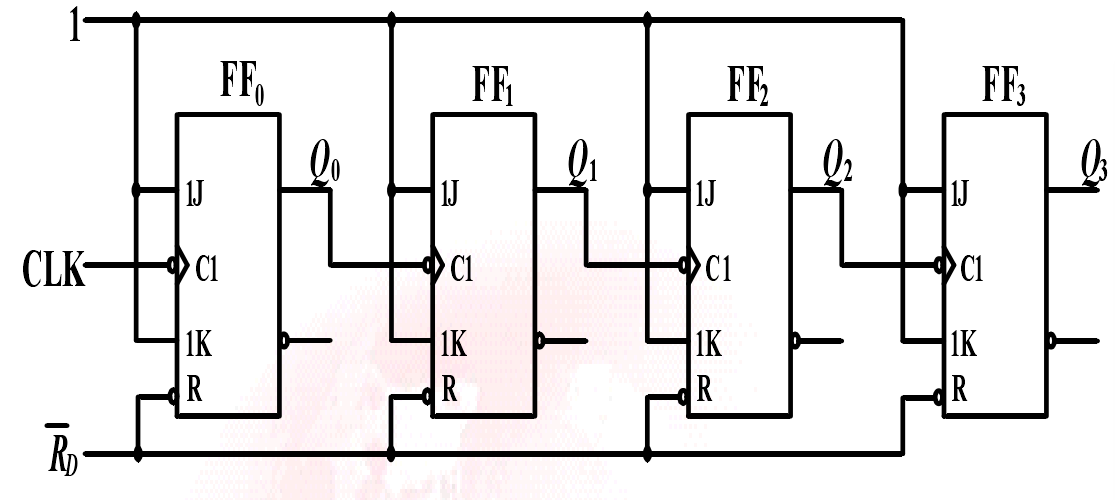

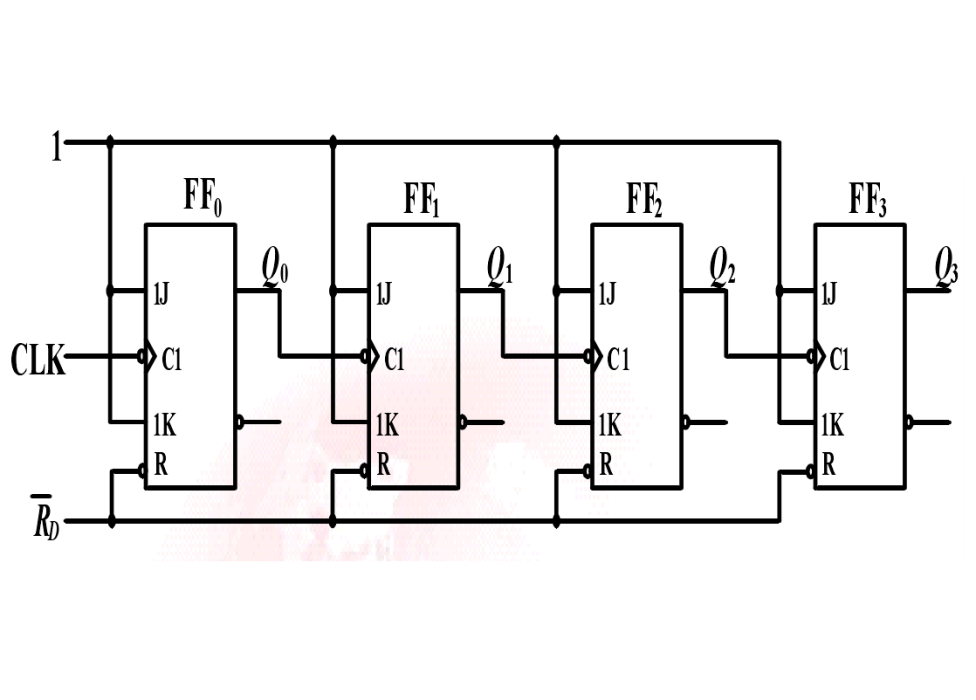

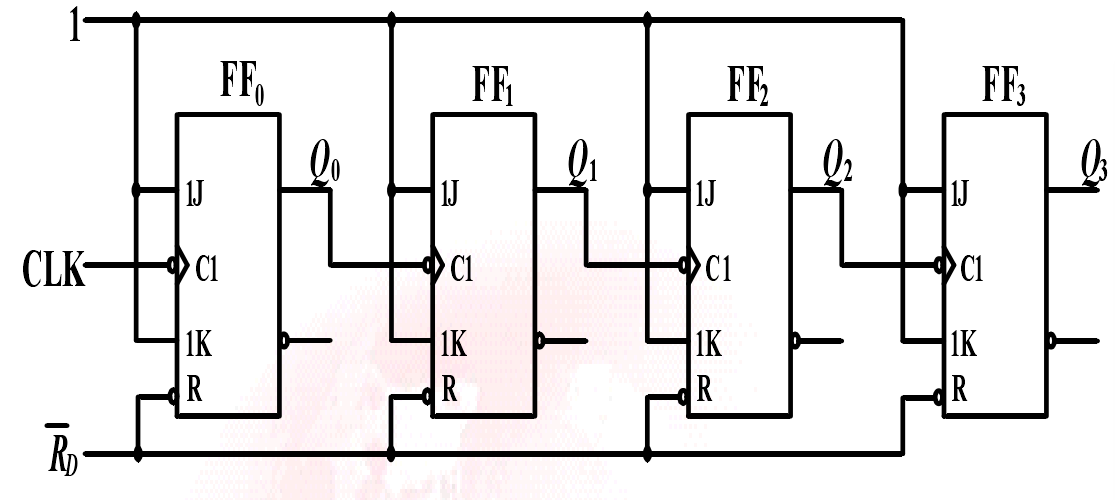

時序邏輯電路套用很廣泛,根據所要求的邏輯功能不同進行劃分,它的種類也比較繁多。在具體的授課環節中,主要選取了套用較廣、具有典型時序邏輯電路特徵的三種邏輯器件進行比較詳細地介紹[1]。1.計數器 一般來說,計數器主要由觸發器組成,用...

同步時序邏輯電路的存儲器件 觸發器是一種具有記憶能力、構成時序邏輯的基本單元電路。一個觸發器能“存儲”一位二進制數字信息:“0”或“1”。一個觸發器有兩個穩定狀態:“0”狀態:Q=0,=1;“1”狀態:Q=1,=0。觸發器(...

時序邏輯電路 時序邏輯是Verilog HDL設計中另一類重要套用。從電路特徵上看來,其特點為任意時刻的輸出不僅取決於該時刻的輸入,而且還和電路原來的狀態有關。電路裡面有存儲元件(各類觸發器,在FPGA晶片結構中只有D觸發器)用於記憶信息。

異步時序邏輯是電路的工作節奏不一致,不存在單一的主控時鐘,主要是用於產生地址解碼器、FIFO和異步RAM的讀寫控制信號脈衝。除可以使用帶時鐘的觸發器外,還可以使用不帶時鐘的觸發器和延遲元件作為存儲元件;電路狀態改變完全有外部輸入的...

它類似於含儲能元件的電感或電容的電路,如觸發器、鎖存器、計數器、移位暫存器、存儲器等電路都是時序電路的典型器件,時序邏輯電路的狀態是由存儲電路來記憶和表示的。分析 時序電路的行為是由輸入、輸出和電路當前狀態決定的。輸出和下...

三種邏輯器件 時序邏輯電路套用很廣泛,根據所要求的邏輯功能不同進行劃分,它的種類也比較繁多。在具體的授課環節中,主要選取了套用較廣、具有典型時序邏輯電路特徵的三種邏輯器件進行比較詳細地介紹。1.計數器 一般來說,計數器主要由觸發器...

數字邏輯可分為組合邏輯和時序邏輯。在一個邏輯系統中,輸出結果僅取決於當前各輸入值的稱組合邏輯;輸出結果既由當前各輸入值,又由過去的輸入值來決定的稱時序邏輯。組合邏輯不包含存儲元件,時序邏輯至少包含一個存儲元件。數字邏輯的...

計算機邏輯電路是一種離散信號的傳遞和處理,以二進制為原理、實現數位訊號邏輯運算和操作的電路。分組合邏輯電路和時序邏輯電路。前者由最基本的“與門”電路、“或門”電路和“非門”電路組成,其輸出值僅依賴於其輸入變數的當前值,與...

4.4 算術運算元件 123 4.4.1 加法器 123 4.4.2 加/減法器 130 4.4.3 比較器 132 4.4.4 乘法器 135 4.5 中型組合邏輯的分析與設計 140 4.6 小結 147 習題 148 第5章 時序邏輯元件 152 5.1 雙穩態存儲單元 153 ...

4.1SSI時序邏輯器件——觸發器83 4.1.1觸發器的結構83 4.1.2D觸發器88 4.1.3JK觸發器89 4.1.4T觸發器90 4.2SSI時序邏輯電路分析91 4.2.1時序邏輯電路概述91 4.2.2SSI時序邏輯電路分析92 4.3SSI時序邏輯電路設計95 4...

現代的數字電路由半導體工藝製成的若干數字集成器件構造而成。邏輯門是數字邏輯電路的基本單元。存儲器是用來存儲二進制數據的數字電路。從整體上看,數字電路可以分為組合邏輯電路和時序邏輯電路兩大類。發展 從前面的介紹,大家已經了解到...

3.2.3 同步時序電路設計舉例114 3.3 脈衝異步時序電路的分析與設計117 3.3.1 脈衝異步時序電路概述117 3.3.2 脈衝異步時序電路的分析118 3.3.3 脈衝異步時序電路的設計119 3.4 常用時序邏輯器件122 3.4.1 計數器...

PAL器件速度快,功耗低,並有多種結構類型,可用來設計各種組合邏輯電路和時序邏輯電路。設計時主要考慮以下幾個方面:(1)一個PAL器件的輸入/輸出引出端總數是有限的。(2)每個PAL器件輸出乘積項數目是有限的。(3)在具有暫存器和宏單元...

鎖存器多用於積體電路中,在數字電路中作為時序電路的存儲元件,在某些運算器電路中有時採用鎖存器作為數據暫存器。封裝為獨立的產品後也可以單獨套用,數據有效延遲於時鐘信號有效。這意味著時鐘信號先到,數據信號後到。在某些套用中,...

開關矩陣是高度靈活的,可以對其進行配置以便處理組合邏輯、移位暫存器或RAM。在Xilinx公司的FPGA器件中,CLB由多個(一般為4個或2個)相同的Slice和附加邏輯構成。每個CLB模組不僅可以用於實現組合邏輯、時序邏輯,還可以配置為分散式RAM和...

現場可程式門陣列器件是一種新型的高密度可程式邏輯器件,採用CMOS-SRAM工藝製造。 現場可程式門陣列是新一代的數字邏輯器件, 它們的規模比較大, 適合於時序、組合等邏輯電路套用場合, 它可替代幾十甚至上百片通用中等規模以上的 WI ...

FPGA利用小型查找表(16×1RAM)來實現組合邏輯,每個查找表連線到一個D觸發器的輸入端,觸發器再來驅動其他邏輯電路或驅動I/O,由此構成了既可實現組合邏輯功能又可實現時序邏輯功能的基本邏輯單元模組,這些模組間利用金屬連線互相連線或...