隨著現代科技的發展,人們的生活已經離不開數字電路。計算機邏輯電路是指數字電路中最基本的邏輯元件,它能按照一定的條件去控制信號的通過或不通過。基本邏輯關係為“與”、“或”、“非”三種。

基本介紹

- 中文名:計算機邏輯電路

- 外文名:Logic Gates of computer

- 分類:計算機

- 構成:門電路

- 原理:二進制

- 基本邏輯:與或非

隨著現代科技的發展,人們的生活已經離不開數字電路。計算機邏輯電路是指數字電路中最基本的邏輯元件,它能按照一定的條件去控制信號的通過或不通過。基本邏輯關係為“與”、“或”、“非”三種。

隨著現代科技的發展,人們的生活已經離不開數字電路。計算機邏輯電路是指數字電路中最基本的邏輯元件,它能按照一定的條件去控制信號的通過或不通過。基本邏輯關係為“...

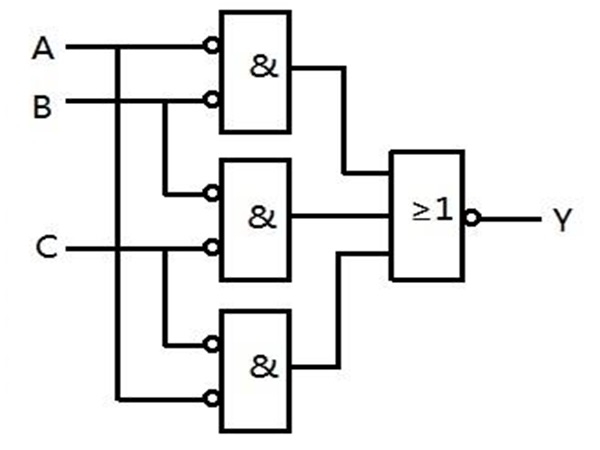

邏輯電路是一種離散信號的傳遞和處理,以二進制為原理、實現數位訊號邏輯運算和操作的電路。分組合邏輯電路和時序邏輯電路。前者由最基本的“與門”電路、“或門”...

可逆邏輯有許多套用,尤其在量子計算領域,量子可逆邏輯電路是構建量子計算機的基本單元,量子可逆邏輯電路綜合就是根據電路功能,以較小的量子代價自動構造量子可逆邏輯電路...

這一邏輯理論人們常稱它為布爾代數。20世紀30年代,邏輯代數在電路系統上獲得套用,隨後,由於電子技術與計算機的發展,出現各種複雜的大系統,它們的變換規律也遵守布爾...

CMOS邏輯電路代表互補的金屬氧化物半導體(Complementary Metal-Oxide-Semiconductor),它指的是一種特殊類型的電子積體電路(IC)。...

計算機中的數字電路按照邏輯功能和電路組成的不同特點 , 可以分為 組合邏輯電路和時序邏輯電路兩大類 。...

邏輯門(Logic Gates)是在集成電路(Integrated Circuit)上的基本組件。簡單的邏輯門可由電晶體組成。這些電晶體的組合可以使代表兩種信號的高低電平在通過它們之後產生...

邏輯元件或邏輯電路(logical circuit)是具有邏輯功能的元件(電路),也稱門電路。 常見的有“與”門、“或”門、“非”門、“與非”門及“或非”門等。 利用...

實現基本和常用邏輯運算的電子電路,叫邏輯門電路。 在數字電路中,所謂“門”就是只能實現基本邏輯關係的電路。...

計算機科學與技術 類別 邏輯電路 原理 先與後非 目錄 1 門電路 2 與非門電路 3 真值表 4 邏輯符號 5 DTL與非門 6 TTL與非門 ▪ 基本結構 ...

二極體邏輯電路(Diode logic circuit)是用晶體二極體作為操作開關的邏輯電路。二極體邏輯電路優點是電路形式簡單,工作電壓範圍不受限制,但二極體邏輯電路中只有邏輯與門,...

《計算機邏輯設計》是2015年人民郵電出版社出版的圖書,作者是余立功。...... 本書可作為計算機本科及相關專業的計算機邏輯基礎(原數字電路)等課程的教材。也適合本科...

計算機原理由馮·諾依曼(Von Neumann)與莫爾小組於1943年—1946年提出。在人類...先解釋什麼是邏輯電路、邏輯門一條線上串兩個開關,需要兩個開關都打開才能通電...

數字電路根據邏輯功能的不同特點,可以分成兩大類,一類叫組合邏輯電路(簡稱組合電路),另一類叫做時序邏輯電路(簡稱時序電路)。組合邏輯電路在邏輯功能上的特點是任意...

用數位訊號完成對數字量進行算術運算和邏輯運算的電路稱為數字電路,或數字系統。由於它具有邏輯運算和邏輯處理功能,所以又稱數字邏輯電路。現代的數字電路由半導體工藝...

美國ILLIAC-IV計算機,是第一台全面使用大規模集成電路作為邏輯元件和存儲器的計算機,它的出現標誌著計算機的發展已到了第四代。Illiac計算機ILLIAC系統結構 編輯 ...

用以實現基本邏輯運算和複合邏輯運算的單元電路稱為門電路。常用的門電路在邏輯功能上有與門、或門、非門、與非門、或非門、與或非門、異或門等幾種。...

於邏輯“0”,這被稱做TTL(電晶體-電晶體邏輯電平)信號系統,這是計算機處理器...TTL電路是電流控制器件,TTL電路的速度快,傳輸延遲時間短(5-10納秒),但是功耗大...

過去有些計算器像是今日的計算機一樣大,第一個機械計算器是桌面型機械設備,但很快被桌面型電力機械計算器取代,之後又被真空管、電晶體、集成電路邏輯線路等材料依...

《計算機電子技術》是2006年2月機械工業出版社出版的圖書,作者是王慧玲。...包括數字電路基礎、組合邏輯電路、時序邏輯電路、可程式器件、A/D與D/A轉換器...