概念

基本單元

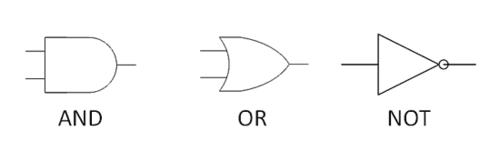

邏輯門又稱“數字邏輯電路基本單元”。執行“或”、“與”、“非”、“或非”、“與非”等

邏輯運算的電路。任何複雜的

邏輯電路都可由這些邏輯門組成。廣泛用於計算機、通信、控制和數位化儀表。

作用

通過控制高、低電平(分別代表邏輯上的“真”與“假”或二進制當中的“1”和“0”),從而實現邏輯運算。

邏輯門的種類

常見的邏輯門包括“與”門,“或”門,“非”門,“

異或”(也稱:互斥或)等等。邏輯門可以組合使用實現更為複雜的邏輯運算。

或門

或門(英文:Or gate)又稱或電路。如果幾個條件中,只要有一個條件得到滿足,某事件就會發生,這種關係叫做“或”邏輯關係。具有“或”邏輯關係的電路叫做或門。或門有多個輸入端,一個輸出端,多輸入或門可由多個2輸入或門構成。只要輸入中有一個為高電平時(邏輯1),輸出就為高電平(邏輯1);只有當所有的輸入全為低電平時,輸出才為低電平。

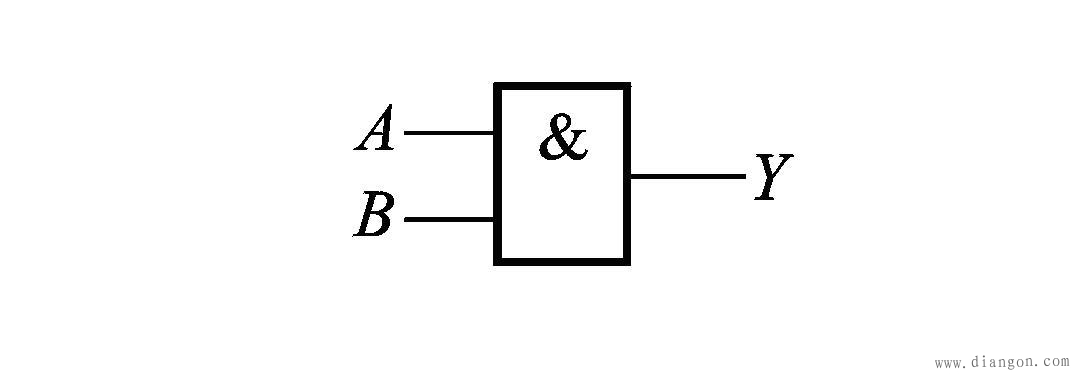

與門

與門(英語:AND gate)又稱“與電路”。是執行“與”運算的基本邏輯門電路。有多個輸入端,一個輸出端。當所有的輸入同時為高電平(邏輯1)時,輸出才為高電平,否則輸出為低電平(邏輯0)。

非門

非門(英文:NOT gate)又稱反相器,是

邏輯電路的基本單元,非門有一個輸入和一個輸出端。邏輯符號中輸出端的圓圈代表反相的意思。當其輸入端為高電平(邏輯1)時輸出端為低電平(邏輯0),當其輸入端為低電平時輸出端為高電平。也就是說,輸入端和輸出端的電平狀態總是反相的。

與非門

由與門與非門組合而成。

或非門

由或門和非門組合而成。

其中,非門和或非門在數字電路中較為常見。

符號表

設其中A和B為輸入變數

類型 | 又名/短釋 | 邏輯函式表示 | 真值表 |

NOT | 非門╱反相器:

逆轉輸入的高低狀態。 | A' | 輸入

A

0

1 | 輸出

An

1

0 |

AND | 與門╱且門:

所有輸入為高時,

才會有輸出高。 | A*B | 輸入

A B

0 0

0 1

1 0

1 1 | 輸出

AandB

0

0

0

1 |

NAND | 與非門:

與與門相反。

所有輸入為高時,

才會有輸出低。 | (A*B)' | 輸入

A B

0 0

0 1

1 0

1 1 | 輸出

AnandB

1

1

1

0 |

OR | 或門:

所有輸入為低時,

才會有輸出低。 | A + B | 輸入

A B

0 0

0 1

1 0

1 1 | 輸出

AorB

0

1

1

1 |

NOR | 或非門:

與或門相反。

所有輸入為低時,

才會有輸出高。 | (A + B)' | 輸入

A B

0 0

0 1

1 0

1 1 | 輸出

AnorB

1

0

0

0 |

XOR | 異或門:

輸入相同時輸出為低,

否則為高。 | A'B + AB' | 輸入

A B

0 0

0 1

1 0

1 1 | 輸出

AxorB

0

1

1

0 |

XNOR | 同或門:

與異或門相反。

輸入相同時輸出為高,

否則為低。 | AB + A'B' | 輸入

A B

0 0

0 1

1 0

1 1 | 輸出

AxnorB

1

0

0

1 |

邏輯門電路

把基本邏輯運算的電子電路稱之為

邏輯門電路。在數字電路關係套用中,邏輯門電路中的門代表著基本邏輯關係的電路。

通過對邏輯門內部電路的源器件的差異,我們可以將其分為三大類,比較常用的就是CMOS 的邏輯門電路。

這種CMOS 邏輯門電路具備良好的套用效益,首先其功耗比較低,具備較低的套用成本,其電源電壓的範圍比較寬,邏輯度比較高,具備較強的抗干擾能力,其輸入阻抗比較高。MOS 門電路是由一系列的單極型MOS 管構成,其具備比較簡單的製造工藝,其功耗水平比較低,具備較高的集成度,其抗干擾能力強,比較適合進行大規模積體電路的套用。

在實踐過程中,MOS 門電路按照其MOS 管的套用不同,進行不同類型的劃分。CMOS 電路的套用優點比較特殊,其靜態功耗比較低,抗干擾能力強,工作具備較高的穩定性,其開關速度也是比較高的,因此其套用性比較廣泛。

在數字電路套用中,邏輯門電路是一種基本的邏輯元件。邏輯門的中就是一種開關,在一定條件的建立下,其決定信號的通過或者不通過。在實際運作中,我們可以看到門電路輸入及其輸出存在密切的因果關係,我們把門電路稱之為邏輯門電路,其基本邏輯關係是非、或、與關係。