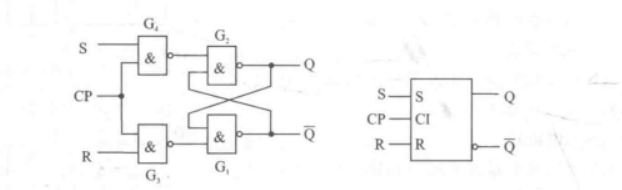

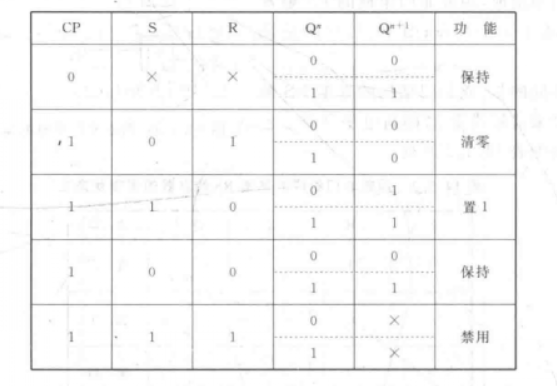

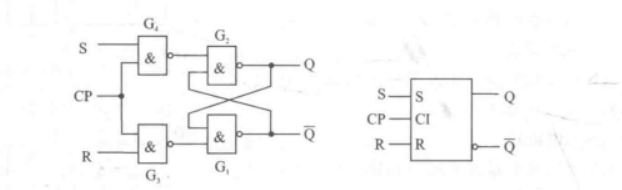

復位/置位觸發器(R、S分別是英文復位,置位的縮寫)也叫做基本R-S觸發器,是最簡單的一種觸發器,是構成各種複雜觸發器的基礎。

基本介紹

- 中文名:復位/置位觸發器

- 別名:RS觸發器

- 學科:電工電子技術

- 組成:與非門

- 方式:正反饋

- 特點:簡單,基本

復位/置位觸發器的狀態

工作原理

電路結構

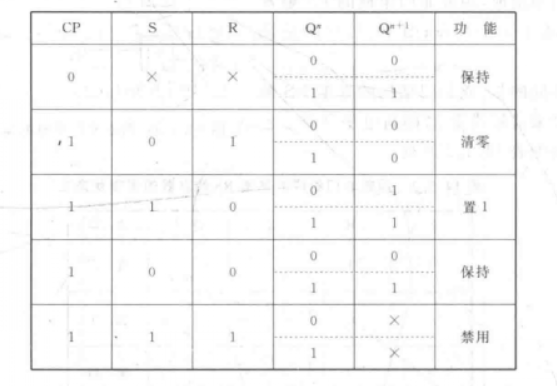

真值表

SR鎖存器一般指本詞條

復位/置位觸發器(R、S分別是英文復位,置位的縮寫)也叫做基本R-S觸發器,是最簡單的一種觸發器,是構成各種複雜觸發器的基礎。

觸發器是構成時序邏輯電路以及各種複雜數字系統的基本邏輯單元。觸發器和鎖存器是在計算機、通訊和許多其他類型的系統中使用的數字電子系統的基本組成部分。觸發器的線路圖由邏輯門組合而成,其結構均由SR鎖存器派生而來(廣義的觸發器包括...

4.4.2 逐位進位加法器 4.4.3 任務 4.5 奇偶校驗器 4.6 三態緩衝器 4.6.1 多值邏輯 4.7 組合邏輯塊的測試平台 總結 參考資料 練習題 第5章 時序邏輯塊的SystemVerilog模型 5.1 鎖存器 5.1.1 SR鎖存器 5.1.2 D...

第5章 觸發器 5.1 SR鎖存器 5.2 時鐘電平觸發的觸發器 5.3 時鐘脈衝觸發的觸發器 5.4 時鐘邊沿觸發的觸發器 5.5 觸發器邏輯功能的分類及邏輯功能的描述 本章小結 習題 第6章 時序邏輯電路 第7章 半導體存儲器 第8章 可...

4.2鎖存器140 4.2.1SR和SR鎖存器140 4.2.2D鎖存器143 4.3觸發器143 4.3.1邊沿觸髮式觸發器144 4.3.2標準圖形符號145 4.3.3直接輸入147 4.4時序電路分析148 4.4.1輸入方程148 4.4.2狀態表148 4.4.3狀態圖150 ...

2.6.1數據比較器 2.6.2加法器 2.7奇偶校驗器 2.7.1奇偶校驗的基本原理 2.7.2具有奇偶校驗的數據傳輸 小結 習題 第3章時序邏輯 3.1鎖存器 3.1.1鎖存器的基本特性 3.1.2基本SR鎖存器 3.1.3門控SR鎖存...

4.1 鎖存器 133 4.1.1 基本SR鎖存器 133 4.1.2 鐘控SR鎖存器 137 4.1.3 鐘控D鎖存器 138 4.2 觸發器 141 4.2.1 主從D觸發器 141 4.2.2 維持阻塞D觸發器 143 4.2.3 其他功能的觸發...

1.9.9乘法器 1.10時序邏輯電路 1.10.1時序邏輯電路類型 1.10.2時序邏輯電路特點 1.10.3基本SR鎖存器 1.10.4同步SR鎖存器 1.10.5D鎖存器 1.10.6D觸發器 1.10.7其他觸發器 1.10.8普通暫存器 1.10.9移位暫存器 1...

第5章鎖存器和觸發器 5.1時序電路基本邏輯單元概述 5.1.1時序電路基本邏輯單元及特點 5.1.2鎖存器和觸發器分類及描述 5.2鎖存器 5.2.1基本SR鎖存器 5.2.2具有使能端的SR鎖存器 5.2.3D鎖存器 5.3主從觸發器 5.3...

6.3 移位器125 6.4 乘法運算126 6.4.1 二進制乘法126 6.4.2 有符號乘法129 6.5 除法運算132 6.6 算術邏輯單元(ALU)135 習題138 Chapter 07 時序電路 7.1 鎖存器和觸發器142 7.1.1 SR 鎖存器142 7.1.2 時鐘...

6.1.3SR鎖存器的套用 6.2觸發器 6.2.1電平觸發的觸發器 6.2.2脈衝觸發的觸發器 6.2.3邊沿觸發的觸發器 6.2.4觸發器功能匯總 6.3總結 習題 …… 第7章時序邏輯電路的分析與設計 ...

4.2 SR鎖存器 110 4.3 D鎖存器 113 4.4 鎖存器的缺陷 114 4.5 D觸發器 115 4.5.1 選擇電路 116 4.5.2 操作規範 116 4.5.3 建立和保持時間 116 4.6 無相位差的時鐘頻率估計 120 4.7 觸發器使能 120 ...

第5章鎖存器和觸發器 5.1鎖存器 5.1.1基本SR(置位復位)鎖存器 5.1.2套用舉例 5.1.3門控SR鎖存器 5.1.4門控D鎖存器 5.2邊沿觸發的觸發器 5.2.1主從觸發器 5.2.2維持阻塞觸發器 5.2.3利用傳輸延遲的觸發器...

附錄二信號發生器和示波器使用中常見問題 附錄三非線性及其測量 附錄四耦合 附錄五單穩態觸發器 附錄六D觸發器 附錄七TDC-GP2晶片簡介 附錄八SR鎖存器 附錄九電荷靈敏度 附錄十前置放大器實驗模組原理圖 附錄十一主放大器實驗模組原理圖...

2.8.1復用器47 2.8.2解碼器50 2.9時序51 2.9.1傳播延遲和最小延遲51 2.9.2毛刺54 2.10總結55 習題55 面試問題60 第3章時序邏輯設計61 3.1引言61 3.2鎖存器和觸發器61 3.2.1SR鎖存器62 3.2.2D鎖存器63 3.2...

一、在基本保持原有理論體系的情況下,對體系結構作了調整,將原來十一章的內容整合成了八章:將原來“觸發器”和“半導體存儲器”兩章的主要內容合併為現在的“第五章半導體存儲電路”,同時取消了原有的“可程式邏輯器件”和“硬體...

5.2.1編碼器110 5.2.2解碼器112 5.2.3顯示解碼器113 5.3觸發器116 5.3.1基本SR鎖存器116 5.3.2JK觸發器118 5.3.3D鎖存器和D觸發器119 5.4時序邏輯電路121 5.4.1暫存器122 5.4.2計數器124 5.4.3集成計數器...

5.7 選擇器 5.8 匯流排 5.9 優先編碼器 5.10 比較器 5.11 移位器和循環移位器 5.12 唯讀存儲器 5.13 可程式邏輯陣列 5.14 本章小結 5.15 參考文獻 5.16 習題 第6章 時序邏輯 6.1 SR鎖存器 6.2 門...

4.2 鎖存器和觸發器77 4.2.1 雙穩態元件77 4.2.2 SR鎖存器78 4.2.3 D鎖存器79 4.2.4 D觸發器79 4.2.5 T觸發器81 4.3 同步時序邏輯設計82 4.3.1 同步時序邏輯設計步驟82 4.3.2 狀態圖/狀態表設計83...

6.3鎖存器302 6.3.1置位/復位型鎖存器302 6.3.2門控SR鎖存器307 6.3.3延遲鎖存器308 6.4觸發器313 6.4.1主從SR觸發器314 6.4.2主從式D觸發器315 6.4.3主從式JK觸發器316 6.4.4邊沿觸髮式D觸發器318 6.4.5...

2.8.1 多路選擇器49 2.8.2 解碼器52 2.9 時序52 2.9.1 傳輸延遲和最小延遲53 2.9.2 毛刺55 2.10 總結57 習題57 面試問題62 第3章 時序邏輯設計63 3.1 引言63 3.2 鎖存器和觸發器63 3.2.1 SR鎖存器...

4.4代碼轉換器109 4.5算術比較電路109 4.6用Verilog設計組合邏輯電路110 4.7小結121 4.8解決問題的實例121 習題126 參考文獻128 第5章觸發器、暫存器和計數器129 5.1基本鎖存器129 5.2門控SR鎖存器131 5.3門控D鎖存器132...

1.6 基本組合邏輯241.6.1 編碼器和解碼器241.6.2 未定義的輸入狀態261.6.3 數據選擇器271.6.4 延遲和競爭冒險271.6.5 加法器281.6.6 乘法器311.6.7 數值比較器321.7 鎖存器321.7.1 SR鎖存器32...

3.4.1 一位半加器和全加器的基本原理 80 3.4.2 多位加法器的基本原理 82 3.4.3 減法器的基本原理 83 習題 84 第4章 鎖存器和觸發器 86 4.1 概述 86 4.2 鎖存器 86 4.2.1 SR鎖存器的基本原理 87 4.2.2 D...

5.8.14位數值比較器 5.8.2中規模(MSI)4位數值比較器 5.8.3VHDL設計數值比較器 5.9編碼器 5.9.1二進制編碼器 5.9.2優先編碼器 5.9.3VHDL優先編碼器 本章小結 習題 第6章觸發器 內容提要 6.1概述 6.2SR鎖存器 6...

第三十節 變壓器耦合振盪器 (210)第三十一節 光電耦合器 (212)第三十二節 邏輯門電路 (216)第三十三節 SR鎖存器 (219)第三十四節 D觸發器 (220)第三十五節 施密特觸發器 (221)第三十六節 單穩態電路 (223)第三十七節 ...