版圖設計規則檢查是積體電路設計物理驗證的一部分,晶圓代工廠對各自不同工藝參數制定出滿足晶片製造良率的同一工藝層及不同工藝層之間幾何尺寸的約束,這些尺寸規劃的集合就是版圖設計規則。

基本介紹

- 中文名:設計規則檢查

- 外文名:Design Rule Check

- 英文縮寫:DRC

檢測介紹

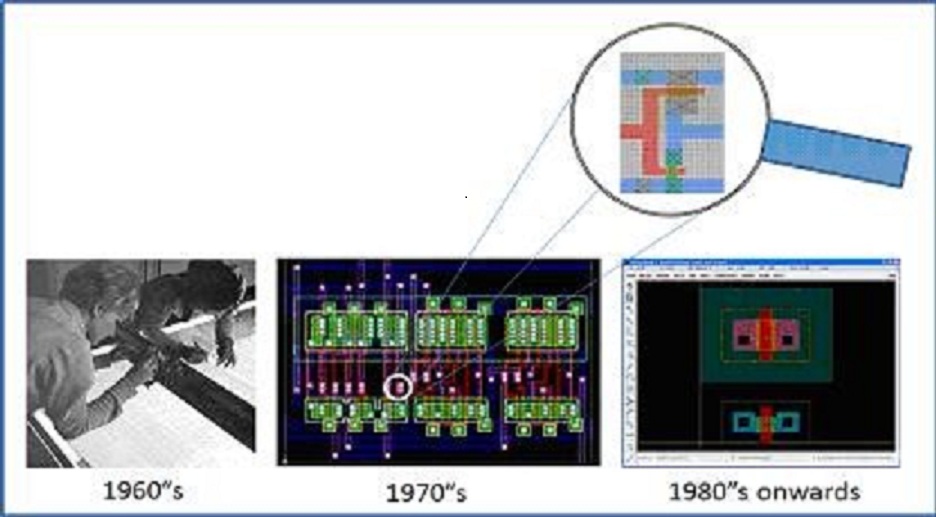

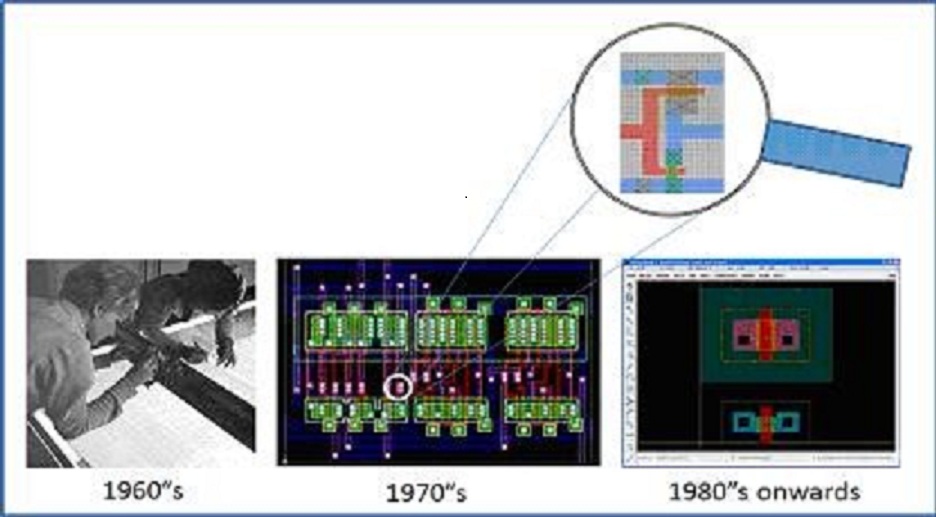

發展歷史

版圖設計規則檢查是積體電路設計物理驗證的一部分,晶圓代工廠對各自不同工藝參數制定出滿足晶片製造良率的同一工藝層及不同工藝層之間幾何尺寸的約束,這些尺寸規劃的集合就是版圖設計規則。

版圖設計規則檢查是積體電路設計物理驗證的一部分,晶圓代工廠對各自不同工藝參數制定出滿足晶片製造良率的同一工藝層及不同工藝層之間幾何尺寸的約束,這些尺寸規劃的集合就是版圖設計規則。檢測介紹DRC 的主要目的是檢査版圖所有因...

光刻規則檢查是指實施光刻工藝前,通過光刻成像模型提前獲知該晶片設計將來可能面臨的可製造性問題,從而儘可能降低積體電路製造失敗的幾率。通過套用光學成像模型,在經過光學解析度增強技術處理的光刻版圖上,檢查、搜尋出成像效果不佳的區域。通常通過下一代光學鄰近效應修正(OPC)後驗證工具為代表的光刻成像模擬軟體,...

6.2 元器件雙面貼放PCB設計——USB轉串口連線器 6.2.1 產品介紹 6.2.2 設計前準備 6.2.3 設計PCB時考慮的因素 6.2.4 從原理圖載入網路表和元器件到PCB 6.2.5 PCB雙面布局 6.2.6 有關SMD元器件的布線規則設定 6.2.7 PCB手工布線 6.2.8 設計規則檢測 6.3 印製板輸出 6.4 實訓 6.4.1 ...

8.5 設計規則檢測……… 183 8.5.1 DRC設定……… 183 8.5.2 常規DRC校驗……… 184 8.5.3 設計規則校驗報告……… 186 8.6 PCB的3D預覽……… 188 8.7 PCB後期處理……… 188 8.7.1 生成報表……… 188 8.7.

一、電氣設計規則 125 二、布線設計規則 128 三、阻焊層設計規則 133 四、內層設計規則 134 五、測試點設計規則 136 六、電路板制板規則 137 操作練習 138 任務2 PCB的高級編輯技巧 138 一、放置坐標指示 138 二、距離標註 140 三、敷銅 142 四、補淚滴 143 五、網路包地 145 六、放置文字 145 七、放置...

3.3 PCB設計 57 3.3.1 創建PCB檔案 57 3.3.2 規劃電路板 58 3.3.3 裝載網路表 61 3.3.4 元件布局 63 3.3.5 布線 64 3.3.6 設計規則校驗(DRC) 67 3.3.7 檔案保存輸出 68 3.4 設計實例 68 3.4.1 實例1 68 3.4.2 實例2 69 任務實施 70 子任務一 繪製函式信號發生器的原理圖 ...

本科畢業論文(設計)抽檢辦法(試行)第一章 總則 第一條 按照《深化新時代教育評價改革總體方案》和《關於深化新時代教育督導體制機制改革的意見》要求,為加強和改進教育督導評估監測,做好本科畢業論文(設計)(以下簡稱本科畢業論文)抽檢工作,保證本科人才培養基本質量,制定本辦法。第二條 教育部負責本科畢業論文...

協同最佳化的(Design Technology Co-optimization,DTCO) 主要內容包括設計規則(Design Rules)、標準單元(Standard Cell)、工藝檔案 (Technology File)和 Spice 模型。工藝和設計的協同最佳化體現為:工藝工程師從工藝角度出發,進行光刻方案的探索及最佳化,並提供設計規則和壞點圖形庫給設計工程師,保證在設計階段能夠避免...

⑤在規定了輸入數據必須遵守的規則的情況下,可確立一個有效等價類(符合規則)和若干個無效等價類(從不同角度違反規則)。⑥在確知已劃分的等價類中各元素在程式處理中的方式不同的情況下,則應再將該等價類進一步的劃分為更小的等價類。設計用例 在確立了等價類後,可建立等價類表,列出所有劃分出的等價類:...

指依據國家有關法律、法規、工程建設強制性標準和設計檔案,對建設工程的材料、構配件、設備,以及工程實體質量、使用功能等進行測試確定其質量特性的活動。主要涵蓋公路、橋樑、建築、電力、核電、鐵路、船舶、特種設備等。檢測手段 主要檢測手段為無損檢測技術 無損檢測是工業發展必不可少的有效工具,在一定程度上反映了...

GB50045高層民用建築設計防火規範 GB50084—2001(2005年版)自動噴水滅火系統設計規範 GB50116—2006建築設計防火規範 GB50219水噴霧滅火系統設計規範 GB50284飛機庫設計防火規範 GA588消防產品現場檢查判定規則 術語和定義 下列術語和定義適用於本檔案。3.1建設工程消防設施 建(構)築物中設定的用於防火、滅火、保障...

治具又分工裝治具、檢測治具兩種,前者用於機械加工、焊接加工、裝配等工藝便於加工、滿足精度的需要而設計的一種工裝夾具;後者為檢測使用,因為有些機械尺寸不便於測量,因其形狀複雜,我們只好設計專門的檢測塊或者檢測用的針對某一種產品而設計檢具,比方說我們有塞規、環規等一些規則的檢具,但有些是不規則的就...

(2)簡易的設計修改和版本控制功能(Ease of design modification and versioning)(3)設計的標準組件的自動產生(Automatic generation of standard components of the design)(4)設計是否滿足要求和實際規則的檢驗(Validation/verification of designs against specifications and design rules)(5)無需建立物理原型的設計模擬(...

⑶檢驗規則 ⑷包裝標誌與儲運 4.編制試製鑑定大綱:試製鑑定大綱是樣品及小批試製用必備技術檔案。要求大綱具備:⑴能考核和考驗樣品(或小批產品)技術性能的可靠性、安全性,規定各種測試性能的標準方法及產品試驗的要求和方法。⑵能考核樣品在規定的極限情況下使用的可行性和可靠性;⑶能提供分析產品核心功能指標的...

電子信息產品在設計、生產和銷售過程中應當符合電子信息產品有毒、有害物質或元素控制國家標準或行業標準,分兩階段施行:第一階段:投放市場的電子信息產品上應標識環保使用期限,標識其中含有的有毒、有害物質或元素名稱、含量、所在部件及其可否回收利用等;電子信息產品包裝物上,應標註包裝物材料名稱。可按照標準SJ/...

設定有《政策導向》《科技視點》《創新論壇》《法規標準》《重大項目跟蹤》《試驗研究》《材料與設計》《科研足跡》《檢驗評價》《檢測技術》《管理技術》《節能減排》《水處理》《安全分析》《事故分析》《應急救援》《特檢之苑》《企業之窗》《行業動態》等欄目。人才培養 據2017年11月研究院官網顯示,中國特種設備...

2019年7月1日,國家標準《檢驗檢測實驗室技術要求驗收規範》(GB/T 37140-2018)實施。制定依據 國家標準《檢驗檢測實驗室技術要求驗收規範》(GB/T 37140-2018)依據中國國家標準《標準化工作導則—第1部分:標準的結構和編寫規則》(GB/T 1.1-2009)規則起草。起草工作 主要起草單位:惠諾德(北京)科技有限公司...

循環冗餘校驗碼包括一系列移位、相除等數據編碼規則,其算法原理、算法程式的設計與分析,都可以通過相應的軟體編碼進行解決。循環冗餘校驗碼是利用軟體進行校驗的算法,因此其檢驗速度很快,校驗的誤碼率也較低,整個計算機網路通信的信息傳輸速度很高。CRC差錯糾正控制法能夠有效減少通信線路的誤碼率,得到的通信數據傳輸...

第十七章 印刷電路板設計 第一節 概述 第二節 原理圖設計 第三節 原理圖編輯 第四節 原理圖庫檔案編輯 第五節 PCB設計 第六節 PCB設計規則設定 第七節 PCB元件封裝庫編輯 第十八章 運動控制系統 第一節 閉環控制的直流調速系統 第二節 雙環控制的直流調速系統 第三節 可逆調速系統 第四節 脈寬調製的直流...

地方標準《建築消防設施檢測技術規程》(DB46/T 527-2021)規定了海南省建築消防設施檢測的術語和定義、總體要求、檢測項目、檢測要求、檢測結論判定規則。該標準適用於已施工完畢經調試合格的新建、擴建、改建(含室內裝修、用途變更)等工程的建築消防設施的檢測。已投入使用的建築消防設施的檢測參照使用。制定過程 制定...

理化檢測是實現工業現代化,發展科學技術的重要基礎性技術,是確保和提高產品質量,鑑定科研成果,評價產品性能,提高科研水平的重要手段和科學依據。在工業企業中,理化檢測是保證和提高產品質量的重要手段,也是新材料,新工藝,新技術工程套用研究,開發新產品,產品失效分析,壽命檢測,工程設計,環境保護等工作的基礎性...

這類方法算法簡單, 容易實現, 但是它不容易檢測線寬、線距違例等瑕疵。無參考校驗法不需要任何參考圖象, 它依據預先定義的 PCB 的設計規則來判斷待檢 PCB 圖象是否有瑕疵, 如果它不符合設計規則, 就認為有瑕疵, 因此也稱為設計規則校驗法。這類方法雖然在榆測線寬、線距違例這類瑕疵時能夠收到很好的效果, 但是...

風格檢查主要是檢查在程式設計風格方面發現的問題,包括命名規則、變數說明、程式格式、注釋的使用結構化程式設計、基本控制結構的使用。高級綜合前的檢查和轉化 Talent2000中VHDL檔案的編譯中間結果用於綜合和模擬,VHDL是面向模擬的語言,並不是所有的VHDL語句都可以綜合,在一個實用化高級綜合系統中,除了根據可綜合子集...

2、 當學生有規則的通過量規來評判他們的作業時,他們將開始對學習的結果充滿責任心,減少了“我還要做什麼”的問題。3、 量規減少了教師為學生作業進行評分的時間,並且使教師更容易向學生解釋,為什麼他們得到這個等級,他們做哪些方面的努力可以獲得提高。4、 使用量規評分的最大好處之一是使標準公開化,這意味著...

框架梁、次梁相交處按圖集要求必須設定附加箍筋,因每個人對規範掌握的程度不同,經常出現漏算。該項檢查規則可以快速查找到未布置附加箍的框架梁,方便用戶修改調整。6.磚牆淨長≥5m設定構造柱、磚牆淨高≥4m設定圈樑 設計規範要求磚牆淨長每超過5m設定一根構造柱,淨高每超過4米設定一道圈樑,用戶建模過程中,經常會...

3.1 產品抽樣:由型式檢驗組根據標準規定的產品抽樣規則進行抽樣。產品抽樣應在製造單位庫房中或在生產線末端經生產企業檢驗合格並包裝好的產品中隨機抽取經製造單位質檢部門檢驗合格的庫存產品。3.2 設計資料審查:型式檢驗組對抽樣產品的圖紙、計算書等設計資料進行審查。3.3 型式檢驗:製造單位現場具備型式檢驗條件的...

為了進行類型檢查,編譯器需要給源程式的侮一個組成部分賦予一個類型表達式。然後,編譯器要確定這些類型表達式是否滿足一組邏輯規則。這些規則稱為源語言的類型系統。類型檢查具有發現程式中的錯誤的潛能。原則上,如果目標代碼在保存元素值的同時保存了元素類型的信息,那么任何檢查都可以動態地進行。一個健全的類型系統...

測試規則 方式 目前流行的界面風格有三種方式:多窗體、單窗體以及資源管理器風格,無論那種風格,以下規則是應該被重視的。易用性 按鈕名稱應該易懂,用詞準確,摒棄模稜兩可的字眼,要與同一界面上的其他按鈕易於區分,能望文知意最好。理想的情況是用戶不用查閱幫助就能知道該界面的功能並進行相關的正確操作。易...

方法標準是指產品性能、質量方面的檢測、試驗方法為對象而制定的標準。其內容包括檢測或試驗的類別、檢測規則、抽樣、取樣測定、操作、精度要求等方面的規定,還包括所用儀器、設備、檢測和試驗條件、方法,步驟、數據分析、結果計算、評定、合格標準、復驗規則等。(4)安全、衛生與環境保護標準 這類標準是以保護人和物...

design rule checking 設計規則檢查 ; 預設法則查抄 ; 規則檢查 ; 設計規則校驗 Model Checking 模型檢測 ; 模型置信度 ; 模型檢驗 ; [自] 模型校驗 ticket checking 查票 ; 驗票 ; 票務檢查 ; 車票檢查 Checking attendance 考勤 ; 點名 Checking Luggage 行李託運 雙語例句 He and Lieutenant Cassidy were ...