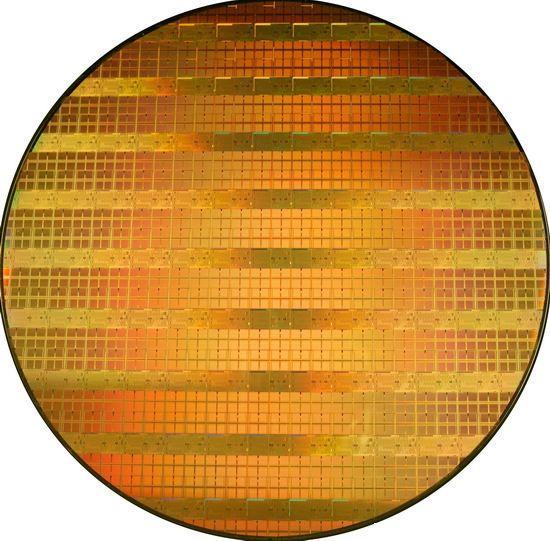

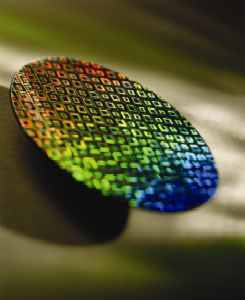

製造過程 晶圓是製造半導體晶片的基本材料,半導體積體電路最主要的原料是矽,因此對應的就是矽晶圓。

矽在自然界中以矽酸鹽或二氧化矽的形式廣泛存在於岩石、砂礫中,矽晶圓的製造可以歸納為三個基本步驟:矽提煉及提純、單晶矽生長、晶圓成型。

首先是矽提純,將沙石原料放入一個溫度約為2000 ℃,並且有碳源存在的電弧熔爐中,在高溫下,碳和沙石中的二氧化矽進行化學反應(碳與氧結合,剩下矽),得到純度約為98%的純矽,又稱作冶金級矽,這對微電子器件來說不夠純,因為半導體材料的電學特性對雜質的濃度非常敏感,因此對冶金級矽進行進一步提純:將粉碎的冶金級矽與氣態的氯化氫進行氯化反應,生成液態的矽烷,然後通過蒸餾和化學還原工藝,得到了高純度的多晶矽,其純度高達99.999999999%,成為電子級矽。

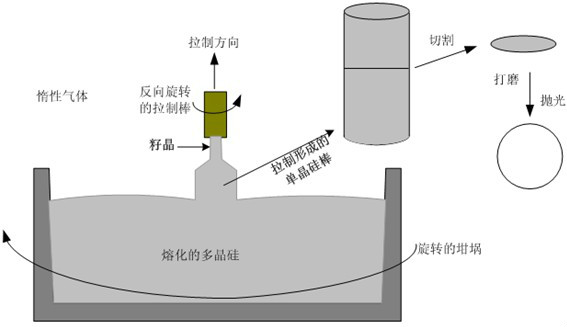

接下來是單晶矽生長,最常用的方法叫直拉法(CZ法)。如下圖所示,高純度的多晶矽放在石英坩堝中,並用外面圍繞著的石墨加熱器不斷加熱,溫度維持在大約1400 ℃,爐中的氣體通常是惰性氣體,使多晶矽熔化,同時又不會產生不需要的化學反應。為了形成單晶矽,還需要控制晶體的方向:坩堝帶著多晶矽熔化物在旋轉,把一顆籽晶浸入其中,並且由拉制棒帶著籽晶作反方向旋轉,同時慢慢地、垂直地由矽熔化物中向上拉出。熔化的多晶矽會粘在籽晶的底端,按籽晶晶格排列的方向不斷地生長上去。因此所生長的晶體的方向性是由籽晶所決定的,在其被拉出和冷卻後就生長成了與籽晶內部晶格方向相同的單晶矽棒。用直拉法生長後,單晶棒將按適當的尺寸進行切割,然後進行研磨,將凹凸的切痕磨掉,再用化學機械拋光工藝使其至少一面光滑如鏡,晶圓片製造就完成了。

晶圓製造 單晶矽棒的直徑是由籽晶拉出的速度和旋轉速度決定的,一般來說,上拉速率越慢,生長的單晶矽棒直徑越大。而切出的晶圓片的厚度與直徑有關,雖然半導體器件的製備只在晶圓的頂部幾微米的範圍內完成,但是晶圓的厚度一般要達到1 mm,才能保證足夠的機械應力支撐,因此晶圓的厚度會隨直徑的增長而增長。

晶圓製造廠把這些多晶矽融解,再在融液里種入籽晶,然後將其慢慢拉出,以形成圓柱狀的單晶矽晶棒,由於矽晶棒是由一顆晶面取向確定的籽晶在熔融態的矽原料中逐漸生成,此過程稱為“長晶”。矽晶棒再經過切段,滾磨,切片,倒角,拋光,雷射刻,包裝後,即成為積體電路工廠的基本原料——矽晶圓片,這就是“晶圓”。

基本原料 晶圓 矽是由

石英砂 所精練出來的,晶圓便是

矽元素 加以純化(99.999%),接著是將這些純矽製成矽晶棒,成為製造

積體電路 的石英半導體的材料,經過照相製版,研磨,拋光,切片等程式,將多晶矽融解拉出單晶矽晶棒,然後切割成一片一片薄薄的晶圓。

製造工藝

表面清洗 晶圓表面附著大約2um的Al2O3和甘油混合液保護層,在製作前必須進行化學刻蝕和表面清洗。

晶圓 初次氧化 由熱氧化法生成SiO2 緩衝層,用來減小後續中Si3N4對晶圓的應力氧化技術:乾法氧化Si(固)+O2 à SiO2(固)和濕法氧化Si(固)+2H2O à SiO2(固)+2H2。乾法氧化通常用來形成,柵極二氧化矽膜,要求薄,界面能級和固定

電荷密度 低的薄膜。乾法氧化成膜速度慢於濕法。濕法氧化通常用來形成作為器件

隔離 用的比較厚的二氧化矽膜。當SiO2膜較薄時,膜厚與時間成正比。SiO2膜變厚時,膜厚與時間的平方根成正比。因而,要形成較厚SiO2膜,需要較長的氧化時間。SiO2膜形成的速度取決於經擴散穿過SiO2膜到達矽表面的O2及OH基等

氧化劑 的數量的多少。濕法氧化時,因在於OH基SiO2膜中的擴散係數比O2的大。

氧化反應 ,Si 表面向深層移動,距離為SiO2膜厚的0.44倍。因此,不同厚度的SiO2膜,去除後的Si表面的深度也不同。SiO2膜為透明,通過光干涉來估計膜的厚度。這種

干涉色 的周期約為200nm,如果預告知道是幾次干涉,就能正確估計。對其他的透明薄膜,如知道其折射率,也可用公式計算出(dSiO2)/(dox)=(nox)/(nSiO2)。SiO2膜很薄時,看不到

干涉色 ,但可利用Si的疏水性和SiO2的親水性來判斷SiO2膜是否存在。也可用干涉膜計或

橢圓 儀等測出。SiO2和Si界面能級密度和固定

電荷密度 可由MOS二極體的

電容 特性求得。(100)面的Si的界面能級密度最低,約為10E+10-- 10E+11/cm ?2.eV-1 數量級。(100)面時,

氧化膜 中固定

電荷 較多,固定電荷密度的大小成為左右閾值的主要因素。

熱CVD 熱CVD(HotCVD)/(thermalCVD)

此方法生產性高,梯狀敷層性佳(不管多凹凸不平,深孔中的表面亦產生反應,及

氣體 可到達表面而附著薄膜)等,故用途極廣。膜生成原理,例如由揮發性金屬鹵化物(MX)及

金屬有機化合物 (MR)等在

高溫 中

氣相 化學反應(熱分解,氫還原、氧化、替換反應等)在基板上形成

氮化物 、

氧化物 、

碳化物 、

矽化物 、

硼化物 、高熔點金屬、金屬、

半導體 等薄膜方法。因只在

高溫 下反應故用途被限制,但由於其可用領域中,則可得緻密高純度物質膜,且

附著強度 極強,若用心控制,則可得安定薄膜即可輕易製得觸鬚(

短纖維 )等,故其套用範圍極廣。熱CVD法也可分成常壓和低壓。低壓CVD適用於同時進行多片基片的處理,壓力一般控制在0.25-2.0Torr之間。作為柵電極的多晶矽通常利用HCVD法將SiH4或Si2H。氣體熱分解(約650oC)澱積而成。採用選擇氧化進行器件隔離時所使用的

氮化矽 薄膜也是用低壓CVD法,利用氨和SiH4 或Si2H6反應面生成的,作為層間絕緣的SiO2薄膜是用SiH4和O2在400--4500oC的溫度下形成SiH4+O2-SiO2+2H2或是用Si(OC2H5)4(

TEOS :tetra ethoxy silanc)和O2在750oC左右的

高溫 下反應生成的,後者即採用TEOS形成的SiO2膜具有台階側面部被覆性能好的優點。前者,在澱積的同時導入PH3 氣體,就形成磷矽玻璃( PSG: phosphor silicate glass)再導入B2H6氣體就形成BPSG(borro ? phosphor silicate glass)膜。這兩種薄膜材料,

高溫 下的流動性好,廣泛用來作為表面平坦性好的層間絕緣膜。

熱處理 在塗敷光刻膠之前,將洗淨的基片表面塗上附著性增強劑或將基片放在惰性氣體中進行熱處理。這樣處理是為了增加

光刻膠 與基片間的粘附能力,防止顯影時光刻膠圖形的脫落以及防止濕法腐蝕時產生側面腐蝕(sideetching)。

光刻膠 的塗敷是用轉速和旋轉時間可自由設定的甩膠機來進行的。首先、用

真空 吸引法將基片吸在甩膠機的吸盤上,把具有一定粘度的

光刻膠 滴在基片的表面,然後以設定的轉速和時間甩膠。由於

離心力 的作用,

光刻膠 在基片表面均勻地展開,多餘的光刻膠被甩掉,獲得一定厚度的光刻膠膜,光刻膠的膜厚是由光刻膠的粘度和甩膠的轉速來控制。所謂

光刻膠 ,是對光、電子束或X線等敏感,具有在顯影液中溶解性的性質,同時具有耐腐蝕性的材料。一般說來,正型膠的解析度高,而負型膠具有感光度以及和下層的粘接性能好等特點。光刻工藝精細圖形(解析度,清晰度),以及與其他層的圖形有多高的位置吻合精度(套刻精度)來決定,因此有良好的光刻膠,還要有好的曝光系統。

除氮化矽 此處用乾法氧化法將氮化矽去除

離子注入 離子布植將硼離子 (B+3) 透過 SiO2 膜注入襯底,形成P型阱離子注入法是利用電場加速雜質離子,將其注入矽襯底中的方法。離子注入法的特點是可以精密地控制擴散法難以得到的低濃度雜質分布。MOS電路製造中,器件隔離工序中防止寄生溝道用的溝道截斷,調整

閥值 電壓 用的溝道摻雜, CMOS的阱形成及源漏區的形成,要採用離子注入法來摻雜。離子注入法通常是將欲摻入半導體中的雜質在

離子源 中離子化, 然後將通過質量分析磁極後選定了離子進行加速,注入基片中。

退火處理

去除光刻膠放高溫爐中進行退火處理 以消除晶圓中

晶格 缺陷和內應力,以恢復晶格的完整性。使植入的摻雜

原子 擴散到替代位置,產生電特性。

用熱磷酸去除氮化矽層,摻雜磷 (P+5) 離子,形成 N 型阱,並使原先的SiO2 膜厚度增加,達到阻止下一步中n 型雜質注入P 型阱中。

去除SIO2層

退火處理,然後用 HF 去除 SiO2 層。

乾法氧化法

乾法氧化法生成一層SiO2 層,然後LPCVD 沉積一層氮化矽。此時P 阱的表面因SiO2 層的生長與刻蝕已低於N 阱的表面水平面。這裡的SiO2 層和氮化矽的作用與前面一樣。接下來的步驟是為了

隔離區 和柵極與晶面之間的

隔離層 。

利用光刻技術和離子刻蝕技術,保留下柵隔離層上面的氮化矽層。

濕法氧化

生長未有氮化矽保護的 SiO2 層,形成 PN 之間的隔離區。

生成SIO2薄膜

熱磷酸去除氮化矽,然後用 HF 溶液去除柵隔離層位置的 SiO2 ,並重新生成品質更好的 SiO2 薄膜 , 作為柵極氧化層。

氧化

LPCVD 沉積多晶矽層,然後塗敷光阻進行光刻,以及等離子蝕刻技術,柵極結構,並氧化生成 SiO2 保護層。

表面塗敷光阻,去除 P 阱區的光阻,注入砷 (As) 離子,形成 NMOS 的源

漏極 。用同樣的方法,在 N 阱區,注入 B

離子 形成 PMOS 的源漏極。

沉積

利用 PECVD 沉積一層無摻雜氧化層,保護元件,並進行退火處理。

含有硼磷雜質的SiO2 層,有較低的熔點,硼磷氧化層(BPSG) 加熱到800 oC 時會軟化並有流動特性,可使晶圓表面初級平坦化。

深處理

濺鍍第一層金屬利用光刻技術留出金屬接觸洞,濺鍍鈦+ 氮化鈦+ 鋁+ 氮化鈦等多層

金屬膜 。離子刻蝕出布線結構,並用PECVD 在上面沉積一層SiO2

介電質 。並用SOG (spin on glass) 使表面平坦,加熱去除SOG 中的溶劑。然後再沉積一層

介電質 ,為沉積第二層金屬作準備。

(1) 薄膜的沉積方法根據其用途的不同而不同,厚度通常小於 1um 。有絕緣膜、

半導體 薄膜、金屬薄膜等各種各樣的薄膜。薄膜的沉積法主要有利用化學反應的CVD(chemical vapor deposition) 法以及

物理現象 的PVD(physical vapor deposition) 法兩大類。CVD 法有

外延生長 法、HCVD , PECVD 等。PVD 有

濺射 法和真空蒸發法。一般而言, PVD 溫度低,沒有毒氣問題; CVD 溫度高,需達到1000 oC 以上將氣體解離,來產生化學作用。PVD 沉積到材料表面的

附著力 較CVD 差一些, PVD 適用於在

光電產業 ,而

半導體 製程中的金屬導電膜大多使用PVD 來沉積,而其他絕緣膜則大多數採用要求較嚴謹的CVD 技術。以PVD 被覆硬質薄膜具有高強度,耐腐蝕等特點。

(2) 真空蒸發法( Evaporation Deposition )採用

電阻加熱 或感應加熱或者電子束等加熱法將原料蒸發澱積到基片上的一種常用的成膜方法。蒸發原料的分子(或原子)的平均自由程長( 10 -4 Pa 以下,達幾十米),所以在真空中幾乎不與其他

分子碰撞 可直接到達基片。到達基片的原料分子不具有表面移動的

能量 ,立即凝結在基片的表面,所以,在具有台階的表面上以真空蒸發法澱積薄膜時,一般,表面被覆性(覆蓋程度)是不理想的。但若可將Crambo真空抽至超高真空( <10 – 8 torr ),並且控制電流,使得欲鍍物以一顆一顆原子蒸鍍上去即成所謂分子束磊晶生長( MBE : Molecular Beam Epitaxy )。

(3) 濺鍍( Sputtering Deposition ) 所謂濺射是用高速粒子(如氬離子等)撞擊

固體 表面,將固體表面的原子撞擊出來,利用這一現象來形成薄膜的技術即讓電漿中的離子加速,撞擊原料靶材,將撞擊出的靶材原子澱積到對面的基片表面形成薄膜。

濺射 法與真空蒸發法相比有以下的特點:台階部分的被覆性好,可形成大面積的

均質 薄膜,形成的薄膜,可獲得和化合物靶材同一成分的薄膜,可獲得絕緣薄膜和高熔點材料的薄膜,形成的薄膜和下層材料具有良好的密接性能。因而,

電極 和布線用的鋁合金( Al-Si, Al-Si-Cu )等都是利用

濺射 法形成的。最常用的

濺射 法在平行平板

電極 間接上高頻( 13.56MHz )電源,使

氬氣 (壓力為1Pa )

離子 化,在靶材濺射出來的原子澱積到放到另一側電極上的基片上。為提高成膜速度, 通常利用

磁場 來增加

離子 的密度, 這種

裝置 稱為

磁控濺射 裝置( magnetron sputter apparatus ),以高電壓將通入

惰性 氬體游離,再藉由

陰極 電場加速吸引帶正電的離子,撞擊在陰極處的靶材,將欲鍍物打出後沉積在基板上。一般均加磁場方式增加電子的游離路徑,可增加氣體的解離率,若靶材為金屬,則使用DC

電場 即可,若為非金屬則因靶材表面累積

正電荷 ,導致往後的

正離子 與之相斥而無法繼續吸引正離子,所以改為RF 電場(因場的振盪頻率變化太快,使正離子跟不上變化,而讓RF-in 的地方呈現

陰極 效應)即可解決問題。

4004的50mm晶圓和Core 2 Duo的300mm晶圓 沉積第二層金屬,並刻蝕出連線結構。然後,用 PECVD 法

氧化層 和氮化矽保護層。

光刻和離子刻蝕

定出 PAD 位置。

最後進行退火處理

以保證整個 Chip 的完整和連線的連線性。

專業術語 1.

Wafer Probe晶圓 針測工序

2.

waferballing process晶圓 球狀化工藝

3.

bonded wafer晶圓

4.

cassette, wafer晶圓 匣

5.

tray, wafer晶圓 承載器

6.

wafer tray晶圓 承載器

7.

wafer cassette晶圓 匣

8.

wafer acceptance (WAT)晶圓 驗收測試

9.

wafer晶圓

10.

Wafer Mapping晶圓 映射

11.

Wafer burn-in晶圓 老化

12.

Multi Project Wafer晶圓

晶圓製造

晶圓製造 晶圓

晶圓 晶圓

晶圓

4004的50mm晶圓和Core 2 Duo的300mm晶圓

4004的50mm晶圓和Core 2 Duo的300mm晶圓