cpsr

相關詞條

- cpsr

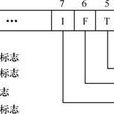

CPSR:程式狀態暫存器(current program status register) cpsr在用戶級編程時用於存儲條件碼;CPSR包含條件碼標誌,中斷禁止位,當前處理器模式以及其他狀態和控制信息。...

- 狀態暫存器

在ARM中有6個狀態暫存器,ARM7TDMI核心包含1個CPSR和5個供異常處理程式使用的SPSR。CPSR反映了當前處理器的狀態,其包含:4個條件代碼標誌(負(N)、零(Z)、進位(...

- 影子暫存器

比如Abort模式下的R13就同用戶模式下的R13不同,雖然它們編碼一樣,但是實際上對應的是不同的物理暫存器(可以將CPSR的模式域當作片選)。...

- 數據處理指令

算術邏輯運算指令完成常用的算術與邏輯的運算,該類指令不但將運算結果保存在目的暫存器中,同時更新CPSR中的相應條件標誌位。比較指令不保存運算結果,只更新CPSR中相應...

- bx

BX指令是ARM指令系統中的帶狀態切換跳轉指令。X指令跳轉到指令中所指定的目標地址,若目標地址的bit[0]為0,則跳轉時自動將CPSR中的標誌位T復位,即把目標地址的...

- spsr

SPSR:程式狀態保存暫存器 SPSR用於保存CPSR的狀態,以便異常返回後恢復異常發生時的工作狀態。 CPSR:Current Program Status Register SPSR:Saved Program Status Register...

- MSR

MSR{條件} 程式狀態暫存器(CPSR或SPSR)_<域>,運算元 MSR指令用於將運算元的內容傳送到程式狀態暫存器的特定域中。其中,運算元可以為通用暫存器或立即數。<域>用於...

- S3C44BOX

msr cpsr_cxsf,r1 ;UndefModeldr sp,=UndefStackorr r1,r0,#ABORTMODE|NOINTmsr cpsr_cxsf,r1 ;AbortModeldr sp,=AbortStack...