CMOS功耗分為靜態損耗和動態損耗。

基本介紹

- 中文名:CMOS功耗模型

- 說明:描述CMOS的功率損耗

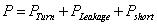

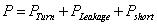

CMOS電路功耗公式

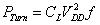

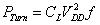

CMOS電路功耗公式 pturn的公式

pturn的公式CMOS功耗分為靜態損耗和動態損耗。

CMOS電路功耗公式

CMOS電路功耗公式 pturn的公式

pturn的公式CMOS功耗分為靜態損耗和動態損耗。...... CMOS功耗分為靜態損耗和動態損耗。中文名 CMOS功耗模型 說明 描述CMOS的功率損耗 目前,CMOS工藝在積體電路特別是數字IC中...

《低功耗CMOS電路設計》是2011年科學出版社出版的圖書,作者christian Piguet。本書內容著重敘述低功耗電路設計。...

3.1.4MOS管的小信號模型 3.1.5MOS管的亞閾值模型 3.2CMOS模擬電路的基本模組...4.5.2動態功耗 4.6CMOS邏輯門的噪聲容限 4.6.1CMOS反相器的噪聲容限 4.6.2CM...

《多電壓CMOS電路設計》是2008年機械工業出版社出版的圖書,作者是(土耳其)庫遜。...6.1 低電壓擺幅降壓變換器的電路模型6.1.1 MOSFET的功耗6.1.2 MOSFET的...

12.3.2 功耗計算 269 12.3.3 電壓降分析 271 第三部分 靜態時序分析及實戰...13.2.1 CMOS邏輯門單元時序參數 280 13.2.2 時序模型 281 13.2.3 互連線...

5.7 反相器翻轉速度模型865.8 CMOS反相器功耗885.8.1 瞬態功耗885.8.2 短路功耗895.8.3 靜態泄漏功耗915.9 功耗與電源電壓調整91...

CMOS它允許我們用簡單的概念和模型來構造邏輯電路。而理解這些概念只需要基本的...這是早期的CMOS集成邏輯門產品,工作電源電壓範圍為3~18V,由於具有功耗低、噪聲...

該著作涵蓋了從模型到器件,從電路到系統的全面內容,是一本權威的、綜合的CMOS...7.1 基於功耗和速度的偏置選擇 7.1.1 器件特性 7.1.2 偏置電路 7....

CMOS電路功耗主要由3部分組成:電路電容充放電引起的動態功耗,結反偏時漏電流引起...電源電壓的減小,模擬積體電路的設計將遇到諸多調整,採用精確的器件模型來開展設計...

低功耗CMOS邏輯電路、數字運算和轉換電路、晶片的I/O設計;第14章和第15章分別...附錄 典型SPICE模型參數習題第5章 MOS反相器的靜態特性5.1 概述...

的宏模型 6.8 小結 習題 參考文獻第7章 高性能CMOS運算放大器 7.1 緩衝運算放大器 7.2 高速/高頻CMOS運算放大器 7.3 差分輸出運算放大器 7.4 微功耗...

本書著重敘述低功耗電路設計,第1部分概述低功耗電子技術和深亞微米下體矽SOI技術的進展、CMOS納米技術中的漏電流及光互連技術等;第2部分闡述深亞微米設計模型、低...

1.3 功耗產生的原因 71.3.1 CMOS 電路的功耗 81.3.2 積體電路中的問題...3.1.1 匯流排低功耗技術 663.1.2 簡化的匯流排能耗模型 723.2 常用的匯流排低功耗...

9?2?1系統級和結構級設計階段的低功耗技術2649?2?2電路級設計階段的低功耗...11?3納米CMOS工藝角建模方法33511?3?1統計模型的需求33511?3?2統計模型的...

2.8 MOS電晶體模型2.9 結論2.10 參考文獻2.11 練習題第3章 MOS器件的製造...8.3 CMOS功耗的來源8.4 降低功耗的工藝選擇8.5 降低功耗的設計選擇...

全書詳細講述了CMOS數字積體電路的相關內容,為反映納米級別CMOS技術的廣泛套用和技術的發展, 全書在前版的基礎上對電晶體模型公式和器件參數進行了修正,幾乎全部章節...

《數字積體電路分析與設計》的作者是楊兵,於2013年出版。內容包括CMOS製造工藝、器件模型和公式、 基本門電路、靜態與動態電路、雙穩態電路、低功耗CMOS設計、存儲器...

簡單的CMOS反相器的開關模型是由一對互補的場效應管組成,原理圖如下圖所示,一...1、功耗低:CMOS積體電路採用場效應管,且都是互補結構,工作時兩個串聯的場效應...