基本介紹

- 中文名:鰭式場效應電晶體

- 外文名:Fin Field-Effect Transistor

發明人

該項技術的發明人是加州大學伯克利分校的胡正明(Chenming Hu)教授 。胡正明教授在台灣大學獲電子工程學士學位,在伯克利大學獲得電子工程與計算機科學碩士和博士學位。現為美國工程院院士。他研究的BSIM模型已成為電晶體模型的唯一國際標準,培養了100多名學生,許多學生已經成為這個領域的大牛,曾獲Berkeley的最高教學獎。

圖1 英特爾公布的FinFET的電子顯微鏡照片

圖1 英特爾公布的FinFET的電子顯微鏡照片工作原理

FinFET源自於傳統標準的電晶體—場效應電晶體 (Field-Effect Transistor;FET)的一項創新設計。在傳統電晶體結構中,控制電流通過的閘門,只能在閘門的一側控制電路的接通與斷開,屬於平面的架構。在FinFET的架構中,閘門成類似魚鰭的叉狀3D架構,可於電路的兩側控制電路的接通與斷開。 這種設計可以大幅改善電路控制並減少漏電流(leakage),也可以大幅縮短電晶體的閘長。

結構

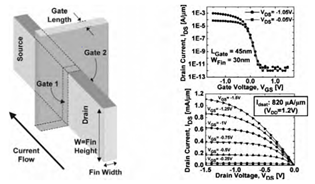

如圖2所示,FinFET的主要特點是,溝道區域是一個被柵極包裹的鰭狀半導體。沿源漏方向的鰭的長度,為溝道長度。柵極包裹的結構增強了柵的控制能力, 對溝道提供了更好的電學控制,從而降低了漏電流,抑制短溝道效應。然而FinFET有很多種,不同的FinFET有不同的電學特性。下面根據襯底類型、溝道的方向、柵的數量、柵的結構,分別給予介紹。SOI FinFET 和體FinFET。根據FinFET襯底,FinFET可以分成兩種。一種是SOI FinFET,一種是體FinFET。體FinFET形成在體矽襯底上。由於製作的工藝不同,相比於SOI襯底,體矽襯底具有低缺陷密度,低成本的優點。此外,由於SOI襯底中埋氧層的熱傳導率較低,體矽襯底的散熱性能也要優於SOI襯底。

體FinFET,SOI FinFET具有近似的寄生電阻、寄生電容,從而在電路水平上可以提供相似的功率性能。但是 SOI 襯底的輕鰭摻雜FinFET,相比於體FinFET,表現出較低的節電容,更高的遷移率和電壓增益的電學性能。

圖2 FinFET的結構和I - V參數

圖2 FinFET的結構和I - V參數優勢

FinFET器件相比傳統的平面電晶體來說有明顯優勢。首先,FinFet溝道一般是輕摻雜甚至不摻雜的,它避免了離散的摻雜原子的散射作用,同重摻雜的平面器件相比,載流子遷移率將會大大提高。另外,與傳統的平面CMOS相比,FinFET器件在抑制亞閾值電流和柵極漏電流方面有著絕對的優勢。FinFET的雙柵或半環柵等體鰭形結構增加了柵極對溝道的控制面積,使得柵控能力大大增強,從而可以有效抑制短溝效應,減小亞閾值漏電流。由於短溝效應的抑制和柵控能力的增強,finFET器件可以使用比傳統更厚的柵氧化物,這樣FinFET器件的柵漏電流也會減小。顯然,FinFET優於PDSOI。並且,由於FinFET在工藝上與CMOS技術相似,技術上比較容易實現。 所以目前已被很多大公司用在小尺寸1C的製造中。