基本介紹

- 中文名:高頻寬存儲器

- 外文名:High Bandwidth Memory

- 領域:計算機存儲

- 套用領域:圖形處理器

- 研發者:超微半導體和SK Hynix

- 特點:數據存取速度快

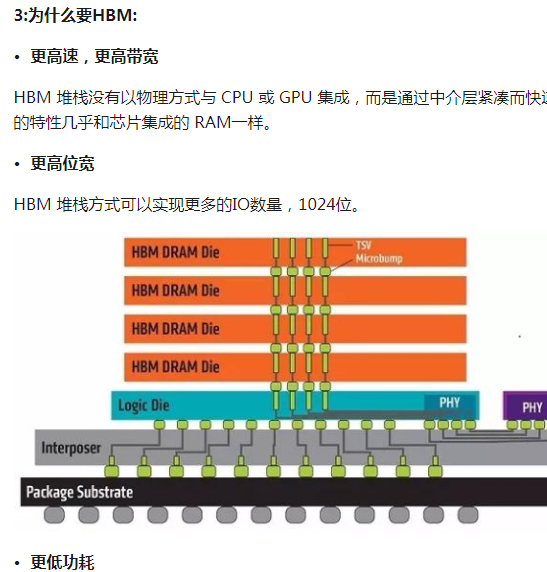

高頻寬存儲器(High Bandwidth Memory,HBM)是超微半導體和SK Hynix發起的一種基於3D堆疊工藝的高性能DRAM,適用於高存儲器頻寬需求的套用場合,像是圖形處理器、網路交換及轉發設備(如路由器、...

高頻寬存儲器(英文:High Bandwidth Memory,縮寫HBM)是超微半導體和SK Hynix發起的一種基於3D堆疊工藝的高性能DRAM,適用於高存儲器頻寬需求的套用場合,像是圖形處理器、網上交換及轉發設備(如路由器、交換器)等。首個使用HBM的設備...

ddr型sram具有出眾的整體匯流排利用率以及高得多的總頻寬,性能也因此得到了最大限度的提升。 和qdr型sram一樣,ddr型sram也有兩種格式:即2字脈衝串和4字脈衝串。究竟選擇哪一種取決於所需的數據顆粒度以及存儲器的數據匯流排寬度。

VSA採用多通道處理方式,把數據平均分散在每一個通道上,改變了物理磁碟讀寫方式,令讀寫速度暢通無阻,以VSA1016 16盤陣列櫃為例,背板通道總頻寬高達6Gbps,保障了磁碟的讀寫速度。VSA 是一種新的服務器存儲套用方案,超低擁有成本(...

當然,這個計算方法是針對僅靠上升沿信號傳輸數據的SDRAM而言的,對於上升沿和下降沿都傳輸數據的DDR來說計算方法有點變化,應該在最後乘2,因為它的傳輸效率是雙倍的,這也是DDR能夠有如此高性能的重要原因。對於和存儲器頻寬關係很大的...

這些優異的條件使得大多數數位相機選擇CF卡作為其首選存儲介質。PCI-e快閃記憶體卡(PCI-Express)是最新的匯流排和接口標準,它原來的名稱為“3GIO”,PCIe屬於高速串列點對點雙通道高頻寬傳輸,所連線的設備分配獨享通道頻寬,不共享資源,主要支持...

第五版圖形用雙倍數據傳輸率存儲器(Graphics Double Data Rate, version 5,簡稱GDDR5),是一種高性能顯示卡使用的同步動態隨機存取存儲器,專為高頻寬需求計算機套用所設計。由AMD、SK Hynix、三星電子、NVIDIA、JEDEC等聯合制定,取代...

DDR4 SDRAM是一種高頻寬的計算機存儲器規格,屬於SDRAM家族的存儲器產品。DDR4 SDRAM(Double-Data-Rate Fourth Generation Synchronous Dynamic Random Access Memory,簡稱為DDR4 SDRAM),是一種高頻寬的計算機存儲器規格。它屬於SDRAM家族...

QBM結構在不增加存儲器基準頻率(記憶體匯流排工作頻率)的條件下增加了存儲器子系統的數據頻寬。QBM利用現有的DDR SDRAM和一種"2到1" FET開關;一種具有基準頻率輸出、基準頻率的90度相移輸出以及雙倍基準頻率輸出的鎖相環(PLL)來實現4倍...

內部133 MHz多層匯流排架構與37條DMA通道、一個雙路外部匯流排接口以及分散式存儲器密不可分,其中,存儲器包括可配置為緊耦合存儲器(TCM)的64-KB SRAM。該匯流排架構可保持處理器以及高速外設所需的高頻寬。I/O支持1.8V或3.3V工作電壓...

這樣簡化了控制器設計,因為它可以避免指令匯流排上的衝突。而且,採用一個簡單的指令序列還可以提高指令和數據匯流排的效率。由於在讀/寫指令之間不存在“氣泡”(bubble)或空隙周期,因此實際的存儲器頻寬也得到提高。最後一點,DDR2採用細...

Core i7處理器的三通道記憶體技術,最高可以支持DDR3-1600記憶體, 可以提供高達38.4GB/s的高頻寬,和主流雙通道記憶體20GB/s的頻寬相比,性能提升幾乎可以達到翻倍的效果。優點 “記憶體控制器”這個名詞我們早在AMD的K8平台上就已經見識過了...

內部133 MHz多層匯流排架構與37條DMA通道、一個雙路外部匯流排接口以及分散式存儲器密不可分,其中,存儲器包括可配置為緊耦合存儲器(TCM)的64-KB SRAM。該匯流排架構可保持處理器以及高速外設所需的高頻寬。 I/O支持1.8V或3.3V工作...