基本介紹

- 中文名:四倍頻寬記憶體

- 外文名:Quad Band Memory

- 簡稱:QBM

- 特點:不需要更高時脈頻率的記憶體組件

簡介,背景,原理,歷程,前途似錦,風光無限,公開露面,無奈夭折,

簡介

QBM(Quad Band Memory,四倍頻寬記憶體)採用一種‘位填塞’機制,不需要更高時脈頻率的記憶體組件,在不增加記憶體基準頻率的條件下,QBM可以利用現有的DDR記憶體和其它組件,實現了能獲得兩倍數據率的配置。其並不是什麼全新的記憶體架構,也不是什麼全新的記憶體產品,而是一種記憶體控制技術。 QBM

QBM

QBM

QBMQBM與DDR一樣,是通過縮短數據傳輸的時鐘周期來提高傳輸頻寬的,但兩者有有所不同。DDR是通過在時鐘頻率的上下沿都存取數據來實現頻寬倍增的。而QBM則是在此基礎上做了一種改進。一個QBM模組由兩個DDR記憶體模組組成,其中一個模組運行在正常頻率的速度,而另外一個的模組的時鐘周期比前一個模組時鐘周期正好慢90度的相位差,也就是說兩者的工作起始時間相差1/4個時鐘周期,通過這種簡單的方法來讓QBM得到兩倍於DDR記憶體的工作效率,即一個時鐘周期實現了4次數據讀寫。QBM的兩個DDR模組之間採用FET晶片進行連線,而這個FET晶片就起到場效應管的作用--當做延遲開關。這樣就簡單的完成了串聯了兩個DDR模組。

背景

隨著CPU前端匯流排頻寬的提高和高速局部匯流排的出現,例如AGP8X,USB2.0,高速乙太網等,記憶體頻寬成為系統越來越大的瓶頸。因此各種新的記憶體解決方案應運而生,首先要提得是DDR II, 日本的ELPIDA已經推出了每pin數據傳輸率1000Mbps的DDR II顆粒,DDR II還有功耗低、可靠性高等優點。但是各大記憶體產商都認為DDR II成為主流至少要到2004年,悲觀一點得認為2005年DDR II才會成為主流。

2003年的主流記憶體還是DDR333,那么對於高端桌面平台和工作站平台,會採用什麼記憶體解決方案呢。在伺服器平台上Intel已經推出了E7500雙通道DDR晶片組,隨後會推出針對高端桌面系統和工作站的E7502,可以使用雙通過DDR333記憶體,它的記憶體頻寬甚至要比E7500還高(限於 Pentium4Xeon的前端匯流排頻率,E7500隻能支持DDR200和DDR266記憶體模組)。VIA的雙通道DDR晶片組P4X600已經出樣,估計很快就會上市。不過雙通道DDR系統的成本較高,它需要六層PCB板支持,要同時使用兩個模組,在主機板布線上也更加的複雜,因此雙通道DDR系統的定位會比較高,主要是工作站平台。VIA另外引入了一個高頻寬的記憶體技術QBM,QBM的名字並不是第一次聽到了,只是首次有主流記憶體廠商來支持它。QBM可以說是一個向下兼容和成本較低的高頻寬解決方案。

為了滿足日益增加的處理器數據吞吐量的要求,還有高速的圖形局部匯流排,磁碟通道,高速串列匯流排,PCI設備的要求,記憶體架構一直在進行更新換代。從486之後,記憶體就一直成為制約系統性能發展的主要瓶頸之一。雖然記憶體從快頁記憶體發展到 EDO記憶體,然後又發展到 SDRAM記憶體,此時記憶體終於可以和系統時鐘頻率同步了。記憶體匯流排的位寬也從32位發展到64位,頻率也從66MHz到100MHz再到133MHz,記憶體的速度是不斷的提高但總是追不上平台的要求。當SDRAM發展到一個瓶頸時,出現了兩條不同的道路,一條是在SDRAM基礎上發展起來的DDR SDRAM,它通過在一個時鐘周期內的兩倍採樣率來達到頻率倍增的效果。另一條是串列記憶體匯流排RAMBUS,由於串列匯流排的頻率可以做得很高,現在的RDRAM採用了8bit Prefetch,比DDR要先進許多,因此在記憶體頻寬上處於領先地位。但是隨著市場的發展,DDR開始成為主流,而RDRAM的市場萎縮到高端工作站上。在SDRAM的發展過程中也出現過其它一些很有希望的技術,最有可能成功的應該算是QDR,故名思意QDR可以在一個時鐘周期內進行四次數據傳輸,在同樣頻率下記憶體頻寬是DDR的兩倍,而且QDR記憶體仍然使用DDR顆粒,QDR也就是四倍數據傳輸率。不過沒有主流晶片組廠商支持QDR,反而是QBM獲得了VIA的青睞。  記憶體頻寬比較

記憶體頻寬比較

記憶體頻寬比較

記憶體頻寬比較原理

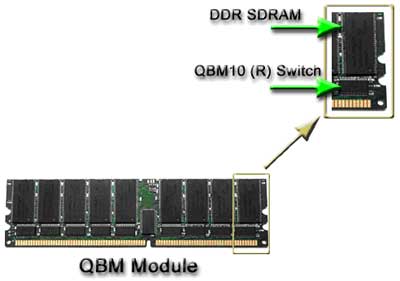

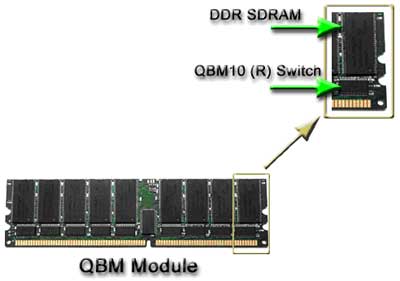

QBM的晶片組簡單地說就是使用了一個傳統的64位DDR SDRAM記憶體接口,其中再整合進支持QBM模組的記憶體控制器。它的一個模組最小需要16片DDR SDRAM顆粒,這些顆粒中的8顆組成第一個段(bank),其它的顆粒組成第二個段。它們分別占用DIMM的兩側,QBM模組仍然採用184pin的接口,和現在的DDR SDRAM模組一樣,接口電氣規範是STTL_2,2.5V工作電壓需要主機板上提供匯流排終結電阻。 QBM模組由DDR SDRAM顆粒和QBM10暫存器構成

QBM模組由DDR SDRAM顆粒和QBM10暫存器構成

QBM模組由DDR SDRAM顆粒和QBM10暫存器構成

QBM模組由DDR SDRAM顆粒和QBM10暫存器構成QBM模組上有8顆暫存器(registers,QBM-10,分別針對8顆DDR SDRAM顆粒),這些暫存器的作用和鎖相環(PLL)電路一樣,通過這個鎖相環電路可以使時鐘信號延遲90度,它把第二個bank的信號的相位進行了90度延遲,而第一個bank仍然使用原始的時鐘相位。 8個暫存器還有FET作用,所謂FET就是一個電路的切換開關,在每個時鐘周期里循環切換兩個bank來傳輸信號,因為有90度的相位延遲,因此在一個時鐘周期中可以傳輸四位數據,也就是說最終的結果是在每個時鐘周期可以得到兩部的DDR數據傳輸率,每pin每個時鐘周期可以傳輸4bit的數據,這也是Quad Band Memory名字的由來。 QBM技術示意圖

QBM技術示意圖

QBM技術示意圖

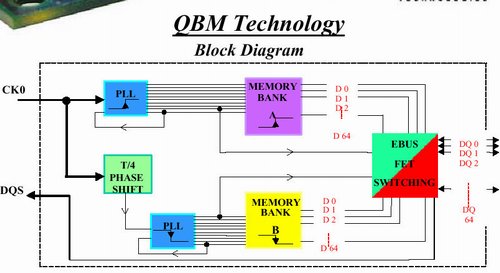

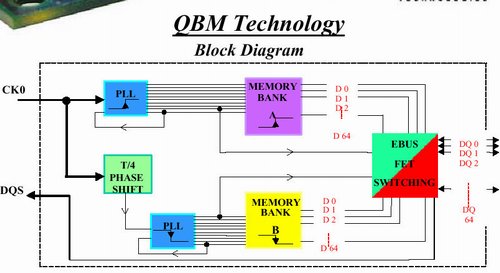

QBM技術示意圖QBM結構在不增加存儲器基準頻率(記憶體匯流排工作頻率)的條件下增加了存儲器子系統的數據頻寬。QBM利用現有的DDR SDRAM和一種"2到1" FET開關;一種具有基準頻率輸出、基準頻率的90度相移輸出以及雙倍基準頻率輸出的鎖相環(PLL)來實現4倍的記憶體頻寬(相對於同基準頻率的SDRAM)。 FET開關工作原理示意圖

FET開關工作原理示意圖

FET開關工作原理示意圖

FET開關工作原理示意圖QBM利用了數據在接收器端(指晶片組中的記憶體控制器)沒有必要保持長時間有效。當基準頻率為100 MHz時,每個DDR器件輸出的數據位的理想保持時間是5納秒。而當接收器的設定和保持時間不足1納秒時,很多時間被浪費掉(接收器等待記憶體數據)。為了降低位時間,就必須提高基準頻率。為了避免高頻帶來的問題,QBM將每個位時間分割,使另外一個有效的數據位插入到前一個數據位沒有占用的時間段內的方法。簡單地說,QBM是一種"位填塞"(bit packing)機制。 下面的時序圖中大家可以比較清楚的看到這種"位填塞"(bit packing)機制,這需要記憶體控制器作一些改進。 QBM將兩顆DDR晶片連線到一個"2到1"的FET開關,它們具有相同的基準頻率,只是其中一個器件的時鐘有90度(或者1/4周期)的相移,因此傳輸到接收器的數據位是DDR所產生的數據位的兩倍。在一個時鐘周期,有四位被"填塞",QBM可以達到DDR I兩倍的數據傳輸率。 QBM的時序圖

QBM的時序圖

QBM的時序圖

QBM的時序圖歷程

前途似錦

2001年1月23~24日,在美國加州聖·喬治召開的Platform Conference會上,美國記憶體模組製造商Kentron展示了QBM技術。通過這種技術可以實現在一個時鐘周期內4次數據傳輸,可以將目前的傳統DDR記憶體在同等工作頻率下,把數據傳輸頻寬提升整整一倍,從根本上解決了DDR記憶體相對於RDRAM記憶體的不足之處,同時這種技術在目前的任何一種DDR記憶體上都能夠發揮同樣的作用。

而負責外部控制QBM運行的重要部件FET模組的成本極低。一顆FET模組僅需要1美元左右,通過這個FET模組,除了可以配合目前的DDR記憶體達到更高的速度以外,還能夠減小系統的功耗,提高記憶體密度以及達到更快的系統匯流排速度,低成本實現高性能。也就是說,QBM記憶體的成本能夠得到很好的控制,其成本理論上同DDR記憶體差不多。

鑒於QBM的良好發展前景,雖然很少有記憶體廠商直接表示對於QBM技術的支持,但是意法電子(ST Micro Electronics)、Integrated Circuit System和Actel三家著名的半導體公司已經公開表示支持QBM技術。Kentron公司也公開表示支持,目前正在和多家公司進行詳細的洽談工作,其中包括DDR記憶體架構的倡導者VIA,以及正在涉足晶片組研發領域的顯示卡業界霸主NVIDIA公司。同時業界也傳出了有關SiS、ALi等晶片組廠商以及ATi意在支持QBM的傳言。

風光無限

2003年8月,QuakeCon遊戲大會上VIA首次展示了其Intel Pentium4平台最新晶片組PT880,並宣布該晶片組除了會支持雙通道傳統DDR記憶體的同時還會支持雙通道QBM記憶體,使得一時間該晶片備受關注。

公開露面

在Compute x2004展會上,VIA首次公開展示其QBM記憶體,演示了QBM記憶體在p4平台上的工作。展示的產品似乎使用雙通道工作模式,QMB記憶體的工作頻率為533MHz,可看到記憶體產品在2004年4月21日出廠,但它仍只是一款工程樣品。 QBM晶片組樣品

QBM晶片組樣品

QBM晶片組樣品

QBM晶片組樣品