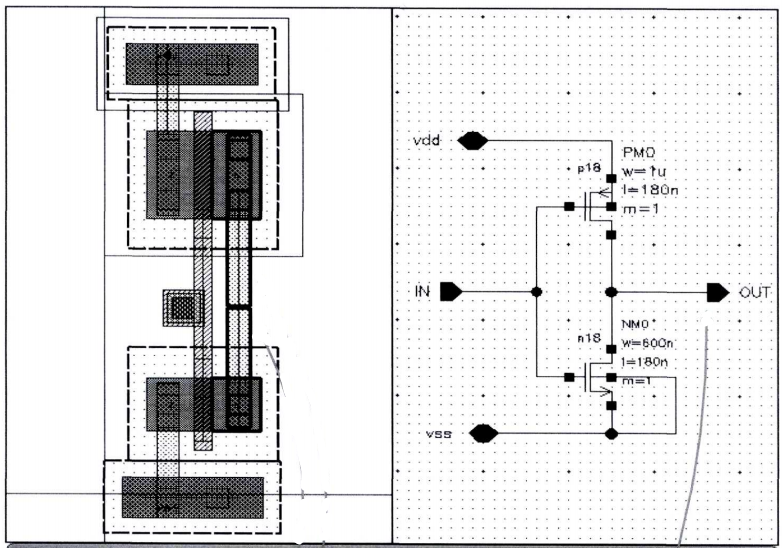

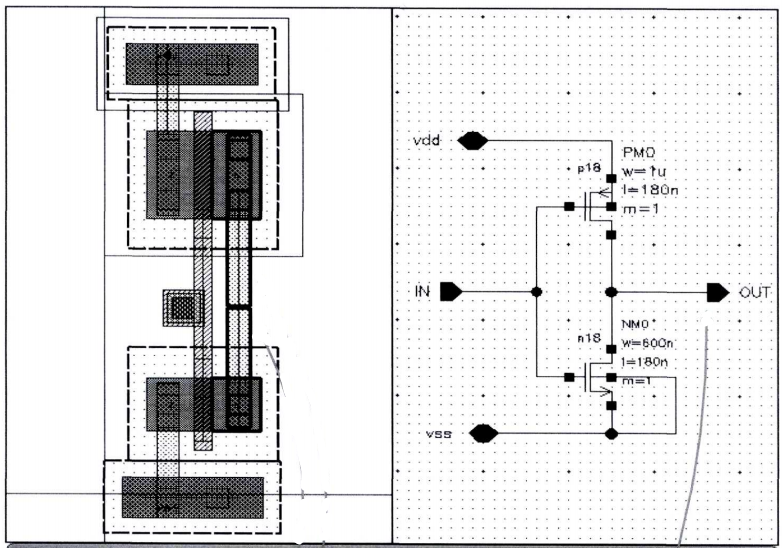

電路規則檢查屬於積體電路設計物理驗證的一部分。其主要目的是驗證版圖與電路原理圖的電路結構是否一致。 電路設計者完成電路設計和仿真後交由版圖設計者完成掩模工作。 確保所畫版圖與設計電路完全一致就是 LVS 工具要做的工作。LVS檢查的內容可以槪括為兩點:①所有信號的電氣連線關係是否一致;②器件類型尺寸是否一致。

基本介紹

- 中文名:電路規則檢查

- 外文名:Layout versus schematic

- 屬於:積體電路設計物理驗證

- 英文縮寫:LVS

電路規則檢查屬於積體電路設計物理驗證的一部分。其主要目的是驗證版圖與電路原理圖的電路結構是否一致。 電路設計者完成電路設計和仿真後交由版圖設計者完成掩模工作。 確保所畫版圖與設計電路完全一致就是 LVS 工具要做的工作。LVS檢查的內容可以槪括為兩點:①所有信號的電氣連線關係是否一致;②器件類型尺寸是否一致。

電路規則檢查屬於積體電路設計物理驗證的一部分。其主要目的是驗證版圖與電路原理圖的電路結構是否一致。 電路設計者完成電路設計和仿真後交由版圖設計者完成掩模工作...

電路檢查是益智小遊戲。...... 愛新奇旦為了保證每塊電路板能正常使用,唯有一塊塊的檢查,小倉鼠...編輯規則 本人編輯 我有疑問 我要質疑 線上客服 參加討論 意見...

版圖設計規則檢查是集成電路設計物理驗證的一部分,晶圓代工廠對各自不同工藝參數制定出滿足晶片製造良率的同一工藝層及不同工藝層之間幾何尺寸的約束,這些尺寸規劃的...

內容包括電路故障檢修前的準備工作、常用工具和儀表的使用方法,使用萬用表檢查...編輯規則 百科術語 我有疑問 我要質疑 線上客服 參加討論 意見反饋 投訴建議 舉報...

電路圖的畫法規則:1.電路圖的信號處理流程方向;2.連線導線 電路圖 實例 ;3.電源線與地線電路圖的識圖方法與步驟。電路的識別包括正確電路和錯誤電路的判斷,串聯...

8.6.3 設定布線層面規則8.6.4 啟動自動布線8.7 電路板布線的調整及3D圖觀察8.7.1 布線的調整8.7.2 電路板3D圖的觀察8.7.3 PCB製作完成後的進一步檢查8...

(2)通電檢查把經過準確測量符合要求的電源電壓接入電路。電源一經接通,不要急於...編輯規則 本人編輯 我有疑問 內容質疑 線上客服 官方貼吧 意見反饋 投訴建議 舉報...

EDA)是指利用計算機輔助設計(CAD)軟體,來完成超大規模集成電路(VLSI)晶片的功能設計、綜合、驗證、物理設計(包括布局、布線、版圖、設計規則檢查等)等流程的設計方式...

電路設計,是指按照一定規則,使用特定方法設計出符合使用要求的電路系統。...... 電路設計,是指按照一定規則,使用特定方法設計出符合使用要求的電路系統。...

分析中,需要對集成電路的輸入輸出連線埠的性質進行仔細檢查,這時要套用精確的電路...編輯規則 本人編輯 我有疑問 我要質疑 線上客服 參加討論 意見反饋 投訴建議 舉報...

攜帶型顯微鏡檢測電路板 1.電路板故障部位的不完全統計:1)晶片損壞30%, 2)...已有很多公司開始在自己的網站上建一個電路板計價程式,通過一些規則,讓客戶自由...

PCB( Printed Circuit Board),中文名稱為印製電路板,又稱印刷線路板,是重要的...複查根據“PCB檢查表”,內容包括設計規則,層定義、線寬、間距、焊盤、過孔設定;...

模擬集成電路設計涉及了更加複雜的信號環境,對工程師的經驗有更高的要求,並且其設計的自動化程度遠不及數字集成電路。逐步完成功能設計之後,設計規則會指明哪些設計...

時序邏輯電路檢查電源 時序邏輯電路較常採用±5V、±15V、±12V電源。當電源對...編輯規則 本人編輯 我有疑問 我要質疑 線上客服 參加討論 意見反饋 投訴建議 舉報...

功能檢測套用 套用電子技術方面的測試:印刷電路板,又稱印製電路板,印刷線路板,...⑤在規定了輸入數據必須遵守的規則的情況下,可確立一個有效等價類(符合規則)和...

放大電路的前置部分或集成電路元件變質引起高頻振蕩產生"噝噝"聲,檢查各部分元件,...編輯規則 本人編輯 我有疑問 內容質疑 線上客服 官方貼吧 意見反饋 投訴建議 舉報...

《Altium Designer 15.0電路仿真、設計、驗證與工藝實現權威指南》是2015年出版...19.4.3測試點設計規則設定19.4.4測試點管理19.4.5檢查測試點的有效性...