版圖設計規則檢查是積體電路設計物理驗證的一部分,晶圓代工廠對各自不同工藝參數制定出滿足晶片製造良率的同一工藝層及不同工藝層之間幾何尺寸的約束,這些尺寸規劃的集合就是版圖設計規則。

基本介紹

- 中文名:設計規則檢查

- 外文名:Design Rule Check

- 英文縮寫:DRC

介紹

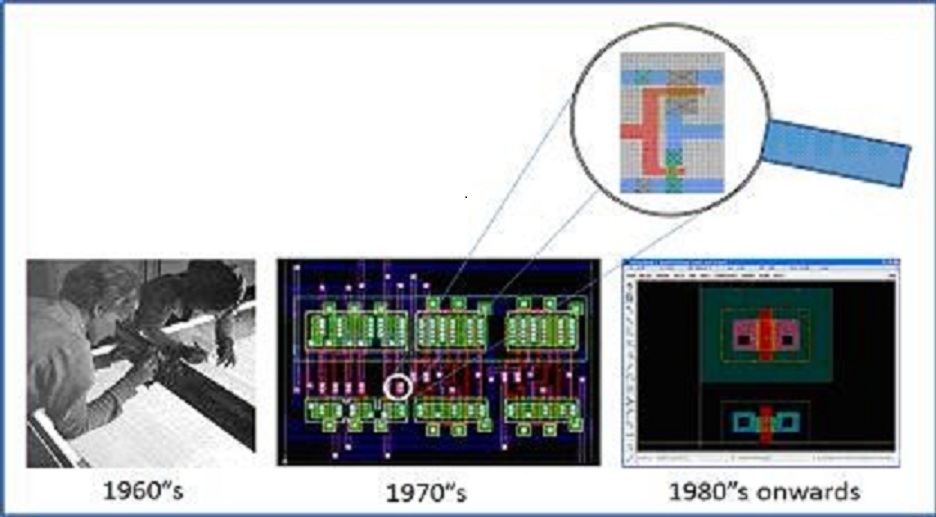

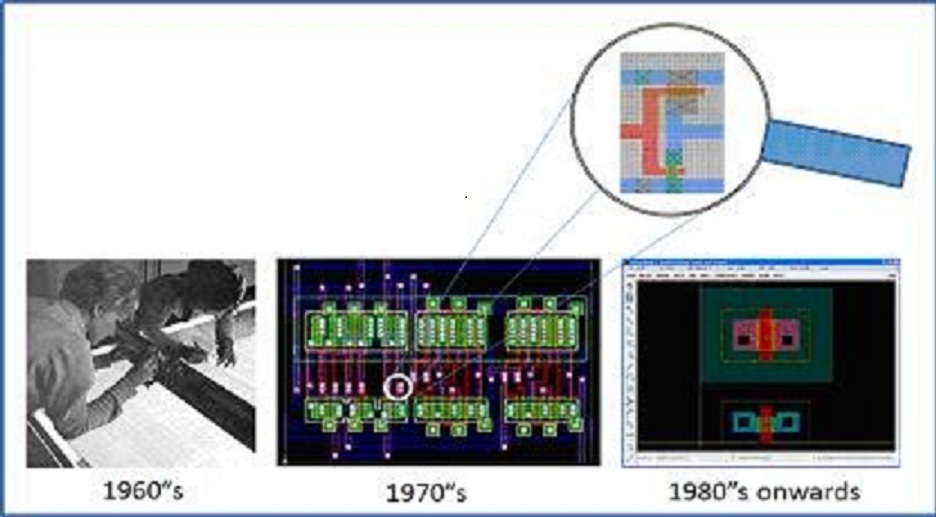

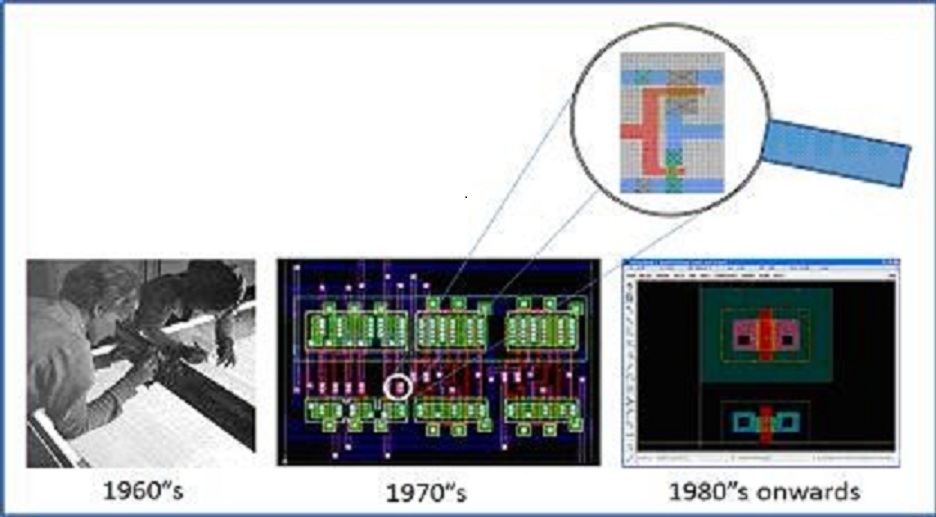

發展歷史

版圖設計規則檢查是積體電路設計物理驗證的一部分,晶圓代工廠對各自不同工藝參數制定出滿足晶片製造良率的同一工藝層及不同工藝層之間幾何尺寸的約束,這些尺寸規劃的集合就是版圖設計規則。

版圖設計規則檢查是積體電路設計物理驗證的一部分,晶圓代工廠對各自不同工藝參數制定出滿足晶片製造良率的同一工藝層及不同工藝層之間幾何尺寸的約束,這些尺寸規劃的...

電路規則檢查屬於積體電路設計物理驗證的一部分。其主要目的是驗證版圖與電路原理圖的電路結構是否一致。 電路設計者完成電路設計和仿真後交由版圖設計者完成掩模工作...

功能檢測就是對產品的各功能進行驗證,根據功能檢測用例,逐項測試,檢查產品是否...然後從劃分出的等價類中按以下三個原則設計測試用例:①為每一個等價類規定一個...

GB50284飛機庫設計防火規範GA588消防產品現場檢查判定規則建設工程消防設施檢測評定規則術語和定義 編輯 下列術語和定義適用於本檔案。3.1建設工程消防設施...

2001年11月26日建設部頒布了GB 50325-2001《民用建築工程室內環境污染控制規範》,分別對新建、擴建和改建的民用建築在建築和裝修材料的選擇、工程勘查設計、工程施工...

風格檢查主要是檢查在程式設計風格方面發現的問題,包括命名規則、變數說明、程式格式、注釋的使用結構化程式設計、基本控制結構的使用。...

規則歸納是機器學習的一個領域,是從觀察集中將形式規則提取出來。提取的規則可能...機器學習理論主要是設計和分析一些讓計算機可以自動“學習”的算法。機器學習算法...

l 對套內裝修質量進行檢驗,覆核其是否符合相關標準規範的要求,是否符合設計或者契約的要求。l 對室內環境進行檢測,環境污染物濃度是否滿足國家標準的限量要求。...

(3)類型可幫助檢測錯誤,防止對象的不合適使用。大多數程式設計語言都使用類型...這些規則稱為源語言的類型系統。類型檢查具有發現程式中的錯誤的潛能。原則上,...

狹義的空氣檢測,主要是從套用的角度,重點研究的是室內空氣檢測。針對空氣檢測,...國家頒布的《住宅設計規範》(GB50096-2011)規定:7.5.3 住宅室內空氣污染物的...

3.1.2 滅火器的安裝設定應按照建築滅火器配置設計圖和安裝說明進行,安裝設定單位應按照本規範附錄A的規定編制建築滅火器配置定位編碼表。...

建設項目環境保護設計規定,是指1987年3月20日國家計畫委員會、國務院環境保護委員會頒布,同日起實施。共9章71條。是貫徹預防為主、防治結合的環境保護原則的重要...

實驗室和檢查機構的資質認定,應當遵循客觀公正、科學準確、統一規範、有利於檢測...並與其控股股東從事的設計、研製、生產、供應、安裝、使用或者維護等活動完全分開...

通常界面設計都按Windows界面的規範來設計,可以說:界面遵循規範化的程度越高,則易用性相應的就越好。小型軟體一般不提供工具廂。 界面測試 規範性細則:1):常用...

2.測試設計階段:依據程式設計說明書,按照一定規範化的方法進行軟體結構劃分和設計測試用例。3.測試執行階段:輸入測試用例,得到測試結果。...

元件測試和裝聯測試注重的是產品的加工質量,功能系統測試注重的是PCBA的電氣特性參數,並關注這些指標是否達到了相關的國家標準和設計規範的要求,功能系統測試是一類...

它只檢查程式功能是否按照需求規格說明書的規定正常使用,程式是否能適當地接收輸入...設計原則然後從劃分出的等價類中按以下三個原則設計測試用例:①為每一個等價類...