專利背景

CMOS電路中,有三部分功耗來源,即P

total=P

switching+P

short+P

leakage。其中P

total是一個CMOS電路的總功耗,P

switching是開關功耗,大小取決於負載電容的充放電;P

leakage是漏電功耗。截至2011年5月,

晶片中最主要的功耗是開關功耗,但是隨著低閾值電壓技術在低功耗設計中的套用,短路功耗和漏電功耗也會變得越來越重要。

其中開關功耗Pswitching=VDD×fclk×ΣαiCLiΔVi,VDD是電源電壓;fclk是時鐘頻率;如果一個電路包含n個結點,ai是每秒鐘信號變化的次數,即開關活動因子;CLi是結點電容;ΔVi是結點i的電壓變化幅度。

短路功耗發生在信號的翻轉瞬間,當輸入信號的值在|Vth|和VDD-|Vtp|之間的時候,PMOS和NMOS同時導通,造成VDD到GND的短路電流。短路功耗可以表示為Pshort=VDDIshort,Ishort為短路電流。

漏電流功耗Pleakage=VDDIleakage,Ileakage是CMOS電路的漏電流,主要由亞閾值效應以及漏源區與襯底反向偏置而引起的。對於深亞微米套用,這一項尤其重要。

從上述分析可以知道,功耗與很多因素相關,如開關活動因子、等效電容、電源電壓、工作頻率、短路電流、漏電流等。低功耗的設計方法就是從這幾個基本因素出發,分別降低這些影響因素以便達到降低功耗的目的。

在電能表系統套用中,對整機的功耗有著嚴格的規定,例如在電池供電的情況下,要求能夠工作5年以上。在電能表的系統晶片解決方案中,整機的功耗主要來自計量系統晶片,因此需要設計一種方法能涵蓋該系統晶片的各個工作狀態,以達到降低功耗的目的。

發明內容

專利目的

《電能計量晶片降低功耗的方法》的目的在於提供一種能涵蓋該系統晶片的各個工作狀態,以達到降低功耗的電能計量晶片降低功耗的方法。

技術方案

實施《電能計量晶片降低功耗的方法》的電能計量晶片降低功耗的方法,該電能計量晶片設有兩個時鐘域,其中該電能計量晶片的CPU位於時鐘域一,並且該電能計量晶片還包括計量電路,計量電路包括功率有效值計算電路與能量累加電路,該二電路均位於時鐘域二,時鐘域一選擇使用低頻時鐘與高頻時鐘,並可停止動作並維持恆定電平,時鐘域二選擇使用低頻時鐘、降頻時鐘及高頻時鐘,並可停止動作維持恆定電平,並且該電能計量晶片可選擇通過電池或電力線供電,該方法包括如下步驟:

電能計量晶片判斷是通過電池還是電力線供電;

如果該電能計量晶片通過電池供電,則計量電路檢測電壓輸入信號的有效值是否小於一設定閾值,同時電流輸入信號的有效值是否大於一設定閾值?如是,則令時鐘域一使用高頻時鐘,時鐘域二使用高頻時鐘,計量電路計算電流輸入的電流有效值,並把得到的電流有效值設定為能量累加電路的固定輸入,並通過暫存器設定使功率有效值計算電路中的所有觸發器輸入不發生變化,之後令時鐘域一停止動作維持恆定電平;如否,則令時鐘域一和時鐘域二停止動作維持恆定電平;

如果該電能計量晶片是通過電力線供電,則計量電路檢測電壓輸入信號的有效值是否小於某個閾值,如是則時鐘域一使用介於低頻時鐘與高頻時鐘之間的時鐘,而時鐘域二使用降頻時鐘;如否,則進入正常工作模式,時鐘域一與二均使用高頻時鐘。

依據上述主要特徵,時鐘域一與時鐘域二停止動作維持恆定電平之後,晶片持續判斷是否有恢復供電復位或者IO休眠喚醒復位發生,如有則返回判斷該電能計量晶片是通過電池還是電力線供電,如否則時鐘域與與時鐘域二保持停止動作並維持恆定電平。

依據上述主要特徵,時鐘域一與時鐘域二保持停止動作並維持恆定電平狀態達到一定時間後,發生定時復位喚醒,重複休眠前的操作,並再次進入保持停止動作並維持恆定電平狀態,上述循環重複達到預設的次數後,則晶片進入深休眠狀態,即只有電池供電變為正常供電與系統晶片的IO輸入發生變化才令晶片喚醒復位。

依據上述主要特徵,在時鐘域一使用高頻時鐘,時鐘域二使用高頻時鐘,計量電路計算電流輸入的電流有效值,並把得到的電流有效值設定為能量累加電路的固定輸入,並通過暫存器設定使功率有效值計算電路中的所有觸發器輸入不發生變化,之後令時鐘域一停止動作維持恆定電平後,系統持續判斷是否有恢復供電復位或者IO休眠喚醒復位或者定時休眠喚醒復位發生,如有則返回判斷該電能計量晶片是通過電池還是電力線供電,如否則重複上述過程。

依據上述主要特徵,該晶片使用一個輸入引腳來判斷當前的供電狀態,定義PWRUP信號標誌為從這個輸入引腳得到的供電狀態,PWRUP=0表示晶片由電池供電,PWRUP=1表示晶片由電力線供電。

依據上述主要特徵,時鐘域一的低頻時鐘為32768赫茲、高頻時鐘為32768xN,其中N為PLL倍頻係數,N的典型值為100,時鐘域二的低頻時鐘為32768赫茲、降頻時鐘為204800赫茲、高頻時鐘為819200赫茲,典型值為32768x100。

依據上述主要特徵,如果該電能計量晶片是通過電力線供電,且計量電路檢測電壓輸入信號的有效值小於某個閾值,則時鐘域一使用32768xN赫茲時鐘,其中N<100,典型值為32768x25赫茲。

依據上述主要特徵,如果該電能計量晶片是通過電力線供電,且計量電路檢測電壓輸入信號的有效值小於某個閾值,在CPU處理任務的空閒時刻,時鐘域一的所有觸發器的輸入都不再發生變化,直到有其他任務時,時鐘域一才退出上述狀態。

依據上述主要特徵,晶片進入正常工作模式時,時鐘域一使用3.2768兆赫時鐘。

改善效果

《電能計量晶片降低功耗的方法》通過為電能計量系統晶片設定多種時鐘狀態,並根據系統晶片當前的供電狀態以及休眠喚醒復位的產生來源進行時鐘狀態的轉換,從而利於降低電能計量系統晶片的功耗。

附圖說明

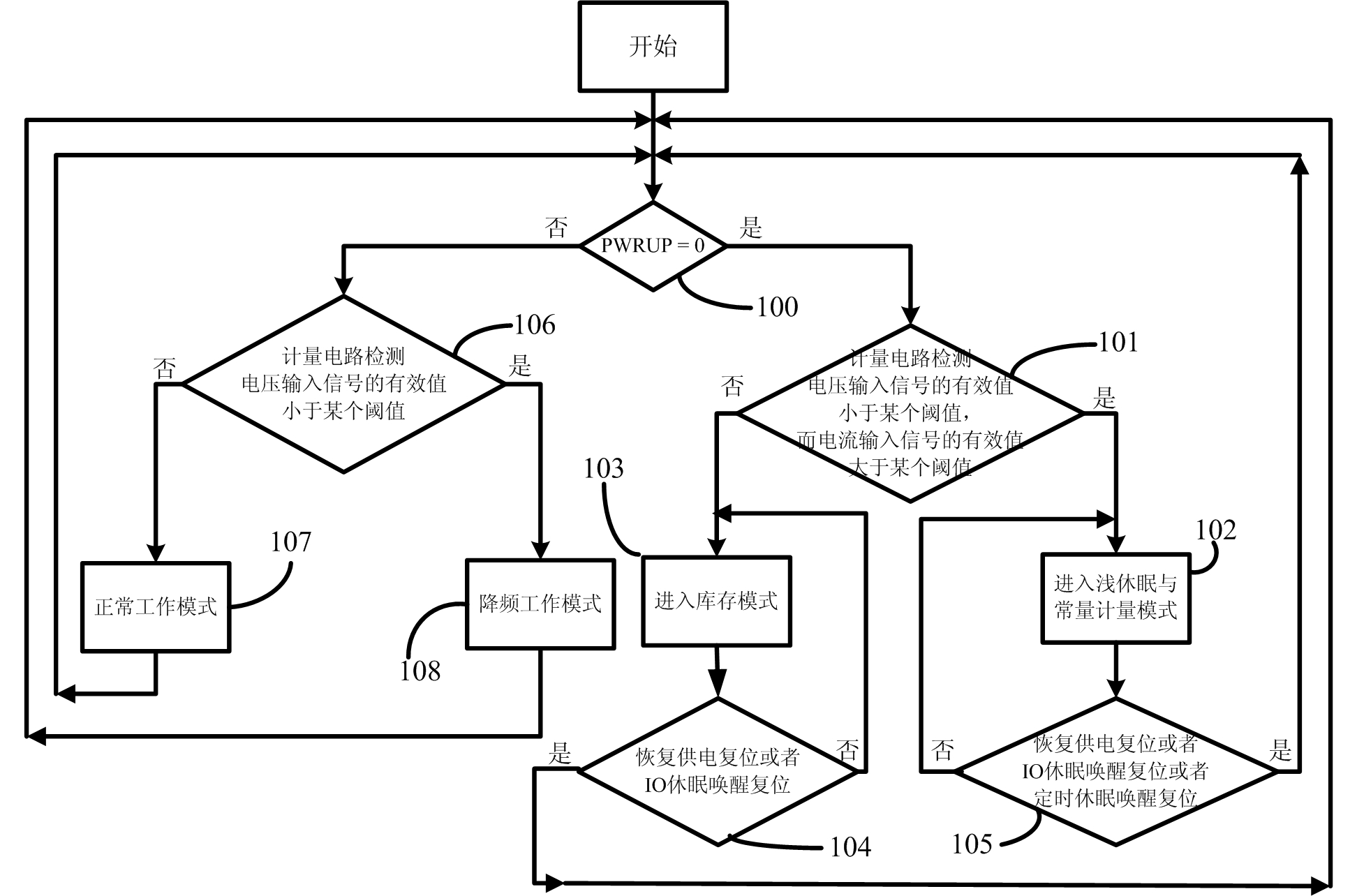

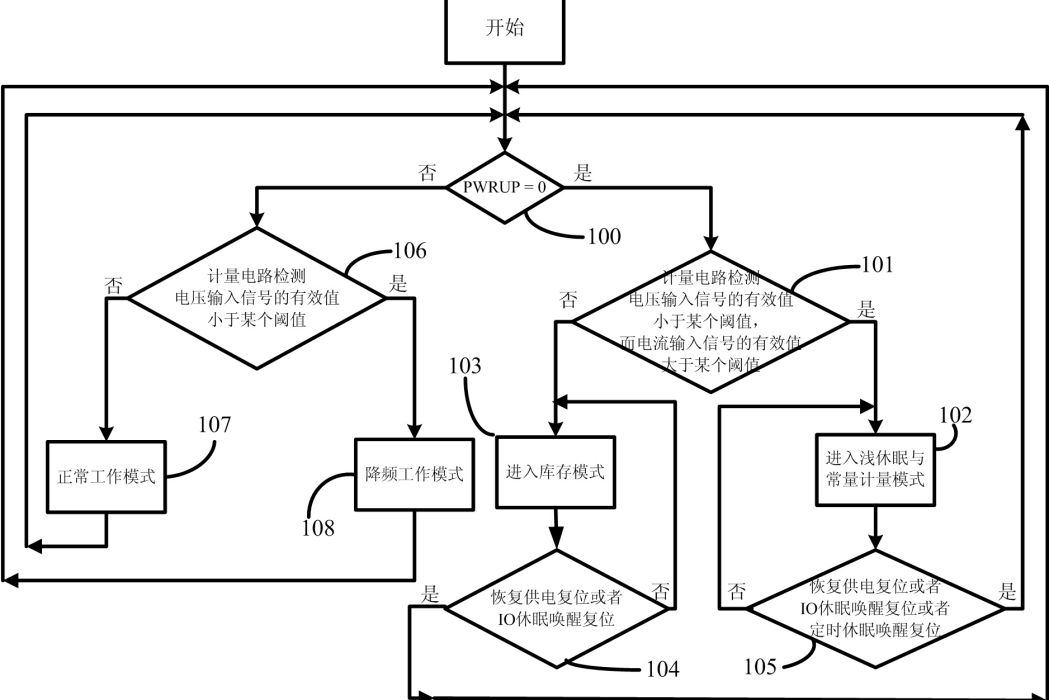

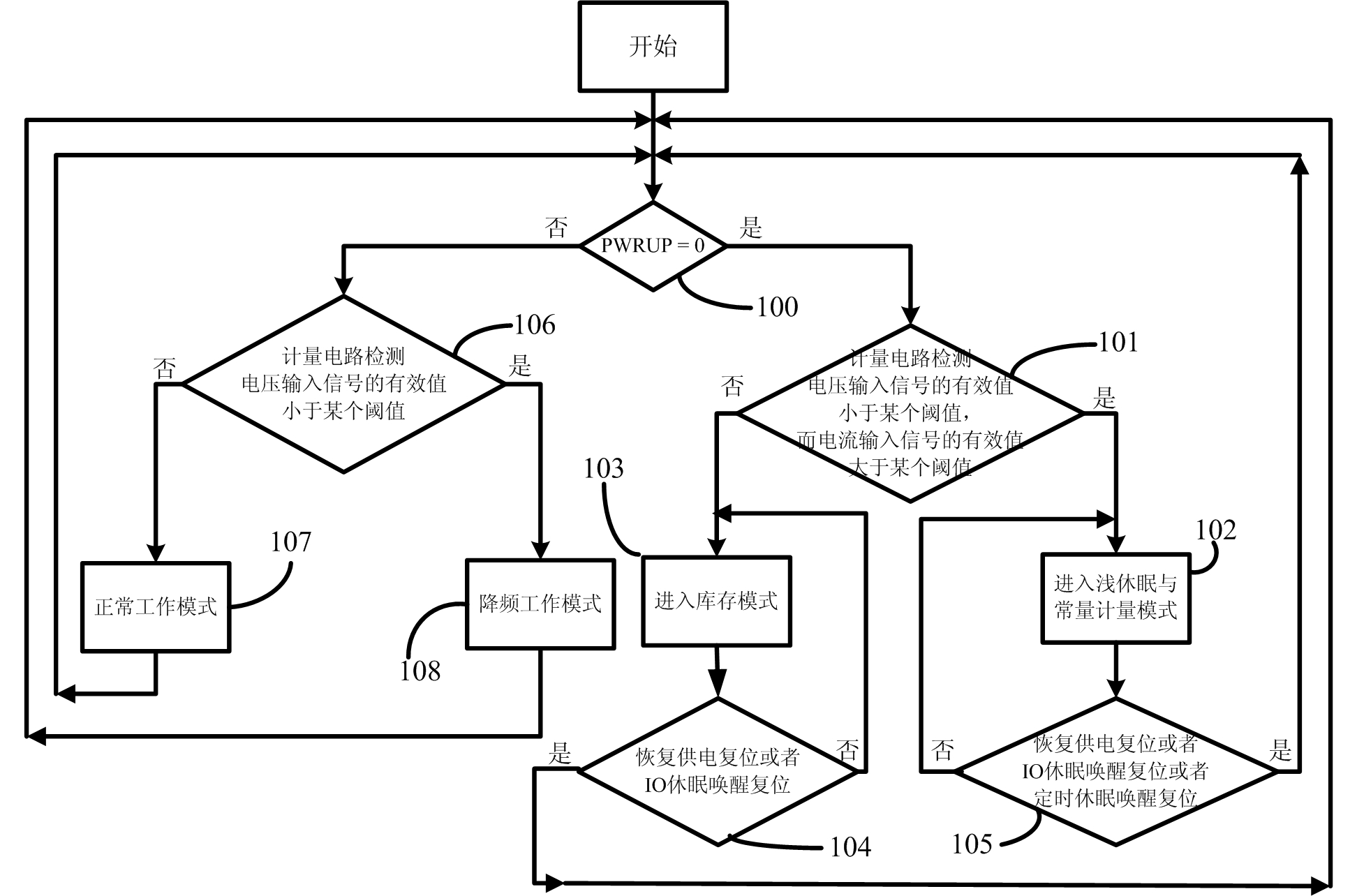

圖1為實施《電能計量晶片降低功耗的方法》的電能計量晶片降低功耗的方法的流程圖。

技術領域

《電能計量晶片降低功耗的方法》有關一種降低功耗的方法,特別是指套用於電能計量晶片中,用來降低電能計量晶片的功耗的方法。

權利要求

1.一種電能計量晶片降低功耗的方法,該電能計量晶片設有兩個時鐘域,其中該電能計量晶片的CPU位於時鐘域一,並且該電能計量晶片還包括計量電路,計量電路包括功率有效值計算電路與能量累加電路,該二電路均位於時鐘域二,時鐘域一選擇使用低頻時鐘與高頻時鐘,並可停止動作並維持恆定電平,時鐘域二選擇使用低頻時鐘、降頻時鐘及高頻時鐘,並可停止動作維持恆定電平,並且該電能計量晶片可選擇通過電池或電力線供電,該方法包括如下步驟:電能計量晶片判斷是通過電池還是電力線供電;如果該電能計量晶片通過電池供電,則計量電路檢測電壓輸入信號的有效值是否小於一設定閾值,同時電流輸入信號的有效值是否大於一設定閾值;如是,則令時鐘域一使用高頻時鐘,時鐘域二使用高頻時鐘,計量電路計算電流輸入的電流有效值,並把得到的電流有效值設定為能量累加電路的固定輸入,並通過暫存器設定使功率有效值計算電路中的所有觸發器輸入不發生變化,之後令時鐘域一停止動作維持恆定電平;如否,則令時鐘域一和時鐘域二停止動作維持恆定電平;如果該電能計量晶片是通過電力線供電,則計量電路檢測電壓輸入信號的有效值是否小於某個閾值,如是則時鐘域一使用32768xN赫茲時鐘,其中N<100,而時鐘域二使用降頻時鐘;如否,則進入正常工作模式,時鐘域一與二均使用高頻時鐘。

2.如權利要求1所述的電能計量晶片降低功耗的方法,其特徵在於:時鐘域一與時鐘域二停止動作維持恆定電平之後,晶片持續判斷是否有恢復供電復位或者IO休眠喚醒復位發生,如有則返回判斷該電能計量晶片是通過電池還是電力線供電,如否則時鐘域一與時鐘域二保持停止動作並維持恆定電平。

3.如權利要求1所述的電能計量晶片降低功耗的方法,其特徵在於:在時鐘域一使用高頻時鐘,時鐘域二使用高頻時鐘,計量電路計算電流輸入的電流有效值,並把得到的電流有效值設定為能量累加電路的固定輸入,並通過暫存器設定使功率有效值計算電路中的所有觸發器輸入不發生變化,之後令時鐘域一停止動作維持恆定電平後,系統持續判斷是否有恢復供電復位或者IO休眠喚醒復位或者定時休眠喚醒復位發生,如有則返回判斷該電能計量晶片是通過電池還是電力線供電,如否則重複上述過程。

4.如權利要求1所述的電能計量晶片降低功耗的方法,其特徵在於:該晶片使用一個輸入引腳來判斷當前的供電狀態,定義PWRUP信號標誌為從這個輸入引腳得到的供電狀態,PWRUP=0表示晶片由電池供電,PWRUP=1表示晶片由電力線供電。

5.如權利要求1所述的電能計量晶片降低功耗的方法,其特徵在於:時鐘域一的低頻時鐘為32768赫茲、高頻時鐘為32768xN,其中N為PLL倍頻係數,時鐘域二的低頻時鐘為32768赫茲、降頻時鐘為204800赫茲、高頻時鐘為819200赫茲。

6.如權利要求5所述的電能計量晶片降低功耗的方法,其特徵在於:時鐘域一的高頻時鐘的典型值為32768x100。

7.如權利要求1所述的電能計量晶片降低功耗的方法,其特徵在於:如果該電能計量晶片是通過電力線供電,且計量電路檢測電壓輸入信號的有效值小於某個閾值,則時鐘域

一使用32768x25赫茲時鐘。

8.如權利要求1所述的電能計量晶片降低功耗的方法,其特徵在於:如果該電能計量晶片是通過電力線供電,且計量電路檢測電壓輸入信號的有效值小於某個閾值,在CPU處理任務的空閒時刻,時鐘域一的所有觸發器的輸入都不再發生變化,直到有其他任務時,時鐘域一才退出上述狀態。

9.如權利要求1所述的電能計量晶片降低功耗的方法,其特徵在於:晶片進入正常工作模式時,時鐘域一使用3.2768兆赫時鐘。

實施方式

為了實現降低功耗的目的,《電能計量晶片降低功耗的方法》為電能計量系統晶片設定多種時鐘狀態,並根據系統晶片當前的供電狀態以及休眠喚醒復位的產生來源進行時鐘狀態的轉換。

在本實施例中,使用系統晶片的一個輸入引腳來判斷當前的供電狀態,定義PWRUP信號標誌為從這個輸入引腳得到的供電狀態,PWRUP=0表示晶片由電池供電,PWRUP=1表示晶片由電力線供電,即正常供電。

系統晶片內部設定兩個時鐘域,CPU位於時鐘域1,而計量電路包括功率有效值計算電路與能量累加電路,該二電路均位於時鐘域2,兩個時鐘域分別使用獨立的時鐘。每個時鐘域的時鐘都可以由CPU運行的控制軟體分別進行控制,時鐘域1可以使用32768赫茲(低頻時鐘)以及32768xN(N為PLL倍頻係數,N的典型值為100)赫茲(高頻時鐘),並可以被門控,即時鐘域1的時鐘停止動作,維持一個恆定電平。時鐘域2可以使用32768赫茲(低頻時鐘)、204800赫茲(降頻時鐘)、819200赫茲(高頻時鐘),並可以被門控,即時鐘域2的時鐘停止動作,維持一個恆定電平。關於門控時鐘的過程,具體原理如下:

2.電路查找時鐘的上升沿;

3.由於上升沿是從低電平到高電平的一個過程,電路在檢測到時鐘的上升沿後,等待適當的延時以便時鐘的電平變化過程穩定,然後電路根據此暫存器的值輸出一個高電平或者低電平;

4.此高電平或者低電平與時鐘信號進行“或操作”,輸出的信號作為門控之後的信號;

5.如上所述,當控制暫存器的值無效的時候,門控電路輸出的是低電平,和時鐘信號進行或操作後,時鐘信號依然保持原來的頻率,只是相位稍有延遲;當控制暫存器的值有效的時候,門控電路輸出的是高電平,和時鐘信號進行或操作後,輸出的時鐘信號變為恆定的高電平,即被門控。

在系統晶片上電復位後的初始狀態下,時鐘域1使用32768赫茲時鐘,時鐘域2使用32768赫茲時鐘。

在PWRUP=0的情況下,時鐘域1可以使用低頻時鐘、高頻時鐘、或者被門控;時鐘域2可以使用低頻時鐘、降頻時鐘、高頻時鐘、或者被門控。在PWRUP=1的情況下,時鐘域1可以使用低頻時鐘、高頻時鐘,但是不能被門控;時鐘域2可以使用低頻時鐘、降頻時鐘、高頻時鐘,但是也不能被門控。

定義時鐘域1被門控的狀態為晶片的休眠狀態,而休眠狀態又分為淺休眠和深休眠兩種狀態。在淺休眠狀態下,當PWRUP從0變為1(電池供電變為正常供電)、IO事件(系統晶片的IO輸入發生變化)或者休眠達到一定時間(對進入休眠狀態的時間進行計時,達到某個閾值)都可以產生一個喚醒復位,從而使晶片回到初始狀態。在深休眠狀態下,只有PWRUP從0變為1(電池供電變為正常供電)、IO事件(系統晶片的IO輸入發生變化)可以產生喚醒復位,休眠時間不能作為產生喚醒復位的依據。

在時鐘域1的時鐘不被門控的情況下,通過暫存器設定使時鐘域1中的所有觸發器的輸入都不再發生變化,定義這種狀態為時鐘域1的掛起狀態。

時鐘域2中的電路分為兩個部分,功率/有效值計算電路以及能量累加電路。在時鐘域2的時鐘不被門控的情況下,通過暫存器設定使功率/有效值計算電路中的所有觸發器的輸入都不再發生變化,並可以設定能量累加電路的輸入為某個固定值,定義這種狀態為時鐘域2的常量計量狀態。

參閱圖1所示,為實施《電能計量晶片降低功耗的方法》的電能計量晶片降低功耗的方法的流程圖,該方法包括如下步驟:

步驟100:判斷PWRUP是否為0?

步驟101:如是,則判斷計量電路檢測電壓輸入信號的有效值是否小於某個閾值,並且電流輸入信號的有效值是否大於某個閾值?

如是,則進入步驟102,即進入淺休眠與常量計量模式,之後持續判斷是否有恢復供電復位或者IO休眠喚醒復位或者定時休眠喚醒復位發生,即步驟105,如有則回到步驟100,如否則保持為淺休眠與常量計量模式。其中淺休眠與常量計量模式是指時鐘域1使用高頻時鐘,時鐘域2使用高頻時鐘,計量電路計算電流輸入的電流有效值,並把得到的電流有效值設定為能量累加電路的固定輸入,並通過暫存器設定使功率有效值計算電路中的所有觸發器輸入不發生變化,即時鐘域2進入常量計量狀態,之後令時鐘域一停止動作維持恆定電平,即晶片進入淺休眠狀態。此特別適用於在某些竊電行為發生的時候,電流互感器產生的功率太小不足以讓晶片工作,或者電能表中不存在電流互感器元件,或者為正常的停電狀態,此時晶片完全由電能表中的電池供電。設時鐘域1使用高頻時鐘的時間為t(即計算獲得電流有效值的時間),保持淺休眠狀態的時間為T。由於能量累加電路相比功率/有效值計算電路面積極小,其功耗相比也可以忽略,且時鐘域2進入常量計量狀態後,僅有與時鐘電路相關的功耗,其功耗也可以忽略的情況下,則晶片的平均功耗為(Pswitching+Pshort)t/T+Pleakage。

如否,則進入庫存模式,即步驟103,之後持續判斷是否有恢復供電復位或者IO休眠喚醒復位發生,即步驟104,如有則回到步驟100,如否則保持為庫存模式。其中在庫存模式,系統門控時鐘域2的時鐘,並使晶片進入淺休眠狀態,即此時時鐘域1與時鐘域2均被門控,處於停止動作維持恆定電平狀態。休眠達到一定時間後,發生定時復位喚醒,重複休眠前的操作,並再次進入淺休眠。上述循環重複達到預設的次數後,如果在之前的過程中始終沒有發生PWRUP從0變為1或者IO事件或者計量電路檢測電壓和電流輸入的有效值超出閾值的事件,則門控時鐘域2的時鐘,使晶片進入深休眠狀態。在庫存模式下,只有恢復供電或者發生IO事件才能使晶片離開庫存狀態,否則,晶片會一直處於深休眠狀態,維持在極低功耗的狀態。在庫存模式下,Pswitching=VDD×fclk×ΣαiCLiΔVi中的fclk為0,Pswitching為0,從而Pshort也為0,晶片只剩下Pleakage。根據晶片的製造工藝,整個晶片的漏電流維持在幾百納安培。

當在步驟100中判斷PWRUP不為0時,計量電路檢測電壓輸入信號的有效值是否小於某個

閾值,即步驟106。

如是,則進入降頻工作模式,即步驟108。其中降頻工作模式時,因PWRUP=1,根據晶片時鐘狀態的描述,時鐘域1和時鐘域2都不能被門控。為了降低功耗,時鐘域1使用32768xN(N<100,N的典型值為25)赫茲時鐘,時鐘域2使用降頻時鐘。並且在CPU處理任務的空閒時刻,時鐘域1進入掛起狀態,直到有其他應該處理的任務的時候(例如中斷或者定時達到預設閾值),時鐘域1才退出掛起狀態。即在降頻模式下,時鐘域1和時鐘域2降低了工作頻率,時鐘域2中的電路正常工作,正常計量電量。時鐘域1中的電路間歇性的對外界事件做出回響。此適用於發生竊電行為且電壓輸入信號為0的時候,電能表裡面的電流互感器能夠產生感應電壓,並為晶片供電。由於

電流互感器產生的功率有限,不足以支持晶片的正常功耗,所以要求此時晶片能夠工作,但是可以降低計量精度以及處理任務的能力。在降頻工作模式下,P

switching=VDD×f

clk×Σα

iC

LiΔV

i中的f

clk降為正常狀態下的1/4,且時鐘域1中的大部分a

i在掛起狀態下為0,只有與時鐘相關的電路的a

i不等於0,從而時鐘域1中的大部分電路的P

switching為0,從而相關的P

short也為0。晶片只剩下P

leakage、降低為正常狀態下1/4的時鐘域2的P

swithcing,以及時鐘域1中的前述的相關功耗。

如否,則進入正常工作模式,即步驟107,在正常工作模式下,時鐘域1使用3.2768兆赫時鐘(即N=100),時鐘域2使用819200赫茲時鐘,所有的電路均處於正常翻轉狀態,即Pswitching中的f,ai,deltavi均為正常值,時鐘電路的功耗也處於正常狀態。

從以上的描述中可以看出,在休眠狀態下f為0,Pswitching=0,且時鐘電路功耗也為0,而在掛起狀態下,ai為0,Pswitching=0,僅存在時鐘電路功耗;在降頻模式下,功耗會根據降頻倍數成倍降低,從而可以有效在降低該電能計量晶片的功耗。

榮譽表彰

2016年12月7日,《電能計量晶片降低功耗的方法》獲得第十八屆中國專利優秀獎。