微電子技術中利用元件、器件結構特點實現光複印自動對準的技術。

正文

微電子技術中利用元件、器件結構特點實現光複印自動對準的技術。

微電子技術中利用元件、器件結構特點實現光複印自動對準的技術。...... 微電子技術中利用元件、器件結構特點實現光複印自動對準的技術。 目錄 1 正文 ...

電晶體自對準技術,這是製作MOS大規模積體電路的一種重要工藝技術。採用該技術即可減小其中MOSFET的寄生電容,大大提高工作頻率和速度。...

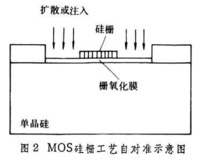

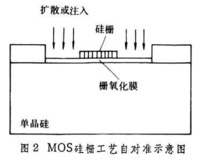

擴散自對準工藝(silicon gate self-aligned technology) 是製作矽柵場效應電晶體的一種新工藝。自對準工藝是先在生長有柵氧化膜的矽單晶片上澱積一層多晶矽,然後在...

自對準雙重成像技術(Self-aligned Double Patterning , SADP)即,一次光刻完成後,相繼使用非光刻工藝步驟(薄膜沉積、刻蝕等)實現對光刻圖形的空間倍頻。最後,使用...

初始對準、動基座自對準和傳遞對準、地磁定位和天文定位算法,捷聯慣導系統誤差及其傳播特性、導航解算、卡爾曼濾波技術等自主定位定向系統的基本原理和設計,並介紹了...

可用同一塊掩模來進行自對準 目錄 1 局部氧化技術: 2 具體步驟 局部氧化技術局部氧化技術: 編輯 局部氧化(local oxidation of silicon,LOCOS)技術:這是Si積體電路...

自對準技術self-alignment technique微電子技術中利用元件、器件結構特點實現光複印自動對準的技術。早期的 MOS積體電路採用的是鋁柵工藝,首先在矽單晶片上熱氧化生長...

6.7.3 自對準金屬柵結構6.7.4 離子注入在SOI結構中的套用6.8 離子注入與熱擴散比較及摻雜新技術本章小結單元習題二第3單元 薄膜製備...

以及矽外延技術; 第5章討論了半導體工藝中的加熱過程;第6章詳細介紹了光學光刻...13.4.2 自對準雙阱 13.4.3 雙阱 13.5 電晶體製造 13.5.1 金屬柵工藝...

BGA (Ball Grid Array)-球狀引腳柵格陣列封裝技術,高密度表面裝配封裝技術。在...2)在回流焊過程中可利用焊球的自對準作用,印焊球的表面張力來達到焊球與焊盤...

在背柵器件部分,主要內容為全自對準背柵MOS電晶體製作技術研究、多晶矽上高質量柵氧化矽生長技術研究以及可用於三維SRAM的高性能背柵器件的研製。在平面雙柵器件部分,...

離子注入的優點是能精確控制雜質的總劑量、深度分布和面均勻性,而且是低溫工藝(可防止原來雜質的再擴散等),同時可實現自對準技術(以減小電容效應)。...

高於該溫度的擴散或熱氧化工序不能在布線之後進行,這對自對準技術是個限制。⑤鋁-矽肖特基勢壘高度不穩定,在雙極型高速電路工藝中,布線金屬往往又是金屬-半導體接觸...

2.6.7 矽柵MOS結構和自對準技術2.6.8 高電子遷移率電晶體(HEMT)習題第3章 積體電路製造工藝3.1 矽平面工藝基本流程……第4章 積體電路設計第5章 微電子...

[19]經張俊,程向紅,王宇. 捷聯羅經的動基座自對準技術. 中國慣性技術學報, 2009, Vol.17(4):408-412.詞條標籤: 行業人物 , 教師, 大學教師 , 人物 V...

這一技術意味著N阱區摻雜濃度可以降低,因而NMOS器件的閾值電壓大為減小,結果使通信用BiCMOS電路可在低電源電壓(3.3V)下工作。4)用矽柵自對準工藝減小交疊電容製作...