基本概念

近來,微電子器件及其

邏輯電路的可靠性和抗輻射性能受到了研究者廣泛的關注 ,這個特徵對於新興的納米級磁性邏輯器件也不例。

磁性邏輯器件(Magnetic Logic Device ,MLD) ,也可稱作磁性量子元胞自動機(Magnetic Quantum Cellular Auotmata ,MQCA),是一種利用納磁體間偶極子場作用進行信息處理和傳遞的新興納電子器件,由Cowburn等首次提出。和傳統CMOS 以及其它新興器件相比,MLD 除了具有極低功耗優點外,其最重要的優勢是具有天然非易失性和抗輻射功能,這些特徵使其在空天電子領域具有廣泛的套用前景。

雖然磁性邏輯器件相比CMOS 而言在實現相同的功能(例如擇多邏輯門)下占用更少的版圖面積,但是隨著片上集成密度的增加,納磁體尺寸會越來越小,而此時能否獲得可靠的電路轉換極為重要。

磁性邏輯器件結構

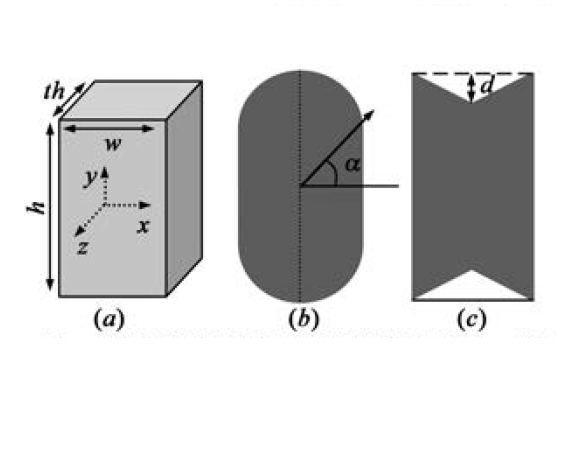

MLD通常由長方體納磁體構成,這是因為拉長的長方形納磁體具有明顯的形狀各向異性,易於實現雙穩態(‘0’和‘1’)。然而,研究表明當MLD 電路中含有多於五個納磁體或一個以上的擇多邏輯門時,磁性邏輯器件極易受雜散磁場的影響而發生自發和無序翻轉。這些雜散磁場或來源於非對稱的納磁體版圖結構,或來源於溫度波動引起的微小熱耦合場。目前常用的增加磁性邏輯器件穩定性的方法是採用二軸各向異性和多重磁晶各向異性納磁體以及慢變旋轉磁場時鐘。改變各向異性是一種很有效的解決方法,但其需要外延生長工藝進行納磁體製備,不利於實現多層磁邏輯結構;而慢變旋轉磁場時鐘則大大降低了電路的工作速度。因而磁性邏輯的可靠轉換迫切需要設計出簡潔和穩定的器件結構。

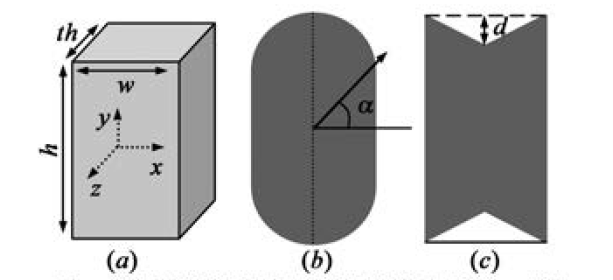

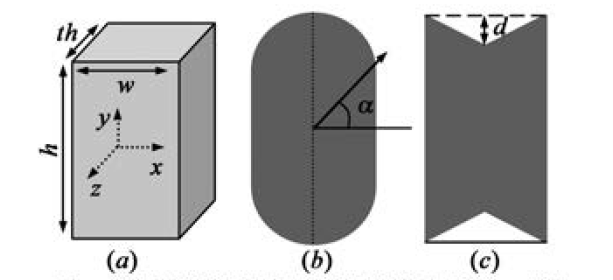

圖1( a)所示為納米磁性邏輯器件,它採用拉長形狀的單疇納磁體構成(單疇是指納磁體內所有磁化是大致相同的,可等效為一個巨大的經典旋轉),納磁體的大小可表示為寬× 高× 厚(w × h × th)。x-y平面上,MLD 的長軸通常被視為易磁化軸,即圖1( a)中的y方向;短軸則為難磁化軸,即圖1( a)中的x 方向;z 軸表示厚度。通常情況下可採用如下邏輯編碼方法,如磁化方向朝上或朝下可分別用於編碼邏輯‘1’或‘0’ ,而沿難磁化軸朝右或朝左的磁化則為空態‘。納磁體之間的偶極子耦合產生了‘0’和‘1’指向交替出現的反鐵磁排序(Antiferromagnetic Ordering ,AFO)和指向相同的鐵磁排序(Ferromagnetic Ordering ,FO) ,這兩種排序的組合可實現有用的磁性邏輯門電路。圖1( b)所示為正常形狀的圓角長方形納磁體(x-y平面圖) ,其中α表示瞬態磁化方向和短軸的夾角。圖1( c)所示為對稱缺失等腰三角形特殊形狀納磁體,其中等腰三角形的底邊和納磁體的寬度相同,d表示等腰三角形的高度。

圖1

MLD 的轉換機制為:沿著器件難磁化軸施加一個微小的磁場將納磁體磁化到空態(這個微小的輔助磁場就是磁性邏輯器件的時鐘),隨後該器件會在鄰接納磁體的偶極子場作用下翻轉到期望的邏輯態。

磁性擇多邏輯電路

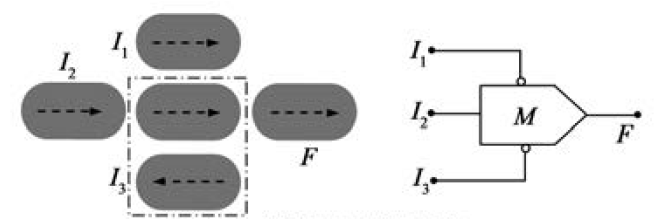

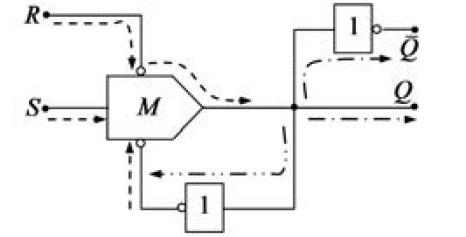

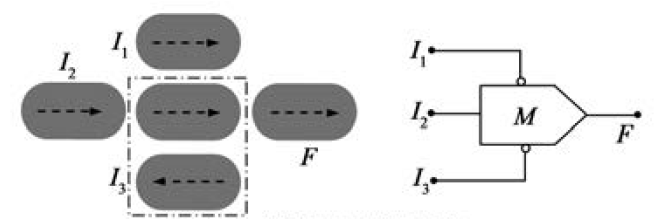

反相器是CMOS 中的基本電路,而MLD 中的信號反相是通過反鐵磁耦合實現的,圖2中虛線方框描述的兩個納磁體即是一個最簡單的磁性邏輯反相器。這裡右向代表邏輯‘1’ ;左向代表邏輯‘0’ ;朝上或朝下為空態。磁性擇多邏輯門電路如圖2所示,它由十字形放置的五個納磁體構成,三輸入共有八種配置組合。

圖2

圖2中,

、

和

為輸入納磁體,F為輸出納磁體;虛線箭頭給出的磁化指向為其中一種穩態配置。注意磁性擇多邏輯門與早期的電性量子元胞自動機擇多邏輯門完全不同,這是因為磁性邏輯器件中存在兩種不同機理的耦合形式。通過OOMMF軟體窮盡模擬8個輸入邏輯組合得出了不同情況下的納磁體磁化指向,進而推導出其邏輯表達式(能夠實現輸出

、

和

變數組中出現次數較多的邏輯態)為:

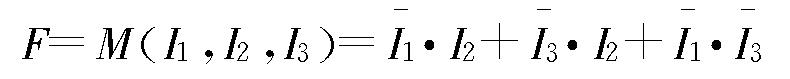

MLD觸發器實現

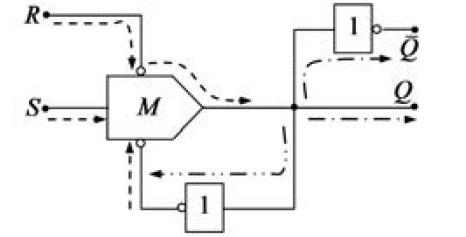

觸發器是具有記憶功能、能存儲數字信息的最常用的一種基本時序單元電路,但目前還未見採用磁性邏輯器件實現時序電路的報導,主要原因也在於大量納磁體和多個邏輯門的整體傳遞行為非常複雜,要實現可靠轉換比較困難。一個簡潔的非鐘控RS觸發器(無CP脈衝控制信號),其電路圖如圖3所示。這個電路用到了兩個反相器和一個擇多邏輯門,其邏輯表達式為:

該觸發器實現的功能是:當兩輸入值R和S相等時,觸發器輸出保持為先前的邏輯態;當R=0、S=1時,其輸出為邏輯‘1’;當R=1、S=0時,其輸出為邏輯‘0’。

圖3

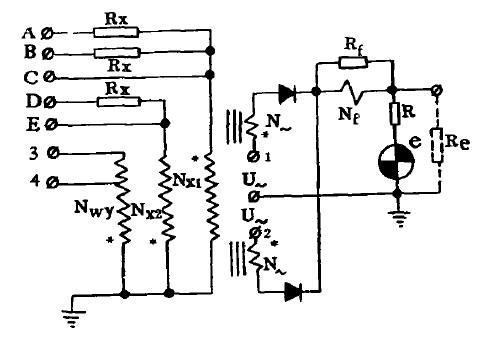

LC1型磁性邏輯元件

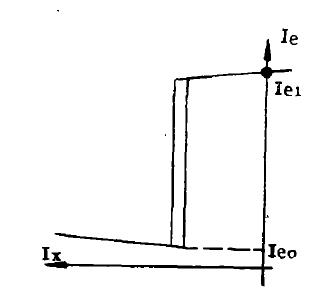

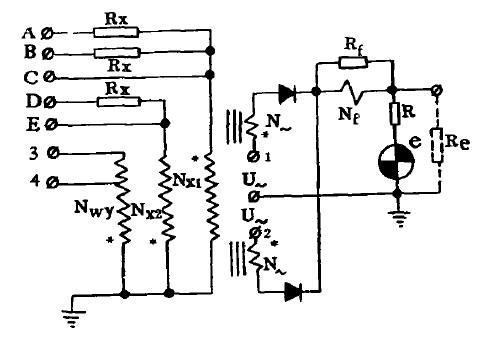

LC1型磁性邏輯元件是利用磁性放大器工作在繼電狀態下——磁繼電器的原理來構成的。其基本線路如圖4,基本特性如圖5。

圖4

圖5

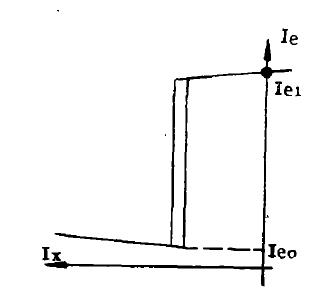

圖5所示的繼電特性類似有接點繼電器的控制特性,有著兩種穩定的工作狀態—元件輸出狀態

(工作在特性的上限)和元件干擾狀態

(工作在特性的下限),相當於繼電器的起動狀態和釋放狀態。

元件的基本線路中共有兩個控制器組

及

以及一個位移繞組,它們的極性已在圖4中標出。只要適當地改變引入位移安匝的大小及部分外部連線即能得到表1所示的五種基本基輯元件和多種複合是輯元件(“和——記憶”複合,“是——否”複合等等),所以本型邏輯元件亦有萬用元件之稱。