在數字電路系統工作過程中,把正在處理的二進制數據或代碼暫時存儲起來的操作叫做暫存,暫存器電路就是實現暫存功能的電路,是數字邏輯電路的基礎模組。

基本介紹

- 中文名:暫存器電路

- 外文名:register circuit

- 拼音:jì cún qì diàn lù

- 定義:實現暫存功能的電路

- 屬性:數字邏輯電路的基礎模組

- 套用學科:計算機

概述

基本暫存器電路

定義

特點

工作原理

在數字電路系統工作過程中,把正在處理的二進制數據或代碼暫時存儲起來的操作叫做暫存,暫存器電路就是實現暫存功能的電路,是數字邏輯電路的基礎模組。

在數字電路系統工作過程中,把正在處理的二進制數據或代碼暫時存儲起來的操作叫做暫存,暫存器電路就是實現暫存功能的電路,是數字邏輯電路的基礎模組。...

暫存器是中央處理器內的組成部分。暫存器是有限存貯容量的高速存貯部件,它們可用來暫存指令、數據和地址。在中央處理器的控制部件中,包含的暫存器有指令暫存器(IR)和...

在數位電路設計中,暫存器傳輸級(英語:register-transfer level, RTL)是一種對同步數位電路的抽象模型,這種模型是根據數位訊號在硬體暫存器、存儲器、組合邏輯裝置和...

暫存器(Registered)記憶體也稱緩衝器(buffered)記憶體(memory),是一種在DRAM模組與系統記憶體控制器之間有暫存器的記憶體模組。...

暫存器(Register),是中央處理器內的其中組成部分,暫存器訪問速度最快,完全能與 CPU 協調工作,但價格卻十分昂貴,因此容量不可能做得很大。暫存器是有限存貯容量的高速...

觸發器暫存器是邊沿敏感的存儲單元,數據存儲的動作有某一信號的上升或者下降沿進行同步的,觸發器的Q輸出端在每一個時鐘沿都會被更新,而所存器只能在使能電平有效...

電路(英文:Electrical circuit)或稱電子迴路,是由電氣設備和元器件,按一定方式聯接起來,為電荷流通提供了路徑的總體,也叫電子線路或稱電氣迴路,簡稱網路或迴路。如...

數字電路根據邏輯功能的不同特點,可以分成兩大類,一類叫組合邏輯電路(簡稱組合電路),另一類叫做時序邏輯電路(簡稱時序電路)。組合邏輯電路在邏輯功能上的特點是任意...

TTL電路是電晶體-電晶體邏輯電路的英文縮寫(Transistor-Transistor-Logic ),TTL電路是數字集成電路的一大門類。它採用雙極型工藝製造,具有高速度低功耗和品種多等特點...

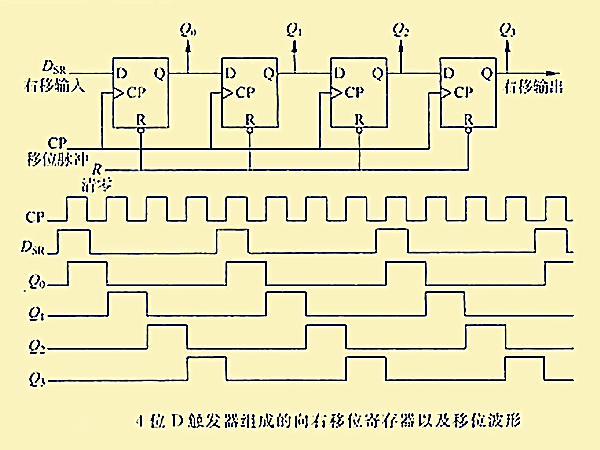

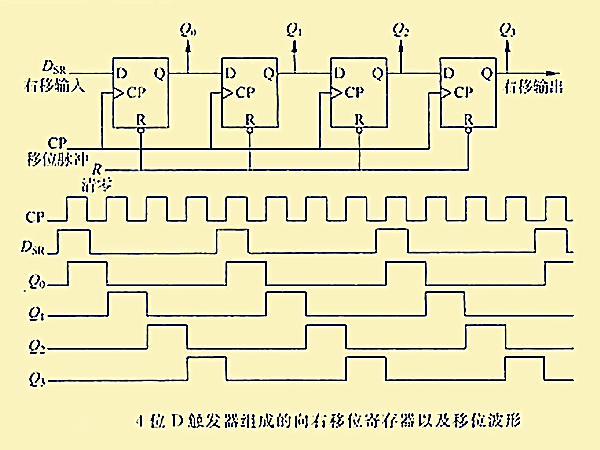

在數字電路中,移位暫存器是一種在若干相同時間脈衝下工作的以觸發器為基礎的器件,數據以並行或串列的方式輸入到該器件中,然後每個時間脈衝依次向左或右移動一個比特...

記憶體資料暫存器(Memory Data Register,MDR),又稱數據暫存器、緩衝暫存器,是計算機控制單元中的暫存器,暫存了將要寫入到計算機主存儲器(例如:RAM)的數據,或由計算機主...

雖然每個數字電路系統可能包含有組合電路,但是在實際套用中絕大多數的系統還包括存儲元件,我們將這樣的系統描述為時序電路。時序電路,是由最基本的邏輯門電路加上反饋...

電源電路是指提供給用電設備電力供應的電源部分的電路設計,使用的電路形式和特點。既有交流電源也有直流電源。...

用來保存當前CPU所訪問的記憶體單元的地址。由於在記憶體和CPU之間存在著操作速度上的差別,所以必須使用地址暫存器來保持地址信息,直到記憶體的讀/寫操作完成為止 。 ...

電路設計,是指按照一定規則,使用特定方法設計出符合使用要求的電路系統。...... 典型數字電路有,振盪器、暫存器、加法器、減法器等。運算不連續性定量電信號。...

接口電路:計算機之間,計算機與外圍設備之間,計算機內部部件之間起連線作用的邏輯電路。接口電路是CPU與外部設備進行信息互動的橋樑。...

電路,是組成電路路徑的各種裝置和電源的總稱。按通過的電流性質可分為直流電路和交流電路。信息電路,用符號傳送的報導組成電路路徑的各種裝置和電源的總稱。...

SCON串列口控制暫存器通常在晶片或設備中為了監視或控制接口狀態,都會引用到接口控制暫存器。SCON 就是51 晶片的串列口控制暫存器。它的定址地址是98H,是一個可以位...

用以實現基本邏輯運算和複合邏輯運算的單元電路稱為門電路。常用的門電路在邏輯功能上有與門、或門、非門、與非門、或非門、與或非門、異或門等幾種。...

暫存器堆(register file)是CPU中多個暫存器組成的陣列,通常由快速的靜態隨機讀寫存儲器(SRAM)實現。這種RAM具有專門的讀連線埠與寫連線埠,可以多路並發訪問不同的暫存器...

數字集成電路是將元器件和連線集成於同一半導體晶片上而製成的數字邏輯電路或系統。根據數字集成電路中包含的門電路或元、器件數量,可將數字集成電路分為小規模集成...

電路:由金屬導線和電氣、電子部件組成的導電迴路,稱為電路。在電路輸入端加上電源使輸入端產生電勢差,電路連通時即可工作。電流的存在可以通過一些儀器測試出來,如...

本書從電路基本原理的介紹開始,對各種類型的電子元器件進行了詳細具體的分類介紹。介紹了各種電路的設計及實用電路;在數字電路中,介紹了暫存器、計數器等各種中規模...

本系統採用DDS集成晶片AD9830,其內部有兩個12位相位暫存器和兩個32位頻率暫存器...基本的恆流源電路主要是由輸入級和輸出級構成,輸入級提供參考電流,輸出級輸出...

暫存器傳輸語言就是既表示了暫存器傳輸操作,又和硬體之間有簡單對應關係的一種方便的設計工具,是描述各模組內部和模組之間連線關係的一種很好的方法。...

《實用電子元器件與電路基礎(第二版)》是電子工業出版社於2009年4月1日出版的圖書。...