時鐘門控(Clock-Gating)一直以來都是降低微處理器功耗的重要手段,主要針對暫存器翻轉帶來的動態功耗。

基本介紹

- 中文名:門控時鐘

- 外文名:Clock-Gating

- 作用:降低微處理器功耗的重要手段

設計

最佳化

時鐘門控(Clock-Gating)一直以來都是降低微處理器功耗的重要手段,主要針對暫存器翻轉帶來的動態功耗。

時鐘門控(Clock-Gating)一直以來都是降低微處理器功耗的重要手段,主要針對暫存器翻轉帶來的動態功耗。設計如何更加有效地設計時鐘門控對於最大限度地降低功耗,同時保證處理器的性能至關重要。多核多執行緒微處理器中,多個...

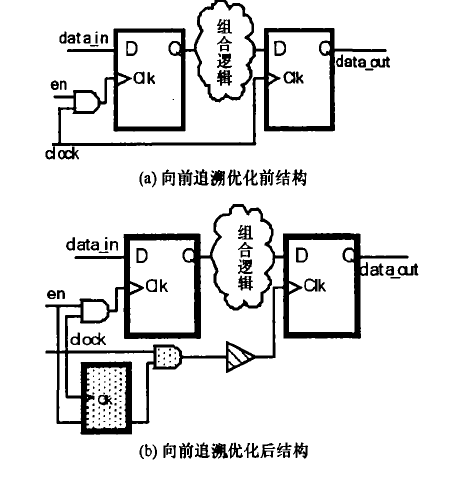

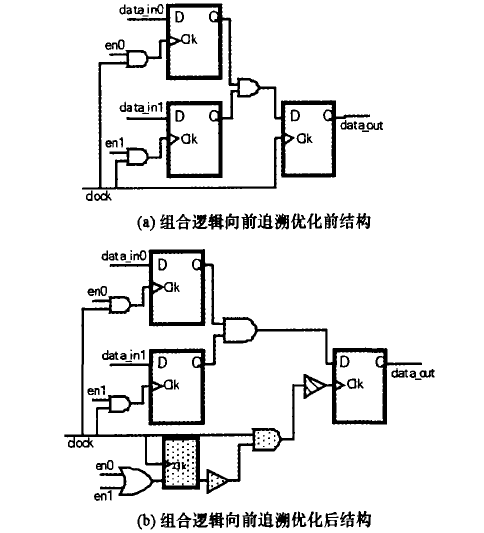

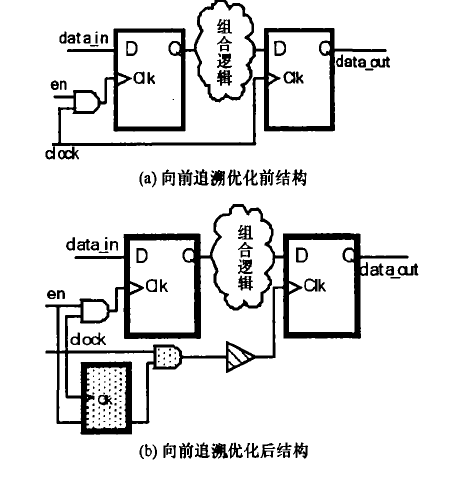

以低功耗為目標,在布局中指導時鐘緩衝器/門控單元的位置規劃。同時,在最佳化中引入工藝參數變化影響因素,增加時鐘網路的抗干擾性設計。本課題旨在探討新的高性能晶片時鐘設計方法,深入研究相應的高可靠性低功耗時鐘最佳化算法,重點在於提高...

門控時鐘控制的暫存器 存儲分區訪問 存儲分區訪問是將一個大的存儲模組分成不同的小的存儲模組,通過解碼器輸出的高位地址來區分不同的存儲模組。工作中,只有被訪問的存儲器才工作,其他幾塊存儲器不工作。多模組RAM的架構如下圖所示。...

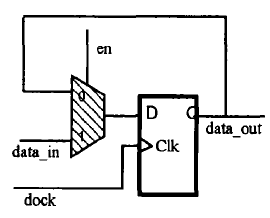

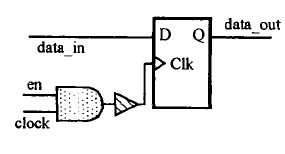

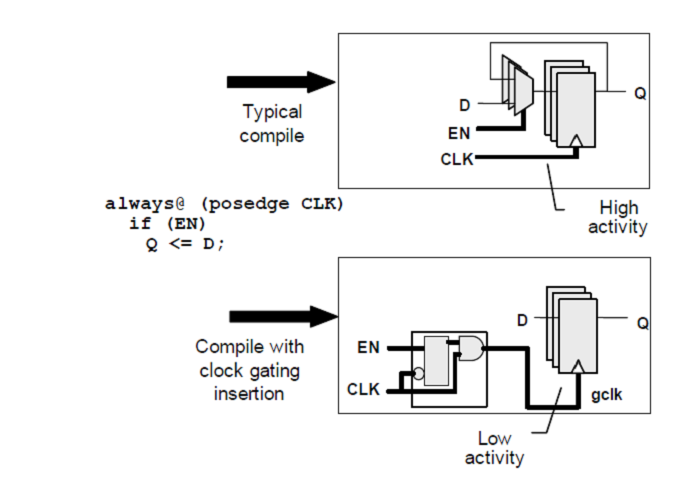

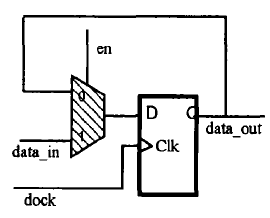

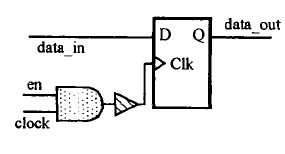

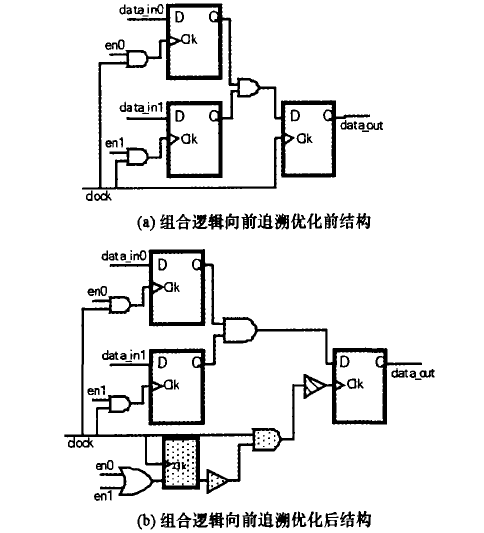

門控時鐘包括門控邏輯模組時鐘和門控暫存器時鐘。門控邏輯模組時鐘對時鐘網路進行劃分,如果在當前的時鐘周期內,系統沒有用到某些邏輯模組,則暫時切斷這些模組的時鐘信號,從而明顯地降低開關功耗。門控暫存器時鐘的原理是當暫存器保持數據...

《電能計量晶片降低功耗的方法》的電能計量晶片設有兩個時鐘域,其中該電能計量晶片的CPU位於時鐘域一,而計量電路位於時鐘域二,時鐘域一選擇使用低頻時鐘與高頻時鐘,並可停止動作維持恆定電平,時鐘域二選擇使用低頻時鐘、降頻時鐘及高頻...

門控時鐘技術 晶片系統中功耗的一大部分來源是時鐘網路所消耗的功耗,動態功耗中近似50%的功耗是時鐘頻率消耗的。為了降低系統功耗,當部分電路模組進入空閒狀態的時候,將該電路的時鐘關閉,這種方法就叫做門控時鐘(Clock Gating), 門控...

時鐘信號也可能由門控,即用一個控制信號使能或關閉電路某一部分的時鐘信號。這種技術經常用於通過有效地關閉數字電路中未使用的部分來節省電力。但同時以複雜的時序分析為代價。單相定時器 現在大部分的同步電路只會用到一個“單相定時器...

74HC165的時鐘輸入是一個“門控與”結構,CP(時鐘脈衝)和CE(時鐘允許)共同產生有效時鐘輸入。只有在CE(時鐘允許)為低時,CP(時鐘脈衝)才有效。應當注意的是,在PL上升沿到來前,CP或者CE必須置高,以防止數據在PL的狀態尚未...

4.1 模組面積和邏輯門數 46 4.2 數據吞吐率和延滯時間 48 4.3 功耗 48 4.4 基本組合運算 50 4.5 延遲時間的最佳化 50 4.6 負數運算 52 4.7 流水線 53 4.8 跨時鐘域電路 55 4.9 時鐘門控 58 第5章 ...

然而,晶片設計趨勢指向事件仿真由於電路中的活動因子減少而獲得相對性能(由於諸如時鐘門控和功率門控之類的技術,這些技術正變得越來越常用於降低功耗)。在這些情況下,由於事件模擬僅模擬必要的事件,因此性能可能不再是循環模擬的劣勢。...

通過數字集成整形電路,將在網運行發電機和待並發電機的電壓信號整形成矩形波,並以此矩形波為門控信號,對時鐘脈衝進行計數。從而將運行發電機與待並發電機的電壓信號間的相位差轉換成時鐘脈衝的計數值(在計算機仿真系統中,相位差計數值...

4.2.2 門控時鐘的約束 4.2.3 分頻電路和多路傳輸電路的時鐘約束 4.3 面積約束 第五章 綜合庫和靜態時序分析 5.1 綜合庫和設計規則 5.1.1 綜合庫 5.1.2 設計規則 5.2 靜態時序分析 5.2.1 時序路徑和分組 5...

4.2.2 門控時鐘的約束 4.2.3 分頻電路和多路傳輸電路的時鐘約束 4.3 面積約束 第五章 綜合庫和靜態時序分析 5.1 綜合庫和設計規則 5.1.1 綜合庫 5.1.2 設計規則 5.2 靜態時序分析 5.2.1 時序路徑和分組 5...