基本介紹

- 中文名:時序電路

- 外文名:Sequential Circuits

- 全稱:時序邏輯電路

- 設計:6步

- 特點:具有記憶功能

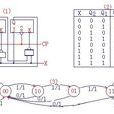

雖然每個數字電路系統可能包含有組合電路,但是在實際套用中絕大多數的系統還包括存儲元件,我們將這樣的系統描述為時序電路。時序電路,是由最基本的邏輯門電路加上反饋...

數字電路根據邏輯功能的不同特點,可以分成兩大類,一類叫組合邏輯電路(簡稱組合電路),另一類叫做時序邏輯電路(簡稱時序電路)。組合邏輯電路在邏輯功能上的特點是任意...

時序電路是計算機及其它電子系統中常用的一種電路。它和組合電路是完全不同的兩種類型電路。時序電路分為兩大類:同步時序邏輯電路和異步時序邏輯電路。在同步時序邏輯...

在各類工業自動控制系統中,有很大一類屬於開關量的自動控制系統,包括繼電接觸控制系統、半導體邏輯控制系統和順序控制系統等。構成這類開關控制系統的基礎是開關電路。...

時序邏輯電路其任一時刻的輸出不僅取決於該時刻的輸入,而且還與過去各時刻的輸入有關。常見的時序邏輯元件有觸發器、計數器、暫存器等。由於時序邏輯電路具有存儲或...

時序邏輯電路其任一時刻的輸出不僅取決於該時刻的輸入,而且還與過去各時刻的輸入有關。常見的時序邏輯電路有觸發器、計數器、暫存器等。時序邏輯電路在邏輯功能上的...

同步時序,即同步時序電路,一種新的時序電路的設計理論與方法,實現了同步、異步電路的設計過程的統一。...

時序產生器是CPU中一個類似"作息時間"的東西,使計算機可以準確、迅速、有條不紊地工作。機器一旦被啟動,即CPU開始取指令並執行指令時,操作控制器就利用定時脈衝的...

時序控制器主要由電源控制電路、電源變換電路、機械式撥碼定時電路、數字式觸發器等六個單元電路組成。...

要使計算機有條不紊地工作,對各種操作信號的產生時間、穩定時間、撤銷時間及相互之間的關係都有嚴格的要求。對操作信號施加時間上的控制,稱為時序控制。只有嚴格的...

數字電路根據邏輯功能的不同特點,可以分成兩大類,一類叫組合邏輯電路(簡稱組合電路),另一類叫做時序邏輯電路(簡稱時序電路)。組合邏輯電路在邏輯功能上的特點是任意...

時序邏輯是指輸出不但和當前輸入的邏輯值有關,而且和在此以前曾經輸入過的邏輯值有關的邏輯系統。異步時序邏輯是電路的工作節奏不一致,不存在單一的主控時鐘,主要...

LCD時序是指對LCD顯示模組進行讀寫時電路的時序要求和狀態。...... LCD時序是指對LCD顯示模組進行讀寫時電路的時序要求和狀態。中文名 LCD時序 接口信號 工作主...

數字電路根據邏輯功能的不同特點,可以分成兩大類,一類叫組合邏輯電路(簡稱組合電路),另一類叫做時序邏輯電路(簡稱時序電路)。組合邏輯電路在邏輯功能上的特點是任意...

邏輯電路是一種離散信號的傳遞和處理,以二進制為原理、實現數位訊號邏輯運算和操作的電路。分組合邏輯電路和時序邏輯電路。前者由最基本的“與門”電路、“或門”...

計數式時序脈衝發生器主要由計數電路和解碼電路組成。主脈衝(計數脈衝)送入計數電路,解碼電路譯出相應的計數狀態,即可得到需要的輸出[1] 。...

而時序電路是一種輸出不僅與當前的輸入有關,而且與其輸出狀態的原始狀態有關,其相當於在組合邏輯的輸入端加上了一個反饋輸入,在其電路中有一個存儲電路,其可以將...

在數字電路系統工作過程中,把正在處理的二進制數據或代碼暫時存儲起來的操作叫做暫存,暫存器電路就是實現暫存功能的電路,是數字邏輯電路的基礎模組。...

驅動時序 driving schedule 指集成電路設計中,以已經完成其版圖而可以調用的單元或宏單元為基礎,對整個晶片的版圖拓... ...

時鐘信號是計算機科學以及相關領域用語,時鐘信號通常被用於同步電路當中,扮演計時器的角色,保證相關的電子組件得以同步運作。...