基本概念

在數字控制設備中,經常要用到時序

脈衝發生器(又稱節拍脈衝發生器或脈衝分配器)。它有許多條輸出線,在這些輸出線上能依次出現節拍控制電位(或時序脈衝),用以協調機器各部分的動作。計數式時序脈衝發生器主要由計數電路和解碼電路組成。主脈衝(計數脈衝)送入計數電路,解碼電路譯出相應的計數狀態,即可得到需要的輸出。

採用觸發器、移位暫存器、計數器與解碼器、脈衝分配器、接口電路與解碼器等均能實現時序脈衝發生器,並且具有廣泛的實用性及通用性。

採用觸發器組成時序脈衝發生器

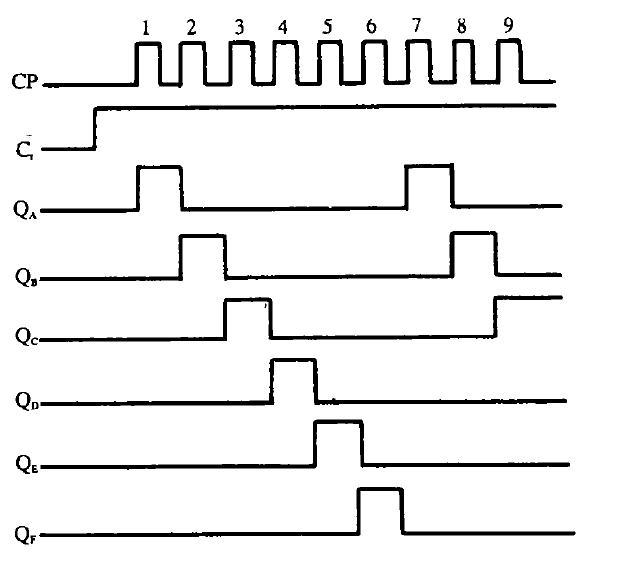

利用D型觸發器可組成時序脈衝發生器,電路如圖1所示。將多級D型觸發器逐級串接,將它們的

清除端接至由R、C組成的上電復位電路,並將它們的輸出端

~

(最末級輸出端

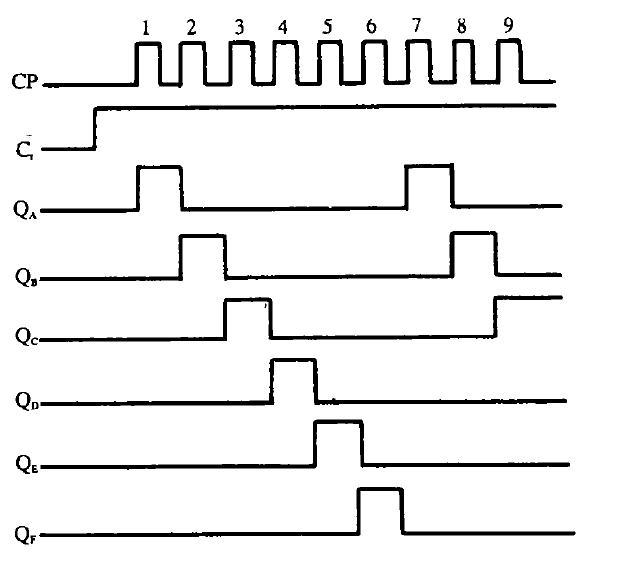

除外)經或非門後再反饋至首級觸發器的D輸入端,便可依次在每個觸發器的Q輸出端獲得時序脈衝,其波形圖如圖2所示。

這種時序脈衝發生器在開機接通電源後能自行啟動,並保持每個時序脈衝的時間為一個時鐘脈衝的周期,因而時序脈衝與脈衝之間不會出現“重疊”或錯亂現象。電路採用同步觸發方式,從理論上講,所有觸發器都應該是同時翻轉的。但是,實際上各個觸發器的性能不可能完全一樣,而且每個觸發器的負載大小和布線情況也不相同。因此,這些觸發器不可能絕對同時翻轉,也就不可能徹底消除競爭冒險現象。圖2中選用的是74LS174六D觸發器和74LS2fi。五輸入或非門組成的時序脈衝發生器。依同樣道理,可選用74LS74,74LS175,74LS273等其它型

號D型觸發器和74LSa2,74LS27,7425等或非門及相應擴展電路組成時序脈衝發生器。

圖1

圖2

採用移位暫存器組成時序脈衝發生器

利用移位暫存器組成時序脈衝發生器的電路如圖3所示,由八位移位暫存器74LS164附加一個組合七輸入端或非門電路組成8時序脈衝發生器。接通電源C,清除端獲負脈衝,暫存器清零,輸出端

~

全為“0”,數據輸入端

、

則為“1”,待時鐘脈衝CP正跳沿來到時,

輸出第一個正時序脈衝並使

、

為0,隨著時鐘脈衝CP的輸入,

移位暫存器執行右移操作,同步地將這個正脈衝移位,直到

輸出正脈衝

、

又為“1",在時鐘脈衝CP作用下

又輸出正脈衝…,如此周而復始不斷循環,完成時序脈衝輸出。如果時鐘脈衝是一個基準時間,則各輸出可作為分時定時信號。

圖3

採用計數器與解碼器組成時序脈衝發生器

利用計數器與解碼器組成的時序脈衝發生器原理電路如圖4所示。作為時間基準的時鐘脈衝加在計數器輸入端,然後經過解碼器將計數器的狀態譯成輸出線上的順序脈衝。圖4中計數器是異步式的,在時鐘脈衝作用,各個觸發器不是同時翻轉,而是有先有後。在每次狀態變化時,可能有兩個或兩個以上的觸發器翻轉,因此將出現競爭冒險現象,可能在解碼器輸出線Y0~Y1上產生干擾脈衝。例如當計數器狀態由001變為010時,若觸發器A先翻轉為0,B後翻轉為1,那么在A已翻轉,而B尚未翻轉時,將出現短暫的000狀態,因而會在Y0輸出線上產生一個窄的過渡干擾脈衝。同理,Y2輸出線在由011變100時,Y4輸出線在由101變110時等等,均可能有過渡干擾脈衝產生。要消除過渡干擾脈衝,可採用

環形計數器,

格雷碼計數器或詹森計數器,而最簡單的辦法是用計數輸入脈衝去封解碼器。