理論知識

計算機內部的主機板上混合了各種

高頻電路、數字電路和

模擬電路,它們工作時會產生大量高頻電磁波互相干擾,這就是EMI。EMI還會通過主機板布線或外接線纜向外發射,造成

電磁輻射污染,影響其他的電子設備正常工作。

PC板卡上的晶片在工作過程中既是一個電磁干擾對象,也是一個電磁干擾源。總的來說,我們可以把這些電磁干擾分成兩類:串模干擾(差模干擾)與共模干擾(接地干擾)。以主機板上的兩條PCB走線(連線主機板各元件的

導線)為例,所謂串模干擾,指的是兩條走線之間的干擾;而共模干擾則是兩條走線和PCB地線之間的電位差引起的干擾。串模干擾電流作用於兩條信號線間,其傳導方向與波形和信號電流一致;

共模干擾電流作用在信號線路和地線之間,干擾電流在兩條信號線上各流過二分之一且同向,並以地線為公共迴路。

如果板卡產生的共模電流不經過衰減過濾(尤其是像USB和IEEE

1394接口這種高速接口走線上的共模電流),那么共模干擾電流就很容易通過接口數據線產生電磁輻射——線上纜中因共模電流而產生的共模輻射。美國FCC、國際無線電干擾特別委員會的CISPR22以及我國的GB9254等標準規範等都對

信息技術設備通信連線埠的共模傳導干擾和輻射發射有相關的限制要求。為了消除信號線上輸入的干擾信號及感應的各種干擾,我們必須合理安排濾波電路來過濾共模和串模的干擾,共模電感就是濾波電路中的一個組成部分。

共模電感實質上是一個雙向

濾波器:一方面要濾除信號線上共模電磁干擾,另一方面又要抑制本身不向外發出電磁干擾,避免影響同一電磁環境下其他電子設備的正常工作。

工作原理

為什麼共模電感能防EMI?要弄清楚這點,我們需要從共模電感的結構開始分析。

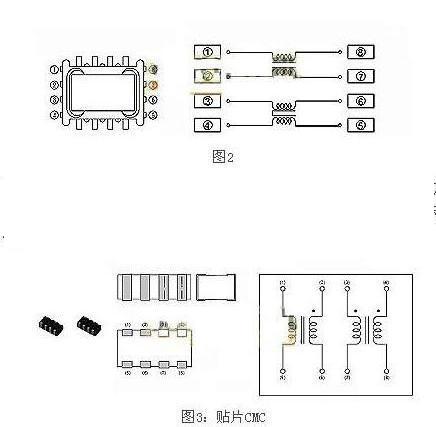

共模電感的濾波電路,La和Lb就是共模

電感線圈。這兩個線圈繞在同一鐵芯上,匝數和相位都相同(繞制反向)。這樣,當電路中的正常電流流經共模電感時,電流在同相位繞制的電感線圈中產生反向的磁場而相互抵消,此時正常信號電流主要受線圈電阻的影響(和少量因漏感造成的阻尼);當有共模電流流經線圈時,由於共模電流的同向性,會線上圈內產生同向的磁場而增大線圈的

感抗,使線圈表現為高阻抗,產生較強的阻尼效果,以此衰減共模電流,達到濾波的目的。

圖2 圖3

圖2 圖3事實上,將這個濾波電路一端接干擾源,另一端接被干擾設備,則La和C1,Lb和C2就構成兩組

低通濾波器,可以使線路上的共模EMI信號被控制在很低的電平上。該電路既可以抑制外部的EMI信號傳入,又可以衰減線路自身工作時產生的EMI信號,能有效地降低EMI干擾強度。

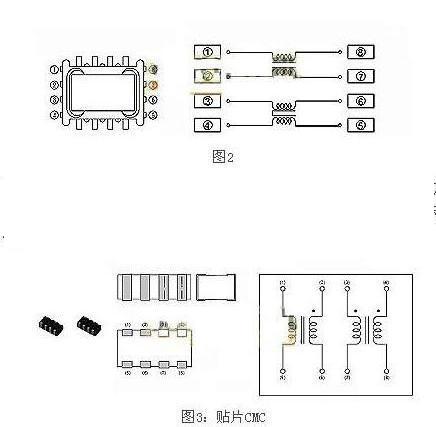

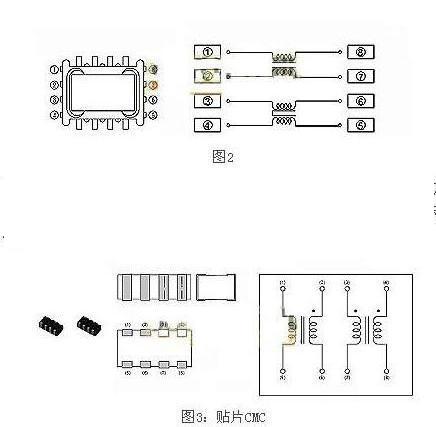

國內生產的一種小型共模電感,採用高頻之雜訊抑制對策,共模扼流線圈結構,訊號不衰減,體積小、使用方便,具有平衡度佳、使用方便、高品質等優點。廣泛使用在雙平衡調音裝置、多頻變壓器、阻抗變壓器、平衡及不平衡轉換變壓器...等。

還有一種共模濾波器電感/

EMI濾波器電感採用鐵氧體磁心,雙線並繞,雜訊抑制對策佳,高共模噪音抑制和低

差模噪聲信號抑制,低差模噪聲信號抑制干擾源,在高速信號中難以變形,體積小、具有平衡度佳、使用方便、高品質等優點。廣泛使用在抑制電子設備EMI噪音、個人電腦及外圍設備的 USB線路、DVC、STB的IEEE1394線路、液晶顯示面板、低壓微分信號...等。

漏感差模

對理想的電感模型而言,當線圈繞完後,所有磁通都集中線上圈的中心內。但通常情況下環形線圈不會繞滿一周,或繞制不緊密,這樣會引起磁通的泄漏。共模電感有兩個繞組,其間有相當大的間隙,這樣就會產生磁通泄漏,並形成

差模電感。因此,共模電感一般也具有一定的差模干擾衰減能力。

在濾波器的設計中,我們也可以利用漏感。如在普通的濾波器中,僅安裝一個共模電感,利用共模電感的漏感產生適量的差模電感,起到對差模電流的抑制作用。有時,還要人為增加

共模扼流圈的漏電感,提高差模電感量,以達到更好的濾波效果。

共模電感

共模電感材料優劣

磁環類型的鐵芯優點:

高初始導磁率(這個是共模電感的基本要求)、高飽和磁感應強度、溫度較之鐵氧體穩定(可以理解為溫升小),頻率特性比較靈活,因為導磁率高,很小就可以做出很大的感量,適應頻率比較寬;

整體優勢:

因為初始導磁率是鐵氧體的5-20倍,對傳導干擾的抑制作用遠大於鐵氧體;

納米晶的高飽和磁感應強度比鐵氧體的好,所以在大電流下不易飽和;

溫升較之UF系列的要低,某人實際測試:室溫下要低將近10度(個人測試值僅作參考);

結構上的靈活令其適應性好,從加工工藝上進行改變,即可適應不同需求(見過節能燈上用的磁環電感,使用相當靈活);

分布電容會更小,因為繞線的面積更寬,體積也相對較小;

環行所用匝數少一點,分布參數小一點,效率占優。

整體劣勢:

磁環孔徑小,機器難以穿線,需要人工去繞,費時費力,加工成本高,效率低。而在成本壓力日益增加的同時,這一點已尤為重要了。

耐壓方面較之UF優勢不大:因為可以看到很多磁環共模中間使用扎線帶隔開的,這樣不是很可靠,有的中間拉開一定距離,線用點膠固定,時間長了,可靠性怎么樣呢?如果電感量要求比較大,線會擠在一起,安全性上有一點疑惑。

安裝不便,故障率較高。

套用:

因為成本的因素,磁環大多用在大功率的電源上,某人形容:“小功率的用磁環太高檔了”,是有道理的。

當然因為體積小,對體積有要求的小功率電源,採用磁環的也是很OK的選擇。

綜合性能比起來,優於UF系的。如果成本壓力不大的項目,可以考慮用磁環的。某實際測試傳導,用磁環的餘量要低更多。而且感量還比UF的小。

再說說UF/UU系列的共模

材料:基本上為鐵氧體,當然這鐵氧體也有區別的,一般有MXO-錳鋅類和NXO-鎳鋅類。鎳鋅類的主要優點是:初始磁導率低(小於1000u),但是可以工作在比較高的頻率(大於100MHZ)下,保持磁導率不變。很強很偉大。

NXO比MXO電阻率高。利用鐵氧體對高頻雜波的類似阻尼的作用將高頻雜波以熱能的方式釋放出來,這就解釋了共模電感的溫度問題。

整體優勢:

最重要的一點:成本低(某人用的這個是0.9元人民幣),可以用機器繞、高效,常用UU9.8或UU10.5;

有骨架,繞制工藝應該會更好控制,可以做更高的電感量;

耐壓及可靠性要好?針對磁環共模的;

好外掛程式,好安裝。四個腳,孔位對了就沒一點問題;基本用在小電流的電源上,因為線徑不可以用很粗的,故電流不能太大;

整體劣勢:

空間因素:封裝位置大,maybe是因為比較強壯,不像磁環那么小巧玲瓏;

發熱比較嚴重,也是根據我實測的:90V輸入滿載室溫下,可以到快90度;

套用:

一般用在成本控制比較嚴格的、抑或小功率的場合。

設計因素

在一些主機板上,我們能看到共模電感,但是在大多數主機板上,我們都會發現省略了該元件,甚至有的連位置也沒有預留。這樣的主機板,合格嗎?

不可否認,共模電感對主機板高速接口的共模干擾有很好的抑制作用,能有效避免EMI通過線纜形成電磁輻射影響其餘外設的正常工作和我們的身體健康。但同時也需要指出,板卡的防EMI設計是一個相當龐大和系統化的工程,採用共模電感的設計只是其中的一個小部分。高速接口處有共模電感設計的板卡,不見得整體防EMI設計就優秀。所以,從共模濾波電路我們只能看到板卡設計的一個方面,這一點容易被大家忽略,犯下見木不見林的錯誤。

只有了解了板卡整體的防EMI設計,我們才可以評價板卡的優劣。那么,優秀的板卡設計在防EMI性能上一般都會做哪些工作呢?

1.主機板Layout(布線)設計

對優秀的主機板布線設計而言,時鐘走線大多會採用禁止措施或者靠近地線以降低EMI。對多層PCB設計,在相鄰的PCB走線層會採用開環原則,導線從一層到另一層,在設計上就會避免導線形成環狀。如果走線構成閉環,就起到了天線的作用,會增強EMI

輻射強度。

信號線的不等長同樣會造成兩條線路阻抗不平衡而形成共模干擾,因此,在板卡設計中都會將信號線以蛇形線方式處理使其阻抗儘可能的一致,減弱共模干擾。同時,蛇形線在布線時也會最大限度地減小彎曲的擺幅,以減小環形區域的面積,從而降低輻射強度。

在高速PCB設計中,走線的長度一般都不會是

時鐘信號波長1/4的整數倍,否則會產生

諧振,產生嚴重的EMI輻射。同時走線要保證回流路徑最小而且通暢。對去耦電容的設計來說,其設定要靠近電源管腳,並且電容的電源走線和地線所包圍的面積要儘可能地小,這樣才能減小電源的紋波和

噪聲,降低EMI輻射。

當然,上述只是PCB防EMI設計中的一小部分原則。主機板的Layout設計是一門非常複雜而精深的學問,甚至很多DIYer都有這樣的共識:Layout設計得優秀與否,對主機板的整體性能有著極為重大的影響。

2.主機板布線的劃斷

如果想將主機板電路間的電磁干擾完全隔離,這是絕對不可能的,因為我們沒有辦法將電磁干擾一個個地“包”起來,因此要採用其他辦法來降低干擾的程度。主機板PCB中的金屬導線是傳遞干擾電流的罪魁禍首,它像天線一樣傳遞和發射著電磁干擾信號,因此在合適的地方“截斷”這些“天線”是有用的防EMI的方法。“天線”斷了,再以一圈絕緣體將其包圍,它對外界的干擾自然就會大大減小。如果在斷開處使用濾波電容還可以更進一步降低電磁輻射泄露。這種設計能明顯地增加高頻工作時的穩定性和防止EMI輻射的產生,許多大的主機板廠商在設計上都使用了該方法。

3.主機板接口的設計

不知大家是否注意到,主機板都會附送一塊開口的薄鐵擋片,其實這也是用來防EMI的。雖然機箱EMI禁止性能都不錯,但電磁波還是會從機箱表面的開孔處泄漏出來,如

PS/2接口、USB接口以及並、串口等的開口處。孔的大小決定了電磁干擾的泄露程度。開口的孔徑越小,電磁干擾輻射的削弱程度越大。對方形孔而言,L就是其對角線長度。

使用了擋片之後,擋片上翹起的金屬觸片會和主機板上的輸入輸出部分很好地通過機箱接地,不但衰減了EMI,而且減小了方孔的尺寸,進一步縮小L值,從而可以更有效地禁止電磁干擾輻射。

上述三點只是主機板設計中除電路設計之外的幾個主要防EMI設計,由此可見,主機板的防EMI設計是一個整體的概念,如果整體的設計不合格,就會帶來較大的電磁輻射,而這些也不是一個小小的共模電感所能彌補的。

共模電感

共模電感必要因素

共模電感缺失=防EMI性能低下?這樣的說法顯然是頗為片面的。

誠然,由於國家的EMI相關規範並不健全,部分廠商為了省料就鑽了這個空子,在整體防EMI性能上都大肆省料壓縮成本(其中就包括共模電感的省略),這樣做的直接後果就是主機板防EMI性能極其低下;但是對於那些整體設計優秀,用料不縮水的主機板,即使沒有共模電感,其整體防EMI性能仍能達到相關要求,這樣的產品仍然是合格的。因此,單純就是否有共模電感這一點來判斷主機板的優劣並不恰當.

測量診斷

1.概述

電源濾波器的設計通常可從共模和差模兩方面來考慮。共模濾波器最重要的部分就是共模

扼流圈,與差模扼流圈相比,共模扼流圈的一個顯著優點在於它的電感值極高,而且體積又小,設計共模扼流圈時要考慮的一個重要問題是它的漏感,也就是差模電感。通常,計算漏感的辦法是假定它為共模電感的1%,實際上漏感為共模電感的 0.5% ~ 4%之間。在設計最優性能的扼流圈時,這個誤差的影響可能是不容忽視的。

2.漏感的重要性

漏感是如何形成的呢?緊密繞制,且繞滿一周的環形線圈,即使沒有磁芯,其所有磁通都集中線上圈“芯”內。但是,如果環形線圈沒有繞滿一周,或者繞制不緊密,那么磁通就會從芯中泄漏出來。這種效應與線匝間的相對距離和螺旋管芯體的磁導率成正比。共模扼流圈有兩個繞組,這兩個繞組被設計成使它們所流過的電流沿線圈芯傳導時方向相反,從而使磁場為0。如果為了安全起見,芯體上的線圈不是雙線繞制,這樣兩個繞組之間就有相當大的間隙,自然就引起磁通“泄漏”,這即是說,磁場在所關心的各個點上並非真正為0。共模扼流圈的漏感是差模電感。事實上,與差模有關的磁通必須在某點上離開芯體,換句話說,磁通在芯體外部形成閉合迴路,而不僅僅只局限在環形芯體內。

如果芯體具有差模電感,那么,差模電流就會使芯體內的磁通發生偏離零點,如果偏離太大,芯體便會發生磁飽和現象,使共模電感基本與無磁芯的電感一樣。

3.共模扼流圈綜述

濾波器設計時,假定共模與差模這兩部分是彼此獨立的。然而,這兩部分並非真正獨立,因為共模扼流圈可以提供相當大的差模電感。這部分差模電感可由分立的差模電感來模擬。

為了利用差模電感,在濾波器的設計過程中,共模與差模不應同時進行,而應該按照一定的順序來做。首先,應該測量

共模噪聲並將其濾除掉。採用差模抑制網路(Differential Mode Rejection Network),可以將差模成分消除,因此就可以直接測量共模噪聲了。如果設計的共模濾波器要同時使差模噪聲不超過允許範圍,那么就應測量共模與差模的混合噪聲。因為已知共模成分在

噪聲容限以下,因此超標的僅是差模成分,可用共模濾波器的差模漏感來衰減。對於低功率

電源系統,共模扼流圈的差模電感足以解決差模輻射問題,因為差模輻射的源阻抗較小,因此只有極少量的電感是有效的。

儘管少量的差模電感非常有用,但太大的差模電感可以使扼流圈發生磁飽和。

4.用LISN原理測量共模扼流圈飽和特性的方法

測量共模線圈磁芯(整體或部分)的飽和特性通常是很困難的。通過簡單的試驗可以看出共模濾波器的衰減在多大程度上受由60Hz編置電流引起的電感減小量的影響。進行此項測試需要一台示波器和一個差模抑制網路(DMRN)。首先,用示波器來監測線電壓。按如下方法從示波器的A通道輸入信號,將示波器的時間基準置為2ms/div,然後將觸發信號加在A通道上,在

交流電壓達到峰值時會有線電流產生,此時濾波器效能的降級是意料中的事情。差模抑制網路(DMRN)的輸入端連線到LISN,輸出端用50的阻抗進行匹配且與示波器的B通道相連。當共模扼流圈工作線上性區時,在輸入電流波動期間,B通道監測到的發射增加值不超過6—10dB。線上電壓峰值期間,橋式整流器正嚮導通且傳送充電電流。

如果共模扼流圈達到飽和,那么在輸入浪涌增加時,發射將會增加。如果共模扼流圈達到強飽和,發射強度與不加濾波器時的情況是一樣的,也就是說很容易達到40dB以上。

這些實驗數據可用其他方法來解釋。發射最小值(

線電流為0的時候)是濾波器無

偏置電流時表現出來的效果。峰值發射與最小發射的比率,即降級因子,用來衡量線電流偏移量對濾波器實際效果的影響。降級因子較大表明共模扼流圈磁芯完全沒有得到恰當的使用,較好的濾波器的“固有降級因子”差不多在2—4之間。它是由兩種現象產生的:第一,60Hz充電電流引起的電感減小(如上所述);第二,橋式整流器的正向及反嚮導通。共模發射的

等效電路由一個阻抗約為200pF的電壓源、二極體阻抗和LISN的共模阻抗組成。當橋式整流器正向偏置時,在源阻抗、25和LISN共模阻抗之間會產生分壓現象。當橋整流器反向偏置時,在源阻抗、整流橋反偏電容、LISN之間產生分壓現象。當二極體整流橋反向偏置電容較小時,對共模濾除有一定效果。當整流橋正向偏置時則對共模濾除沒有影響。

由於產生了分壓,固有降級因子的預期值為2左右。實際值的變化相當大,主要取決於源阻抗和二極體整流橋反向偏置電容的實際大小。在Flugan發明的一個電路中,正是套用這個原理來減小鎮流器的傳導發射的。

5.用電流原理測量共模扼流圈飽和特性的方法

如果測試人員相當謹慎,那么就可以採取類似MIL-STD-461中的測試裝置來檢測共模扼流圈的飽和特性。這個原理的套用如下:測試時採用兩隻

電流探頭,低頻探頭監測線電流,高頻探頭僅測量共模發射電流。線電流監視器作為觸發源。不過,使用電流探頭的一個隱患是差模電流衰減是管芯內繞組導線對稱性的函式。如果精心合理安排繞線布局的話,30dB左右的差模電流衰減是能夠得到的。即使達到這個衰減值,測得的差模分量也可能超過預期的共模分量值。可用如下兩項技術來解決這一問題:第一,將一隻6kHz

轉折頻率的高階高通濾波器與示波器串聯(注意套用50的終端阻抗進行匹配)。第二,在每隻10μF的電容與電源匯流排之間接入一根導線。為了測量共模輻射,電流探頭應夾在這些載有極小線電流的導線近旁。

6.共模扼流圈記憶體在的差模與共模磁通

為了快速且淺顯地介紹共模扼流圈的作用,可考慮採用以下論述:“共模扼流圈管芯兩側的磁場相互抵消,因此不存在磁通使管芯飽和。”儘管這種論述對共模扼流圈作用的直覺敘述具體化了,但實質上並非如此。

7.漏感綜述

共模扼流圈能發揮一定的作用是由於μcm比μdm大好幾個數量級的緣故,因為共模電流通常很小,可以通過使L/D保持在較低值來獲得更小的μdm。

為了得到共模電感,同時又要使差模電感最小,最好是採用橫截面積較大的磁芯繞製成多匝線圈。採用較大的螺旋管磁芯,也並非一定要這樣的磁芯,可在共模扼流圈內併入有效的差模電感。因為差模磁通是遠離磁芯(環形結構)的,因此可能會產生極強的輻射。尤其是濾波器安裝在PCB板上的情況下,這種輻射可以耦合到電源線,使傳導發射增強。當

磁性材料被帶到場內時(例如,環形磁芯放置在鐵殼裡),差模磁導率就可能會顯著地增加,從而由於差模電流而導致磁芯的飽和。

8.無輻射共模扼流圈結構

為了實現有效的濾波器設計,磁通離開磁芯引起的輻射問題必須予以解決。其辦法有是將差模磁通限制在磁性結構物體中(壺形鐵芯),或者是為差模磁通(E形鐵芯)提供一條高磁導率的路徑。

9.壺形鐵芯結構

如果共模扼流圈採用壺形鐵芯結構,那么就需兩個繞軸。壺形鐵芯窗格里的兩組線圈及其產生的磁通路徑。同時也表明了同一結構條件下的差模磁通路徑。

10.E形鐵芯結構

另外還有一種共模扼流圈,它比環形磁芯線圈更易繞制,但比壺形鐵芯線圈的輻射更厲害,E形鐵芯線圈共模磁通將外部引線上的兩組線圈都聯繫在一起了。為了獲得較高的磁導率,在外部引線上應沒有空氣隙。另一方面,差模磁通將外部引線和中心引線聯繫起來。差模路徑中的磁導率可以通過使中心引線彼此隔開來取得,中心引線是產生輻射的主要區域。

要求

(1)繞制線上圈磁芯上的導線要相互絕緣,以保證在瞬時過電壓作用下線圈的匝間不發生擊穿短路;

(3)線圈中的磁芯應與線圈絕緣,以防止在瞬時過電壓作用下兩者之間發生擊穿;

(4)線圈應儘可能繞制單層,這樣做可減小線圈的寄生電容,增強線圈對瞬時過電壓的承受能力。

通常情況下,同時注意選擇所需濾波的頻段,共模阻抗越大越好,因此在選擇共模電感時需要看器件資料,主要根據阻抗頻率曲線選擇。另外選擇時注意考慮差模阻抗對信號的影響,主要關注差模阻抗,特別注意高速連線埠。

圖2 圖3

圖2 圖3 共模電感

共模電感 共模電感

共模電感

圖2 圖3

圖2 圖3 共模電感

共模電感 共模電感

共模電感