基本概述

噪聲容限(英語:Noise Margin)是指在前一極輸出為最壞的情況下,為保證後一極正常工作,所允許的最大噪聲幅度。在

數字電路中,一般常以“1”態下(上)限噪聲容限和“0”態上(下)限噪聲容限中的最小值來表示電路(或元件)的噪聲容限。噪聲容限越大說明容許的噪聲越大,電路的抗干擾性越好。

高電平噪聲容限=最小輸出高電平電壓-最小輸入高電平電壓

低電平噪聲容限=最大輸入低電平電壓-最大輸出低電平電壓

噪聲容限=min{高電平噪聲容限,低電平噪聲容限}

舉例

一條數字電路中的電壓也許被設計在0.0和1.2v之間變化,任何在0.5v以下的電壓被認為是邏輯‘0’,而任何在0.7v之上的電壓被認為是邏輯1。 然後0的噪聲容限是電壓值在0.5v以下的信號,並且‘1’的噪聲容限是電壓值在0.7v以上的信號。通俗點講就是,整個電路所容許的噪聲極限。

TTL 電路額定高電平和低電平分別是2.4v和0.4v,最小可識別電平(即臨界可識別電平)是2v和0.8v。即系統本身高電平識別是2.4v,但若一個信號受噪聲疊加後呈現是2v的電壓,此時也可識別為高電平;低電平額定識別是0.4v,若一個信號受噪聲疊加後呈現0.8v的電壓時,也可以識別出是低電平。TTL的高低電平的噪聲容限都是0.4v,這說明疊加在信號電平上的容許的噪聲擺幅/抖動在小於0.4v時,是對邏輯的正確識別沒有影響的,噪聲容限就是容許的疊加在信號電平上的噪聲幅值裕度,在噪聲容限之內的噪聲信號是可以容許的,不影響正確識別。噪聲容限是 0.4v,就是說可以容許信號電平上有疊加上小於0.4v裕度的噪聲。在這種情況下噪聲容限沒有被測量作為絕對電壓,沒有比率。 CMOS晶片的噪聲容限比TTL通常大,因為VOH是離電源電壓較近,並且最小值是離零較近。

在通信系統工程學,噪聲容限是信號超出極小的可接受的數額的比率。它在分貝耳通常被測量。

靜態噪聲容限

靜態噪聲容限SNM(Static Noise Margin)是指存儲單元所能承受的最大直流噪聲信號的幅值。若超過這個值,存儲結點的狀態會發生錯誤翻轉 [4]。它是衡量存儲單元抗干擾能力的一個重要參數。

NPS-HMI模件母板信號噪聲容限分析

概述

保護裝置母板傳輸的數位訊號在工作時會受到各種干擾和噪聲的影響。只有使這些並非所需要的干擾和噪聲信號小於數字系統所能承受的容限,才能保證系統的正常工作。當干擾大於數字系統所能承受的容限時,則危害系統的正常工作。與模擬電路的干擾只影響其量值和線性不同,數字系統受干擾後會產生誤動作,在運行時會產生嚴重的後果。隨著現代數字電路工作頻率越來越高,工作電壓越來越低,使得數字電路動作能量小、翻轉速度快、信號電平低,所以外部干擾容易影響其正常工作,這就需要更加重視對系統數字電路干擾與噪聲產生的原因及其危害性的分析與研究,提出更完善的防治干擾與噪聲的措施,保證系統達到應有的性能和可靠的工作。

3種描述數字電路抗噪聲能力的噪聲容限

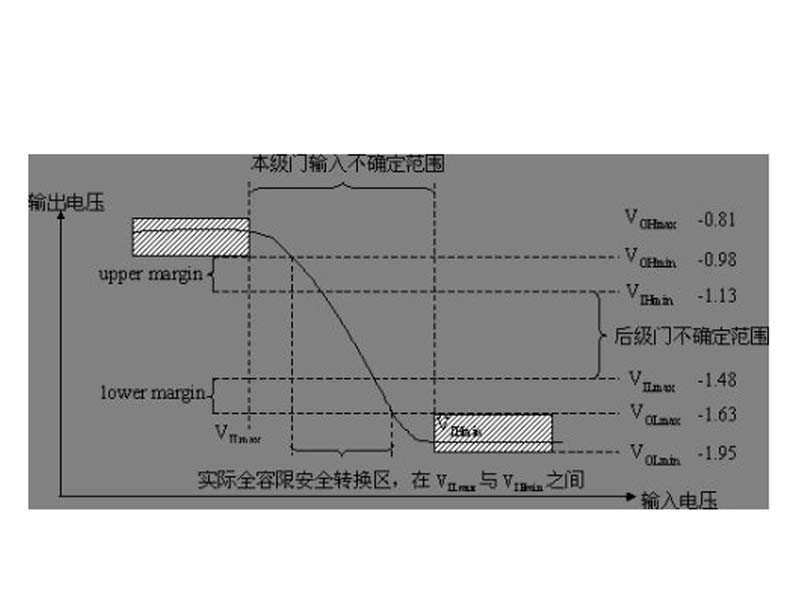

1)直流噪聲容限這是一個靜態參數,可以根據器件說明書所給出的4個極限參數,即高電平輸入電壓,低電平輸入電壓,高電平輸出電壓,低電平輸出電壓來求得輸入為低電平和輸入為高電平的直流噪聲容限。公式如下:

數字電路的直流噪聲容限與環境溫度、電源電壓有著很密切的關係。

2)交流噪聲容限又稱為動態噪聲容限。它與數字電路的反應速度有關,工作速度高的積體電路,其交流噪聲容限小,與直流噪聲容限值相接近。如電路本身反應速度慢,那么對於窄脈衝的快速干擾電壓就來不及反應,因而其容限值增大。所以交流噪聲容限通常比直流噪聲容限大。按理交流噪聲容限更能科學地反映電路在實際工作條件下的抗干擾能力,但交流噪聲容限測量困難,且與施加的干擾波形有關。所以往往採用直流噪聲容限值來衡量總體抗干擾能力,以求安全性更好。板間傳輸的信號,採用低速電路,會有更好的抗干擾性能。

3)能量噪聲容限ENI(EnergyNoiseImmunity) 即是在電路保持正常工作狀態下,電路所能承受的噪聲能量,其量綱為納焦耳nJ。單用直流噪聲容限不能全面地反映電路的抗干擾性能。能量噪聲容限這一概念指出:電路受噪聲干擾而發生誤動作,不僅需要有超過電路閾值的噪聲電壓幅值,而且還要具有使電路能產生干擾效應(如誤觸發、翻轉等)的能量。它與器件的閾值電壓、傳輸延遲時間及驅動側器件的輸出阻抗有關。能量噪聲容限定義為:

其中,是電路的閾值電壓,

是電路的傳輸延遲時間,

是電路的輸出阻抗.