介紹

由

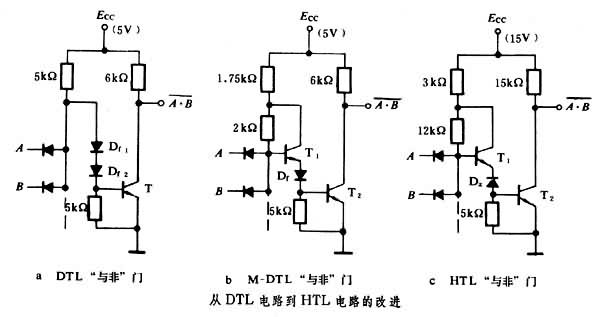

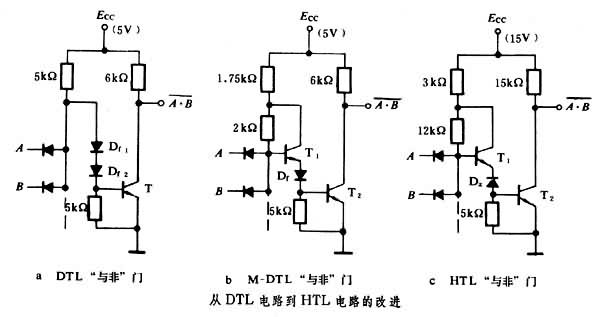

二極體-電晶體邏輯電路(DTL)和改進型二極體-電晶體邏輯電路(M-DTL)改進而來的一種高閾值雙極型中、低速數字積體電路,簡稱HTL電路。HTL電路具有很好的抗干擾性能。圖中表示從DTL電路到HTL電路的改進過程。

特點

HTL電路的主要特點,是用齊納二極體(D2)代替DTL、M-DTL電路中原來的電平位移二極體(Df)並將D2反接。齊納二極體的製造工藝與常規雙極型積體電路製備工藝相同,所以齊納二極體可在

雙極型積體電路製造過程中形成。通常,利用電晶體基極與集電極短路的eb結,即發射區和基區間的 P+N+結製成。齊納二極體的反向擊穿電壓一般約為6.7伏,要使其通導,必須有約6.7伏的電壓降。因此,它使HTL電路的閾值電壓提高到約為6.7+0.7=7.4伏,比一般DTL電路的閾值電壓約高6伏。正是利用齊納二極體的反向特性,使電路的輸入低電平的噪聲容限,從原來的1伏提高到約6伏;而輸入高電平的級聲容限,取決於電源電壓的高低。如採用12伏電源,只能獲得約3伏的輸入高電平的噪聲容限。因此,輸入高、低電平的抗噪聲能力是不對稱的。為了獲得對稱的輸入高、低電平的抗噪聲能力,一般採用15伏電源,從而使電路的輸入高、低電平的噪聲容限均達到6伏左右,可顯著提高電路的抗干擾能力。HTL電路適用於對速度要求不高,而對抗干擾能力要求很高的電子系統,如數控工具機、工業控制機、循回檢測裝置、數位化儀表等電子設備。它能使這些設備在惡劣的干擾環境中正常工作而又不必採取過多的附加措施。

為了限制 HTL電路的功耗隨電源電壓的提高而增大,常採用高阻值電阻進行限流。高阻值的電阻在版圖設計中占用較大的面積,從而限制了集成度的進一步提高。因此,HTL電路只適用於中、小規模積體電路。