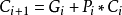

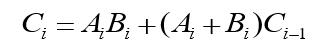

先行進位加法器,各級的進位彼此是獨立產生,只與輸入數據A,B和C_in有關,將各級間的進位級聯傳播給去掉了,這樣就可以減小進位產生的延時。

基本介紹

- 中文名:先行進位加法器

- 外文名:anticipated carry adder

- 學科:計算機科學與技術

- 類別:並行進位加法器

- 特點:進位只與輸入數據A,B和C_in有關

- 優勢:減小延遲

基本概念

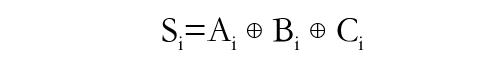

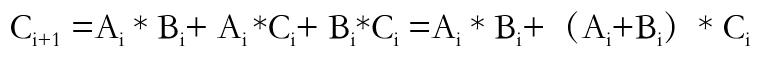

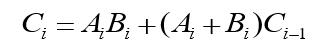

原理

超前進位加法器

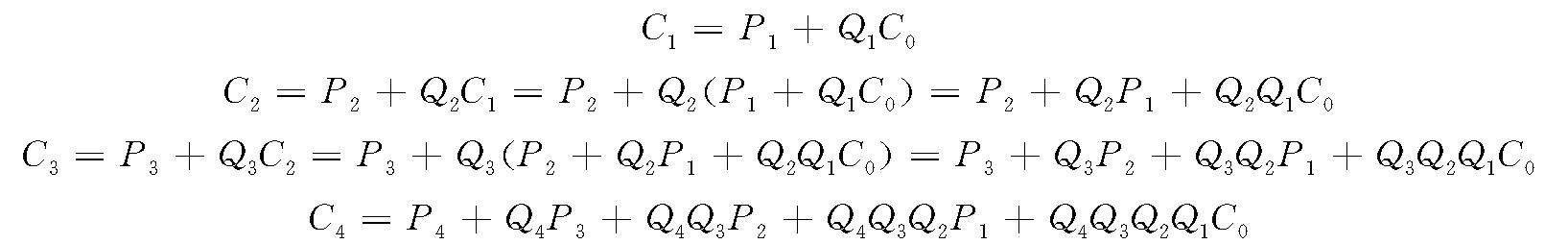

4位超前進位加法器

先行進位加法器,各級的進位彼此是獨立產生,只與輸入數據A,B和C_in有關,將各級間的進位級聯傳播給去掉了,這樣就可以減小進位產生的延時。

先行進位加法器,各級的進位彼此是獨立產生,只與輸入數據A,B和C_in有關,將各級間的進位級聯傳播給去掉了,這樣就可以減小進位產生的延時。...

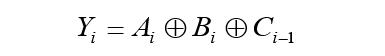

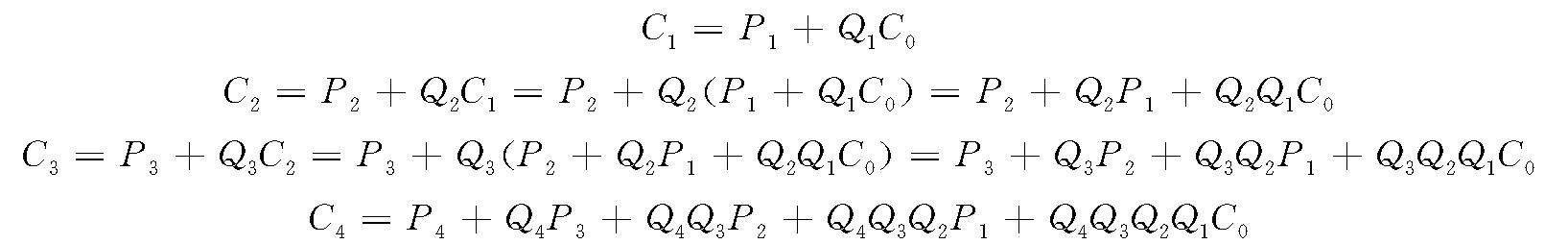

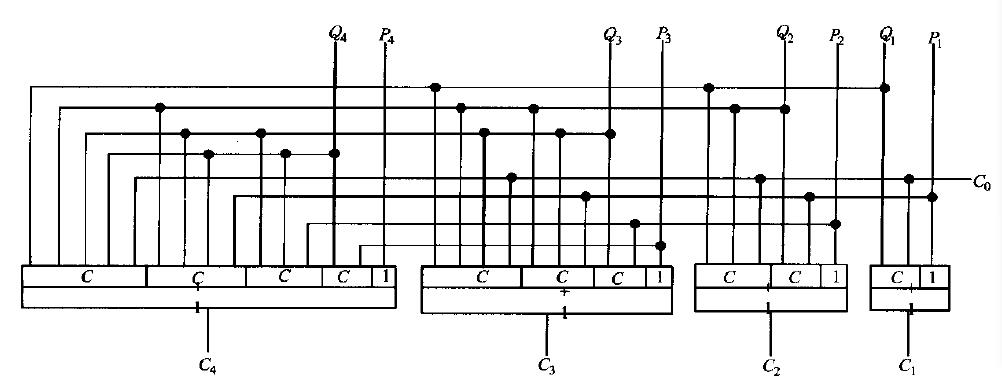

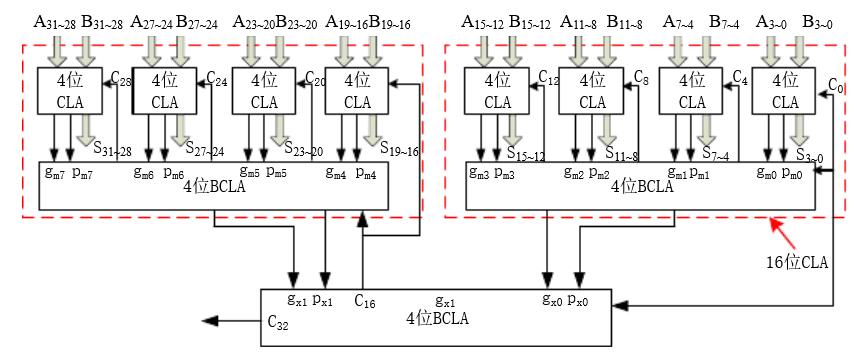

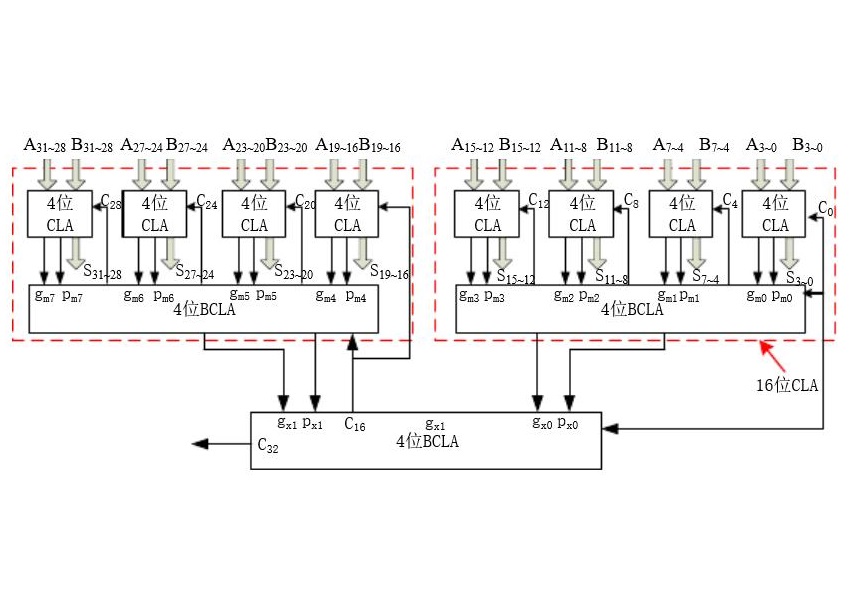

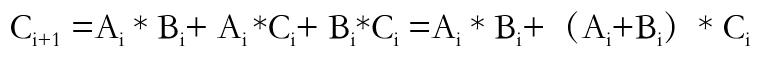

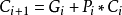

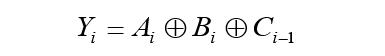

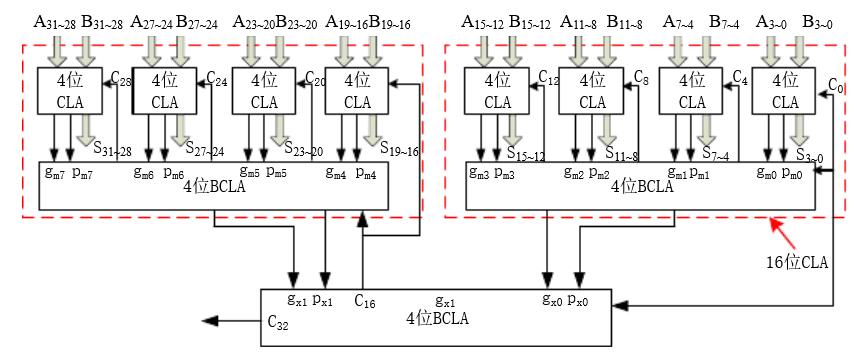

超前進位加法器(Carry-Lockahead Adder)是對普通的全加器進行改良而設計成的並行加法器,主要是針對普通全加器串聯時互相進位產生的延遲進行了改良。超前進位加法器...

實現多位數相加的具體電路是很多的,其中有一種就是採用所謂並行相加、逐位進位的方式。逐位進位的加法器,邏輯電路比較簡單,缺點是運算速度比較慢,因為最高位的加法...

串列二進制加法器即加法器執行位串列行操作,利用多個時鐘周期完成一次加法運算,即輸入運算元和輸出結果方式為隨時鐘串列輸入/輸出。...

電子加法器是一種用於執行加法運算的數字電路部件,是構成電子計算機核心微處理器中算術邏輯單元的基礎。在這些電子系統中,加法器主要負責計算地址、索引等數據。除此...

4.8.5 MSI加法器 4.8.6 MSI算術邏輯單元 4.8.7 組間先行進位 4.8.8 用VHDL實現加法器 參考資料 訓練題 練習題 第5章 時序邏輯設計原理 5.1 雙穩態元件 5...

11.1.3 先行進位加法器141 11.2 減法運算實現144 11.3 比較運算實現145 11.4 移位器145 11.5 本章小結146 習題147 第12章 定點補碼乘法器148 12.1 補碼...

存儲器、cache和虛擬存儲器管理以及帶有cache、tlb和fpu的cpu設計;多核cpu的...3.2.2 先行進位加法器設計3.3 乘法算法及Verilog HDL實現3.3.1 無符號數...

3.3.2 先行進位加法器 753.4 減法器 813.5 2的補碼加法/減法器 833.6 算術邏輯單元 863.6.1 設計部分:位並行 873.6.2 設計部分:位串列 91...

5.2.4分塊式先行進位加法器線路1255.3一個商售ALU晶片設計的分析1285.3.1基於加法器的ALU的組織1285.3.2針對邏輯操作進行輸入線路的設計129...

4.2BCD加法器4.332位加法器4.3.1先行進位加法器4.4交通燈控制器4.5控制電路狀態圖4.6記分板和控制器4.6.1數據通道4.6.2控制器4.6.3VHLD模型...

《數字電子技術與微處理器基礎(上冊)——現代數字電子技術》是2015年西安電子...7.4.1 一位二進制加法器 1947.4.2 單級和多級先行進位加法器 195...

然而,眾多的數據位數不能容忍行波加法器中進位過程的延時,光學部件又很難實現先行進位加法器中的進位樹結構,在三值光學計算機研究的初期,研究者們就注意到這個難題,...

該書包含了豐富的設計實例,從簡單的二進制加法器到複雜的微處理機設計,書中都...4.2 BCD加法器4.3 32位加法器4.3.1 先行進位加法器4.4 交通燈控制器...