優勢

設計特點 NetMagic 平台設計特點主要體現在:1)基於部分可程式

交換機 體系結構設計 ,為用戶提供豐富靈活的工作模式;2)通過將用戶邏輯與通用

報文 處理邏輯分離並提供良定義接口,可有效簡化用戶

邏輯設計 工作;3)通過通用的基於

乙太網 的NetMagic

訪問控制 協定NMAC,為平台管理提供良好兼容性和可移植性;4)通過提供高速擴展接口,有效支持控制及處理能力的擴展。

NetMagic平台 實物圖

研發背景 當前,

三網融合 、物聯網、

雲計算 以及IPv6過渡等概念和技術的提出和興起,一方面有力推動了下一代網際網路(Next Generation Internet,NGI)及相關技術的研究和發展,另一方面也對

網路技術 ,尤其是

網際網路技術 的創新帶來了前所未有的壓力和挑戰。大量成熟商用網路設備及協定的部署在有力推動網際網路普及套用的同時,其封閉性也為網路技術創新帶來不可忽視的障礙。出於智慧財產權及安全性考慮,傳統商用網路設備(

路由器 、

交換機 等)通常採用封閉式設備形態。新功能的集成被設備生產廠商嚴格控制,以防代碼泄漏或設備的可靠性及可用性受到損害。第三方難以獲得授權,無法在商用平台上展開技術創新和新功能的集成、測試及驗證工作。網路技術研究者提出的各種新型協定和機制也難以在真實網路中部署和實驗,網路技術創新正面臨嚴峻的瓶頸。

為此,基於Emulab的

網路安全 試驗設備DETER、提供良定義的抽象模型的

OpenFlow 交換機 、

網路科研 教學評估板NetFPGA等平台相繼推出,然而,這些平台在可靠性、擴展性、依耐性以及邏輯開發難度等方面存在一定限制。為了解決這些問題,研究者開發了一款開放式高擴展性的網路實驗平台——NetMagic。

套用領域 NetMagic平台具有硬體可重構性和軟體控制可程式性的特點,內部的計算

存儲 模組以及豐富的功能擴展接口為該平台提供了必要的計算存儲能力支持。NetMagic實驗平台獨特的結構設計和豐富的功能支持使得其可適用於很多領域,例如網路教學、

網路科研 、專用網路建設等。

在網路教學方面,NetMagic實驗平台提供了豐富的開放式硬體構件和軟體模組等基礎資源,並基於上述資源實現乙太網

交換機 、IPv4

路由器 、Openflow交換機等參考設計,使用NetMagic實驗平台可以使學生們避免浪費精力在複雜而繁瑣的實驗平台搭建上。基於該平台,學生可以了解網路

報文 的

基本處理 流程,掌握網路系統報文處理機制和協定工作原理。NetMagic平台為用戶自定義邏輯(UM)的集成提供了良定義的接口,學生可以在NetMagic預置的基本數據通路等模組的基礎上,快速高效地將自己的核心網路處理業務集成和部署在NetMagic平台中,實現例如標準乙太網交換機UM、

路由器 轉發引擎UM、Openflow分組處理UM等網路處理功能,從而加深對

網路設備 內部工作原理的理解,從而有效提高學生網路技術創新能力和工程實踐能力。

在網路創新研究方面,NetMagic實驗平台通過“部分可程式交換機系統”專利設計提供了強大的可重構特性和線速報文轉發能力。NetMagic平台通用可程式邏輯加商用高速交換晶片的獨特設計結構,一方面為大規模真實實驗環境構建提供有效支撐,另一方面則在新型網路協定、業務和服務的快速部署提供了支持。通過簡潔良定義的控制協定和接口,研究人員可以通過外部控制器控制NetMagic對網路報文流的處理行為。此外,NetMagic實驗平台還提供了計算

存儲 擴展能力,使得研究人員可以在實驗節點上部署更加豐富的網路管理、處理和計算業務及服務。

目前,基於NetMagic實驗平台已經實現和正在開展很多前沿的網路創新技術研究。國家“973計畫”的“大規模流媒體傳輸”正是基於該實驗平台進行了新型傳輸協定功能實現,有效驗證了其中流量檢測、負載均衡、數據轉發控制等創新技術;國家“863計畫”的“可重構路由器構件組研製”也基於NetMagic平台進行了業務處理子系統的原型系統構建和實驗;國家“863計畫”緊急啟動項目“三網融合演進技術與系統研究”也擬採用NetMagic平台作為構建網路演示驗證環境的核心平台,評價、驗證及展示各子課題的創新型研究成果。NetMagic平台為網路技術創新提供快速原型系統部署和大容量高性能的報文轉發能力,是一個理想的網路技術創新實驗平台。

基本結構 NetMagic平台採用新型部分可程式交換機體系結構技術設計實現,將商用乙太網交換晶片和大容量FPGA有機結合,可提供高連線埠密度下報文線速交換轉發能力,提供豐富的工作模式配置,有效支持用戶自定義報文處理邏輯集成。此外,通用的管理控制接口則使NetMagic避免平台相關性可能導致的兼容性和可移植性問題。NetMagic運行時以報文轉發為基礎,內部並不含CPU,自身無法運行任何作業系統,對於某些相對簡單固定的套用,通過FPGA編程時的一些設定,可以完成預定任務。除此之外對於某些複雜靈活的套用,還需要一台外部主機對它進行配置。我們自主開發了一套NMAC協定,通過乙太網報文的形式傳到FPGA的管理配置接口,然後由FPGA對這些命令和配置報文進行解析,改變NetMagic的轉發行為。

NetMagic基本結構 4.1 硬體處理流程

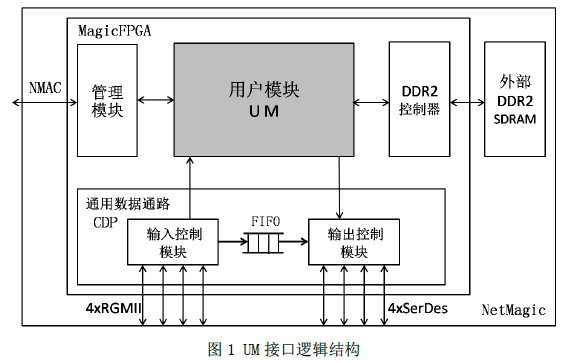

NetMagic以一片中等規模FPGA為核心,稱之為MagicFPGA。NetMagic08外設4個RJ45電口和4個SERDES光口。為了可以對報文進行重組,NetMagic08還設計了一片512Mb的DDR2 SDRAM進行報文快取。報文從某個連線埠進入FPGA,根據轉發規則決定是否將報文送入DDR2快取,或者決定報文從哪個連線埠輸出。轉發規則由外部控制主機通過NMAC協定進行配置。

UM與CDP輸入控制時序圖 4.2 軟體處理流程

NetMagic的軟體處理依靠NMAC協定進行,NMAC協定是NeMagic管理模組和外部控制主機之間的一種訪問控制協定,提供雙方通信機制並定義相關的規範。和NetMagic24平台類似,NetMagic08平台也是以一片MagicFPGA為核心,完成報文的查錶轉發和相同配置管理。MagicFPGA內部的管理模組負責基於NMAC協定與外部控制主機建立連線,並對管理報文中的命令進行解析,轉換為匯流排命令,完成對NetMagic平台中功能模組控制以及存儲器管理等工作。在Netmagic08平台中,管理配置接口使用靜態MAC地址和IP位址,在平台初始化時將MAC地址和IP位址燒入硬體中,可以通過硬體編程進行修改。

4.3 MagicFPGA工作模式

MagicFPGA是NetMagic平台實現可定製報文處理功能的核心,其主要為用戶提供可重構報文交換模組和平台無關的管理接口,如圖3所示。為有效簡化用戶自定義報文處理功能的開發實現,可重構交換模組預置通用數據通路(Common Data Path,CDP)功能,負責提供報文的接收、傳送、複製等基本通用處理原語,並在對存儲器接口等複雜邏輯進行封裝的基礎上,為用戶模組(User Module,UM)提供清晰的良定義接口。基於NetMagic平台開發時,用戶僅需專注於UM中自定義邏輯的實現,而不必考慮網路接口、數據緩衝、平台管理等其它複雜邏輯的實現。

使用技巧 5.1 UM的總體結構

用戶模組User Module簡稱UM,是MagicFPGA中用戶可自行開發的唯一模組,其它模組的硬體代碼和功能已經固定。圖4 表明了NetMagic08平台上的MagicFPGA中用戶模組UM和其它模組的關係。雖然NetMagic平台的硬體代碼是全部公開的,理論上用戶可以修改全部代碼,但對於初學者,我們建議只修改UM中的代碼功能。UM通過相關接口與CDP、管理模組和DDR2控制器相連。UM與CDP之間的接口分為輸入控制接口和輸出控制接口,主要是接收和傳送數據報文,完成數據報文的傳輸;UM與管理模組之間的接口主要通過NMAC協定軟體對UM內部暫存器或內嵌RAM表進行訪問控制;UM與DDR2控制器之間的接口完成片外DDR2 SDRAM中的緩衝報文和其它數據的訪問。DDR2片外存儲器的訪問相對來說比較複雜,初學者可以先不掌握。

CDP的輸入控制模組和輸出控制模組之間還有一個輸入輸出緩衝FIFO,可以直接將報文從輸入控制模組旁路到輸出控制模組,而不經過UM。UM與各個模組之間的接口功信號定義和時序關係在下面的小節中將詳細介紹。用戶可以根據需要,實例化必需的接口,設計出自己的UM。對於最簡單的報文轉發和路由查找等套用,用戶只需要實例化與UM與CDP之間的接口和與管理模組之間的接口。

5.2 UM的引腳說明

UM與MagicFPGA內部其它模組的接口信號定義如表1所示。主要列出了與CDP、管理模組和DR2控制器的引腳信號名稱及相關說明。其中,表1中的信號方向是相對UM而言。表1 UM與相連模組的引腳信號列表

在NetMagic24上此位對應一個外部百兆管理連線埠,在NetMagic08上這個連線埠不再保留了,而是任選一個物理連線埠作為管理連線埠,因此此位保留。

5.3 UM報文處理流程

UM和CDP緊密相連,直接面對CDP的輸入控制模組和輸出控制模組。CDP的輸入控制模組將報文同時往兩個方向複製:CDP輸入輸出FIFO和UM。UM一邊接收報文,一邊提取報文的關鍵字,生成規則信息。規則信息在報文尾到達前生成完畢,然後等待CDP輸出控制模組的許可,即看到CDP的規則FIFO有空閒空間時(um2cdp_rule_usedw<5'd30),將規則信息送往CDP的輸出控制模組。

CDP的輸出控制模組解析UM送來的規則信息,根據規則信息的最高位決定從哪條路徑讀取

報文 。由於規則信息是在

報文 尾到達時送往CDP輸出控制模組的,所以一旦輸出控制模組解析完規則信息並決定轉發報文時,一定有一個完整的報文在等待著它,這個報文要么在CDP輸入輸出FIFO中,要么在UM中。剩下的事情就很簡單了,CDP輸出控制模組一邊解析規則信息,一邊轉發

報文 。

報文 具體送往哪幾個連線埠由規則信息指定。

回頭再看看MagicFPGA的工作模式,可以知道,無論哪種模式,都需要UM產生相應的規則信息。即使處於旁路處理模式,也需要UM產生規則信息,告訴CDP輸出控制模組如何轉發

報文 。因此旁路可處理模式並不意味著用戶可以不做任何事情,這是本文需要提醒用戶注意的。規則是一個更接近軟體的概念,實際上UM在產生規則信息的時候也遵循了這個原則,規則可以由MagicFPGA靜態產生,也可以由軟體通過NMAC協定動態配置,這與NetMagic平台倡導的開放可重構的理念是相吻合的。

5.4 UM接口時序關係

下面,對各個模組之間的時序關係作一介紹,具體內容技術論壇有詳細呈現,如有需要,可以移步至相關資料社區閱讀參考。

5.4.1 輸入控制模組

當UM模組資源空閒,有能力從CDP接收一個新的

報文 時,則給CDP輸入控制模組一個傳送使能信號cdp2um_tx_enable。從5.3節可知,CDP輸入控制模組獲得該使能信號後,同時向UM和輸入輸出FIFO傳送139位寬的報文數據cdp2um_data,並傳送一個報文有效信號cdp2um_data_valid,此信號表明了報文的開始、中間和結束。UM一旦獲得了報文的頭部,就可以取消使能信號cdp2um_tx_enable,直到報文接收完畢。輸入控制模組給UM的報文是連續的。當一個報文傳送結束後,UM可以重新產生髮送使能信號,進行下一個報文的上傳,如此循環操作。具體操作步驟如下:

UM傳送請求報文使能信號cdp2um_tx_enable為高;CDP輸入控制模組收到cdp2um_tx_enable時,檢測是否有一個完整報文等待傳送,若有,則把cdp2um_data_valid信號置高,同時連續傳送數據;若沒有,CDP輸入控制模組等待,cdp2um_tx_enable一直為高;其中,當UM檢測到cdp2um_data_valid信號為高時,取消使能信號(置cdp2um_tx_enable為低);當一個報文傳送結束後,CDP輸入控制模組置cdp2um_data_valid信號為低,此時,如果UM再需要報文數據時,需要重新置cdp2um_tx_enable為高,如此循環。

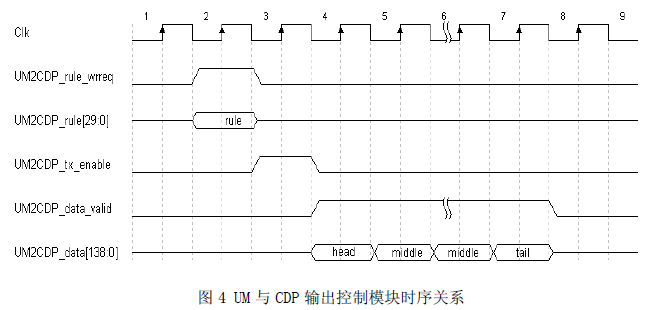

5.4.2 輸出控制模組

UM向CDP輸出控制傳送匹配規則和相應的

報文 數據,具體操作步驟如下:

UM接收到一個

報文 尾,且規則FIFO有剩餘空間時,將規則寫信號um2cdp_rule_wrreq置高一拍,同時把匹配規則傳送給CDP輸出控制模組;CDP輸出控制模組將規則信息存到一個規則FIFO中,然後根據下游的資源情況從FIFO中讀取規則信息,根據規則中的定義(bit[29]),判斷該規則綁定的報文是來自UM或是輸入輸出緩衝FIFO。所謂下游的資源情況是指下游的

狀態機 處於空閒狀態,有能力讀取和傳送一個新的報文。如果綁定為輸入輸出控制FIFO(bit[29]為1),則從輸入輸出緩衝FIFO中讀出一個

報文 ;如果是綁定自UM(bit[29]為0),則給UM一個數據傳送使能信號um2cdp_tx_enable;UM檢測到um2cdp_tx_enable為高時,則把um2cdp_data_valid信號置高,連續傳送報文給CDP輸出控制模組;報文傳送結束後UM置um2cdp_data_valid信號為低,同時等待下一次操作。

5.4.3 UM 與管理模組

管理模組把解析後的命令及數據傳送給UM。UM獲得命令及數據後,對相應的

地址空間 進行讀寫操作。如果為讀操作,則UM需要向管理模組返回從相應地址中讀出的數據及應答信號;如果為寫操作,則UM完成寫操作後,只需返回應答信號即可。因此,根據UM獲得的讀寫兩種操作命令,UM與管理模組之間的接口時序關係也分為read和write兩種。管理模組與UM之間讀操作步驟:

管理模組輸出讀請求、地址;管理模組24ns之後輸出

地址鎖存 信號ale。高有效;管理模組24ns之後撤掉

地址鎖存 信號;UM檢測到ale的下降沿,採樣地址並判斷。如果為自己的

地址空間 則繼續往下執行。如果不為自己的

地址空間 則不繼續往下執行而是等待下一次操作。管理模組24ns之後撤掉讀地址,輸出

片選 。低有效;UM檢測到

片選信號 為0,進行讀操作、返回讀數據data_out,等數據穩定之後將ack_n信號置0;管理模組檢測到ack_n信號為0,採樣數據data_out,撤掉片選、讀請求;UM檢測到片選信號為1,撤掉ack_n信號;管理模組檢測到ack_n變為1,可以發起下一次操作。 管理模組與UM之間寫操作步驟:

管理模組輸出寫請求、地址;管理模組24ns之後輸出

地址鎖存 信號。高有效;管理模組24ns之後撤掉地址鎖存信號;UM檢測到ale的下降沿,採樣地址並判斷。如果為自己的地址空間則繼續往下執行。如果不為自己的

地址空間 則不繼續往下執行而是等待下一次操作;管理模組24ns之後撤掉寫地址,輸出寫數據;管理模組24ns之後輸出

片選 。低有效;UM檢測到

片選信號 為0,進行寫操作,寫操作完成之後將ack_n置0;管理模組檢測到ack_n信號為0,撤掉片選、請求;UM檢測到片選信號為1之後,撤掉ack_n;管理模組檢測到ack_n信號變為1之後,可以發起下一次操作。

5.4.4 DDR2 控制器時序

UM與DDR2_CTRL之間的操作包括讀操作和寫操作。當UM模組檢測到um2ddr_ready為高時(即DDR2準備完畢時),才能向DDR2傳送操作命令。

寫操作時,用戶將需要存儲的數據寫入數據FIFO(um2ddr_data_fifo)之後再將命令、首地址及偏移量寫入命令FIFO(um2ddr_command_fifo)。

讀操作時,用戶將命令、首地址及偏移量寫入命令FIFO(um2ddr_command_fifo)。DDR2_CTRL將讀出的數據寫入數據FIFO(ddr2um_data_fifo)之後再將返回的數據信息寫入命令FIFO(ddr2um_command_fifo)。UM檢測ddr2um_valid_empty信號為0時,表示有數據返回,讀取命令FIFO(ddr2um_command_fifo)和數據FIFO(ddr2um_data_fifo)取出結果。

DDR2接口控制器是用Altera的IP核實現的,由於這部分的功能比較複雜,建議用戶將資源更多地用在對本文轉發的處理上,因此UM與DDR2接口控制器之間的接口

時序圖 本文尚未提供,有興趣的讀者可以參閱網站上的相關資料和Altera的文檔。

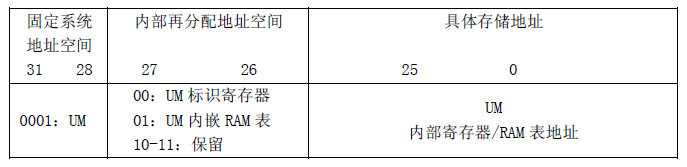

5.5 UM內部暫存器定義

UM內部暫存器是NetMagic平台中MagicFPGA暫存器的一部分。NetMagic

系統地址空間 分配如表2;UM內部暫存器空間的分配如表3;UM標識暫存器地址空間分配如表4;用戶可以通過NMAC協定,傳送

報文 對CDP各個暫存器進行讀取,從而達到讀取連線埠狀態的目的。UM標識暫存器均為32位寬,具體定義如表5;用戶可以根據實際RAM表的大小,確定內嵌RAM表地址具體需要多少位。如果26位地址也不能滿足設計時,可以構造內嵌

鍊表 進行擴充。

UM內部暫存器地址空間分配表 5.6 MagicFPGA數據格式

CDP及UM的內部

報文 數據寬度都是139位,其中低16個位元組為

報文 數據,高11位為帶外控制信息。CDP和UM中的各個功能模組可以根據帶外控制信息對

報文 進行判斷,以確定處理方式。同時,因為報文全部為

乙太網 格式報文,所以最少為64個位元組,即四拍數據,不會出現首尾同拍的情況。

說明:

頭尾標識[138:136]:

其餘保留。

輸入連線埠號port_num[131:128]:為4位通道號(僅在報文頭標識),對應MagicFPGA中的8個物理連線埠,序號為0-7。序號8-15保留。有效位元組數Vbyte[135:132]:僅在報文尾部有效,頭部和中間默認16個位元組全部有效。1111:16個位元組全部有效;

1110:最高15個位元組有效;

1101:最高14個位元組有效;

依次類推;

0000:最高1個位元組有效。

NetMagic平台 實物圖

NetMagic平台 實物圖 NetMagic基本結構

NetMagic基本結構 UM與CDP輸入控制時序圖

UM與CDP輸入控制時序圖

UM內部暫存器地址空間分配表

UM內部暫存器地址空間分配表