FPD-LINK II是收集寬並行匯流排和它的時鐘信號,進行有效負載的最佳化,追加串列控制位,轉換高速串列信號的電平到LVDS的電平。

基本介紹

- 中文名:平板顯示器鏈路

- 外文名:Flat-panel display Link

- 作用:筆記本顯示接口的實用標準

- 特點:串列差分信號

概述,串列器,串並轉換器,串列有效負載,套用,

概述

美國國家半導體嵌入式時鐘LVDS SerDes FPD-Link II系列具有強大的功能,超過了前幾代FPD-Link SerDes在顯示套用上的信號質量。 FPD-Link晶片組將寬並行RGB匯流排串列化為4或5對LVDS信號。18位RGB串列化為三組LVDS數據線和一個LVDS時鐘,而24位RGB則串列化為四組LVDS數據線和一組LVDS時鐘。這就提供了一個更小,更高速的視頻匯流排,並成為了筆記本顯示接口的實用標準。

FPD-Link II SerDes系列使寬並行匯流排串列化為下圖1所示的一個串列差分信號。因此獲得了24:1或更大的信號壓縮比(如果把地線也考慮進來)。系列中的現有晶片支持通用的18位和24位RGB顯示套用。由於消除了單串列信號和多線(多路)間的偏差問題,因此支持長達10米的電纜長度。這就使FPD-Link II SerDes理想用於低成本電纜的長距離套用。

單串列差分信號帶有並行數據(RGB和控制)信息,時鐘信息和小量串列損耗。單信號對的布線大大便利了系統設計,節省了大量互連、接線引腳,並減少了互連線口偏差的憂慮。

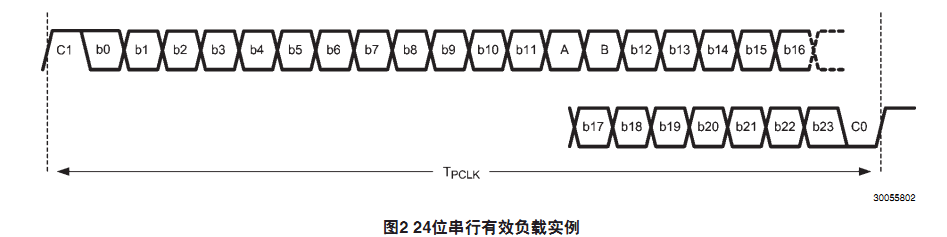

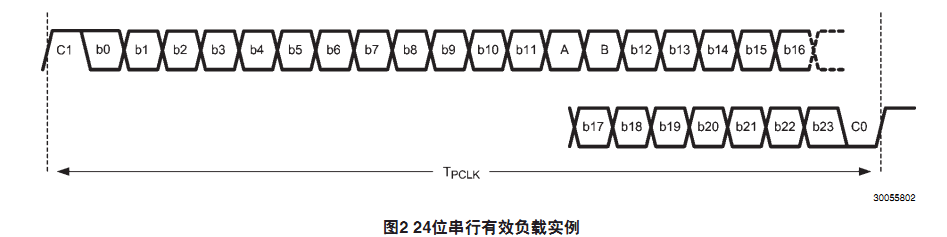

圖2示例了24位(用戶)有效負載。這24位數據區又追加

了四個額外的串列位,它們提供嵌入式時鐘信息,連結代碼

和工作模式信息。固定的時鐘邊沿在C0和C1位產生,編碼/模

式信息則由A&B位傳送。

串列器

串列器(SER)功能一般是收集寬並行匯流排和它的時鐘信號,進行有效負載的最佳化,追加串列控制位,轉換高速串列信號的電平到LVDS的電平。有效負載最佳化了AC耦合互連的串列傳輸。這一動作平衡了傳送給支持AC耦合傳輸的數據。取決於使用的晶片組,有效負載的隨機性和加擾性也提升了鏈路中的信號質量。

有些SER器件(取決於SER器件)可支持一些其它選項。可支持不同的輸入(平行)匯流排,這隨匯流排寬度和信號物理層而變。支持3.3V的LVCMOS匯流排,也支持一些產品可選的1.8V。另外,具有FPD-Link(基於LVDS)輸入的串列器轉換為FPD-Link II(即DS99R421和DS90UR907)。

串並轉換器

串並轉換器(DES)的功能是恢復時鐘和數據信號,並將他們提供給目標設備(例如一個顯示)。

FPD-Link II DES的獨特之處是因為它能夠快速鎖定串列數據流,而不需要Ser提供本地參考時鐘或任何特殊訓練圖形。這些特性使FPD-Link II SerDes和很多其它競爭產品中獨立出來。他們簡化了套用,支持熱插拔,且需要較少的外部元件(減少板空間和成本)。該DES甚至提供了LOCK輸出信號,允許系統檢查串列接口狀態。

有些DES器件(取決於DES器件)可支持一些其它選項。可支持不同輸出(平行)匯流排。這隨匯流排寬度和信號物理層而變。支持3.3V的LVCMOS匯流排,也支持一些產品可選的1.8V。另外,串並轉換器具有FPD-Link(基於LVDS)的輸出(即DS90UR908)。

串列有效負載

串列有效負載最佳化了FPD-Link II 系列的不同晶片組,同時也最佳化他們支持的那些套用。常見的串列有效負載的參考解釋就如上圖2所示的28位串列幀。28位串列幀的組成為:24位數據位、2位嵌入式時鐘信息和2位用於連結的串列控制位。因此,對於每24位的數據,實際傳送的是28位串列位。

這就是基本連結的效率24/28(86%)。這是一個重要的實驗數據,因為我們總是希望保持低損耗。此方案比通用的數據通信8b/10b方案(效率為80%)好30%。注意,24位數據被修改為平衡的、隨機的和加擾的數據。這樣做是為了支持連結上的交流耦合,並在傳送相對靜態的數據時,有助於減少ISI(碼間干擾)的影響。這兩個時鐘位是固定的,一位高(C1)一位低(C0) - 注意這兩個是直流平衡的一對。兩個串列控制位,通常被標註為DCA (A)和DCB (B),給DES提供信息以恢複數據、連結狀態和模式。支持24位RGB晶片組對串列數據流里的視頻同步信號的狀態進行編碼。