工作原理

動態RAM的工作原理 動態RAM也是由許多

基本存儲元按照行和列地址

引腳復用來組成的。

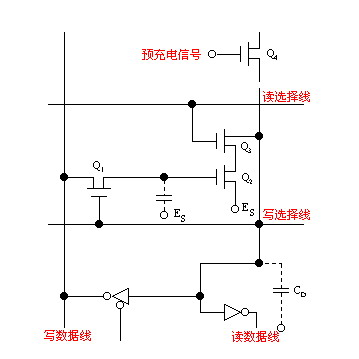

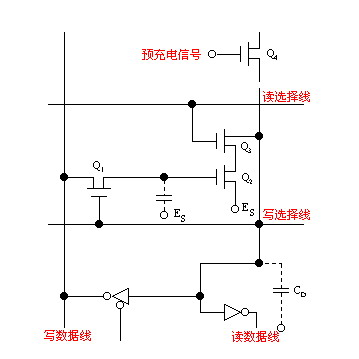

3管動態RAM的工作原理3管動態RAM的

基本存儲電路如右圖所示。在這個電路中,讀選擇線和寫選擇線是分開的,讀數據線和寫數據線也是分開的。

DRAM數據線

DRAM數據線寫操作時,寫選擇線為"1",所以Q1導通,要寫入的數據通過Q1送到Q2的柵極,並通過柵極電容在一定時間內保持信息。

讀操作時,先通過公用的預充電管Q4使讀數據線上的分布電容CD充電,當讀選擇線為高電平有效時,Q3處於可導通的狀態。若原來存有"1",則Q2導通,讀數據線的分布電容CD通過Q3、Q2放電,此時讀得的信息為"0",正好和原存信息相反;若原存信息為"0",則Q3儘管具備導通條件,但因為Q2截止,所以,CD上的

電壓保持不變,因而,讀得的信息為"1"。可見,對這樣的存儲電路,讀得的信息和原來存入的信息正好相反,所以要通過讀出放大器進行反相再送往

數據匯流排。

結構

在

半導體科技極為發達的中國台灣,

記憶體和顯存被統稱為

記憶體(Memory),全名是動態隨機存取記憶體(Dynamic Random Access Memory,DRAM)。基本原理就是利用電容

記憶體儲電荷的多寡來代表0和1,這就是一個二進制位元(bit),記憶體的最小單位。

DRAM的結構可謂是簡單高效,每一個bit只需要一個

電晶體另加一個電容。但是電容不可避免的存在漏電現象,如果電荷不足會導致數據出錯,因此電容必須被周期性的

刷新(預充電),這也是DRAM的一大特點。而且電容的充放電需要一個過程,刷新頻率不可能無限提升(頻障),這就導致DRAM的頻率很容易達到上限,即便有先進工藝的支持也收效甚微。隨著科技的進步,以及人們對

超頻的一種意願,這些頻障也在慢慢解決。

發展過程

“上古”時代的FP/EDO

記憶體,由於

半導體工藝的限制,頻率只有25MHz/50MHz,自SDR以後頻率從66MHz一路飆升至133MHz,終於遇到了難以逾越的障礙。此後所誕生的DDR1/2/3系列,它們

存儲單元官方頻率(JEDEC制定)始終在100MHz-200MHz之間徘徊,非官方(

超頻)頻率也頂多在250MHz左右,很難突破300MHz。事實上高頻

記憶體的出錯率很高、穩定性也得不到保證,除了

超頻跑簡單測試外並無實際套用價值。

既然

存儲單元的頻率(簡稱

核心頻率,也就是電容的刷新頻率)不能無限提升,那么就只有在I/O(輸入輸出)方面做文章,通過改進I/O單元,這就誕生了DDR1/2/3、GDDR1/2/3/4/5等形形色色的

記憶體種類

在其他領域的套用

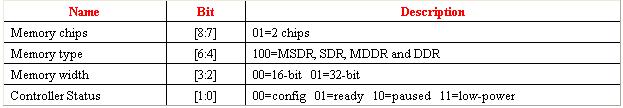

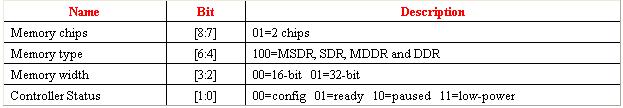

1. DRAM Controller Status Register (Address: 0x7E001000)

DRAM

狀態暫存器,這是一個RO暫存器,用於讀取DRAM的狀態。

實際上,讀到的有用信息就是Controller Status和Memory width。

2. DRAM Controller Command Register (Address: 0x7E001004)

最開始應該配置為0x4,是處於Configure狀態。在配置完所有的DRAM之後,將該

暫存器設定為0x0,處於運行狀態。

3. Direct Command Register (Address: 0x7E001008)

DRAM命令

暫存器,用於傳送命令到DRAM和訪問DRAM中的MRS和EMRS暫存器。

通過該暫存器初始化DRAM,先設定為NOP模式,然後設定為PrechargeAll進行充電,然後設定EMRS和MRS暫存器,一般是這么一個流程。具體的要參見你所使用的DRAM的datasheet。

4. Memory Configuration Register (Address: 0x7E00100C)

DRAM的配置

暫存器,這個與需要參照你所使用的DRAM的datasheet。

該

暫存器肯定是要配的,看看DRAM的datasheet就知道了。

DRAM相關專業術語:

1. | cache /DRAM controller

高速緩衝存儲器/動態隨機存取存儲器控制器 |

2. | dynamic random access memory (DRAM)

動態隨機存取存儲器 |

3. | memory, dynamic random access (DRAM)

動態隨機存取存儲器 |

4. | reduced latencyDRAMRA

時延減少型DRAM |

5. | Rapid LatencyDRAM

快速延遲DRAM |

3管動態RAM基本存儲電路

3管動態RAM基本存儲電路 DRAM數據線

DRAM數據線

3管動態RAM基本存儲電路

3管動態RAM基本存儲電路