CPU 設計是指設計中央處理器(CPU)的工程學,是計算機硬體(設計)的一部分,它是計算機工程和電氣工程中的一個分支。

基本介紹

- 中文名:CPU架構設計

- 外文名:CPU architecture design

- 學科:計算機硬體設計

細節

CPU設計關注

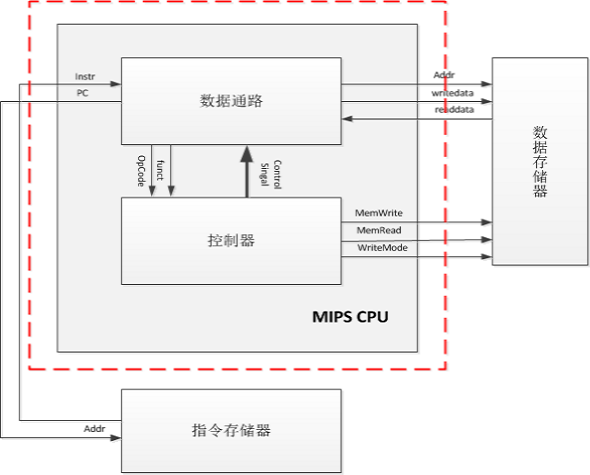

- 數據路徑(如ALU和計算管道)

- 控制單元:邏輯控制的數據路徑

- 記憶體元件,如暫存器檔案快取

- 時脈電路,如時脈驅動器,PLL,時鐘分配網路

- 墊收發器電路

- 邏輯門電路的實現

CPU 設計是指設計中央處理器(CPU)的工程學,是計算機硬體(設計)的一部分,它是計算機工程和電氣工程中的一個分支。

CPU 設計是指設計中央處理器(CPU)的工程學,是計算機硬體(設計)的一部分,它是計算機工程和電氣工程中的一個分支。...

CPU架構是CPU廠商給屬於同一系列的CPU產品定的一個規範,主要目的是為了區分不同類型CPU的重要標示。目前市面上的CPU分類主要分有兩大陣營,一個是intel、AMD為首...

處理器一般指中央處理器,中央處理器(CPU,Central Processing Unit)是一塊超大...計算機體系結構[J]. 計算機工程與設計, 1984(4):48-56.詞條標籤: 科學百科...

先進的製程技術為處理器性能的變革提供了一個良好的基礎,而優秀的核心架構則能夠彌補處理器主頻的不足,更能簡化快取設計而降低成本,二者結合才是優秀處理器的根基...

是一款領先節能的新型微架構,設計的出發點是提供卓然出眾的性能和能效,提高每瓦特性能,也就是所謂的能效比。早期的酷睿是基於筆記本處理器的。...

(一種CPU架構)編輯 鎖定 DEC Alpha,是64位的 RISC 微處理器,支持VMS作業系統、Linux和BSD。中文名 DEC 阿爾法 外文名 DEC Alpha 位數 64位的 RISC 微處理...

(CPU架構)編輯 鎖定 arch指“自回歸條件異方差模型”,由經濟學家恩格爾提出。...最初的設計思想來源於兩個Linux發行版:PLD和CRUX。PLD採用的是apt-get作為rpm...

微處理器內部結構 16位微處理器(圖中為8086微處理器)可分成兩個部分,一部分...PC的套用擴展到很多的領域,如商業辦公和計算、工程設計和計算、數據中心、個人...

多核心處理器架構是指晶片設計工程師在單個處理器中集成兩個或多個基於英特爾奔騰處理器的“執行核心(即計算引擎)”。多核心處理器可直接插入到單一處理器基座中。...

為了便於CPU設計、生產、銷售的管理,CPU製造商會對各種CPU核心給出相應的代號,...(這會降低CPU的生產成本從而最終會降低CPU的銷售價格)、更先進的流水線架構和...

各種CPU核心都具有固定的邏輯結構,一級快取、二級快取、執行單元、指令級單元和匯流排接口等邏輯單元都會有科學的布局。中文名 處理器核心 便於 CPU設計 又稱 核心...

Core微架構是由Intel位於以色列海法的研發團隊負責設計的。該以色列團隊早在2003年就因為設計出兼具高性能與低功耗的 Banias 處理器而聞名天下,Core 微架構也是他們...

可擴充處理器結構(SPARC,Scalable Processor Architecture)是RISC微處理器架構之一。它最早於1987年由Sun電腦所設計,也是SPARC國際公司的註冊商標之一。可擴展處理器...

架構過去稱作進階精簡指令集機器(Advanced RISC Machine,更早稱作:Acorn RISC Machine),是一個32位精簡指令集(RISC)處理器架構,其廣泛地使用在許多嵌入式系統設計。...

對英特爾而言, IA-64(英特爾的64位架構)是下一個10到15年的架構。新的ISA將使英特爾擺脫X86架構的限制,從而設計出超越所有現有RISC CPU和X86 CPU的新型處理器...

《開放式實驗CPU設計》是2007年6月清華大學出版社出版的圖書,作者是湯志忠 。...... 採取全新的實驗理念,允許實驗者自行設計指令系統和cpu的系統結構,能對cpu設計的...

外文名 P6架構 發布時間 1995 發布公司 Intel 特點 外部地址匯流排擴展至36位 1995年Intel發布首個專門為32位伺服器、工作站設計的處理器架構,即P6架構。其首...

處理器一般指中央處理器,中央處理器(CPU,Central Processing Unit)是一塊超大...計算機體系結構[J]. 計算機工程與設計, 1984(4):48-56 詞條標籤: 科學百科...

各種CPU核心都具有固定的邏輯結構,一級快取、二級快取、執行單元、指令級單元和匯流排接口等邏輯單元都會有科學的布局。為了便於CPU設計、生產、銷售的管理,CPU製造商會...

體系結構(architecture)規定了處理器的功能性行為,是處理器設計的規範。微體系結構(microarchitecture)是體系結構的具體設計,即處理器實現。...

架構:Alpha其中,SW1600處理器是江南計算所研製申威系列的第三代處理器,擁有16個...在各種需要浮點運算的套用中,例如3-D圖象處理和計算機輔助設計,21164才能顯示出...

為了便於CPU設計、生產、銷售的管理,CPU製造商會對各種CPU核心給出相應的代號,...其與Northwood最大的區別是採用了0.09um製造工藝和更多的流水線結構,初期採用...