基本概述

ARM9採用哈佛體系結構,指令和數據分屬不同的匯流排,可以並行處理。在流水線上,ARM7是三級流水線,ARM9是五級流水線。由於結構不同,ARM7的執行效率低於ARM9。平時所說的ARM7、ARM9實際上指的是ARM7TDMI、ARM9TDMI軟核,這種處理器軟核並不帶有MMU和cache,不能夠運行諸如linux這樣的嵌入式作業系統。而ARM公司對這種架構進行了擴展,所以有了ARM710T、ARM720T、ARM920T、ARM922T等帶有MMU和cache的處理器核心。

主要特性編輯

融合了ARM920T™ ARM® Thumb® 處理器

– 工作於180 MHz時性能高達200 MIPS,存儲器管理單元

– 16-K 位元組的數據快取,16-K位元組的指令快取,寫緩衝器

– 含有調試信道的內部仿真器

– 中等規模的嵌入式宏單元結構( 僅針對256 BGA 封裝)

· 低功耗:VDDCORE電流為30.4 mA 待機模式電流為3.1 mA

· 附加的嵌入式存儲器

– SRAM為16K ;ROM為128K

· 外部匯流排接口(EBI)

– 支持SDRAM,靜態存儲器, Burst Flash,無縫連線的CompactFlash®,

SmartMedia™及NAND Flash

· 提高性能而使用的系統外設:

– 增強的時鐘發生器與電源管理控制器

– 兩個有雙PLL的片上振盪器

– 低速的時鐘操作模式與軟體功耗最佳化能力

– 四個可程式的外部時鐘信號

– 包括周期性中斷、看門狗及第二計數器的系統定時器

– 有報警中斷的實時時鐘

– 調試單元、兩線UART並支持調試信道

– 有8 個優先權的高級中斷控制器,獨立的可禁止中斷源,偽中斷保護

– 7個外部中斷源及1 個快速中斷源

– 有122個可程式I/O口線的四個32 位PIO控制器,各線均有輸入變化中斷及開漏能力

– 20通道的外設數據控制器(DMA)

· 10/100 Base-T 型乙太網卡接口

– 獨立的媒體接口(MII)或簡化的獨立媒體接口(RMII)

– 對於接收與傳送有集成的28 位元組FIFO及專用的DMA 通道

· USB 2.0 全速(12 M比特/秒) 主機雙連線埠

– 雙片上收發器(208引腳PQFP封裝中僅為一個)

– 集成的FIFO及專用的DMA 通道

· USB 2.0 全速(12 M比特/秒) 器件連線埠

– 片上收發器, 2-K位元組可配置的集成FIFO

· 多媒體卡接口(MCI)

– 自動協定控制及快速自動數據傳輸

– 與MMC及SD存儲器卡兼容,支持兩個SD存儲器

· 3個同步串列控制器(SSC)

– 每個接收器與傳送器有獨立的時鐘及幀同步信號

– 支持I2S模擬接口,時分復用

– 32比特的高速數據流傳輸能力

· 4個通用同步/異步接收/傳送器(USART)

– 支持ISO7816 T0/T1 智慧卡

– 硬軟體握手

– 支持RS485 及高達115 Kbps的IrDA 匯流排

– USART1為全調製解調控制線

· 主機/從機串列外設接口(SPI)

– 8~ 16 位可程式數據長度,可連線4個外設

· 兩個 3 通道16 位定時/計數器(TC)

– 3個外部時鐘輸入,每條通道有2 個多功能I/O引腳

– 雙PWM 產生器,捕獲/波形模式,上加/下減計數能力

· 兩線接口(TWI)

– 主機模式支持,所有兩線Atmel EEPROM 支持

· 所有數字引腳的IEEE 1149.1 JTAG邊界掃描

· 電源供應

– VDDCORE,VDDOSC及VDDPLL電壓為:1.65V ~1.95V

– VDDIOP (外設I/O) 及VDDIOM (存儲器I/O)電壓為:1.65V~ 3.6V

體系特點

結構特點

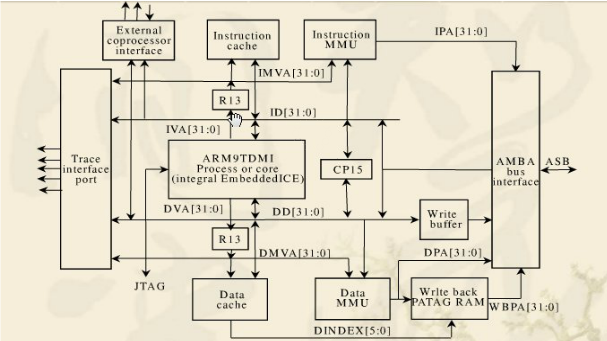

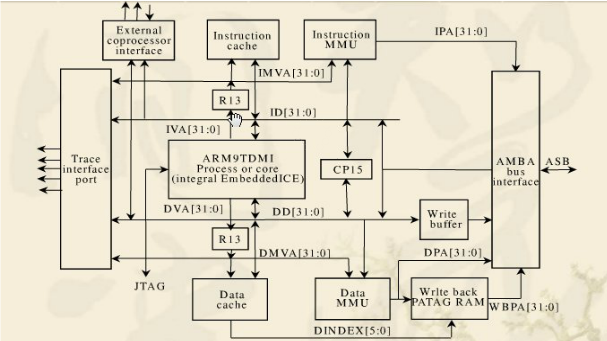

以ARM9E-S為例介紹ARM9處理器的主要結構及其特點。ARM9E-S的結構如圖4所示。其主要特點如下:

⑴32bit定點RISC處理器,改進型ARM/Thumb代碼交織,增強性乘法器設計。支持實時(real-time)調試;

⑵片內指令和數據SRAM,而且指令和數據的

存儲器容量可調;

⑶片內指令和數據高速緩衝器(cache)容量從4K位元組到1M位元組;

⑷設定保護單元(protection unit),非常適合

嵌入式套用中對

存儲器進行分段和保護;

⑺支持標準基本

邏輯單元掃描測試方法學,而且支持BIST(built-in-self-test);

ARM920T運行模式

ARM920T支持7種運行模式,分別為:

(1)用戶模式(usr),

ARM處理器正常的程式執行狀態;

(2)快速中斷模式 (fiq),

用於高速數據傳輸或通道處理;

(3)外部中斷模式(irq),

用於通用的中斷處理;

(4)管理模式(svc),

作業系統使用的保護模式;

(5)數據訪問終止模式(abt),

當數據或指令預取終止時進入該模式,可用於虛擬存儲及存儲保護;

(6)系統模式(sys),

運行具有特權的作業系統任務;

(7)未定義指令中止模式(und)

當未定義的指令執行時進入該模式,可用於支持硬體協處理器的軟體仿真。

ARM微處理器的運行模式可以通過軟體改變,也可以通過外部中斷或異常處理改變。大多數的應用程式運行在用戶模式下,當處理器運行在用戶模式下時,某些被保護的系統資源是不能被訪問的。除用戶模式以外,其餘的6種模式稱為特權模式;其中除去用戶模式和系統模式以外的5種又稱為異常模式,常用於處理中斷或異常,以及訪問受保護的系統資源等情況。

ARM920T的工作狀態

從編程的角度看,ARM920T微處理器的工作狀態一般有兩種:

(1)ARM狀態,此時處理器執行32位的、字對齊的ARM指令;

(2)Thumb狀態,此時處理器執行16位的、半字對齊的Thumb指令。

ARM指令集和Thumb指令集均有切換處理器狀態的指令,在程式的執行過程中,微處理器可以隨時在兩種工作狀態之間切換,並且,處理器的工作狀態的轉變並不影響處理器的工作模式和相應暫存器中的內容。但ARM微處理器在開始執行代碼時,應該處於ARM

狀態。

當運算元暫存器的狀態位(位0)為1時,可以採用執行BX指令的方法,使微處理器從

ARM狀態切換到Thumb狀態。此外,當處理器處於Thumb狀態時發生異常(如IRQ、FIQ、Undef、Abort、SWI等),當異常處理返回時,自動切換回Thumb狀態。當運算元暫存器的狀態位為0時,執行BX指令可以使微處理器從Thumb狀態切換到ARM狀態。此外,在處理器進行異常處理時,將PC指針放入異常模式連結暫存器中,並從異常向量地址開始執行程式,也可以使處理器切換到ARM狀態。

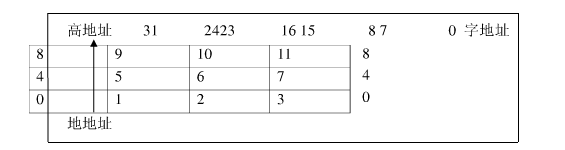

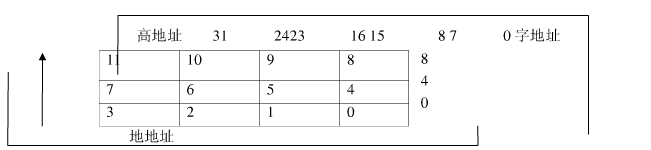

ARM920T體系結構的存儲器格式

ARM920T體系結構將存儲器看做是從零地址開始的位元組的線性組合。從0位元組到3位元組放置第1個存儲的字數據,從第4個位元組到第7個位元組放置第2個存儲的字數據,依次排列。作為32位的微處理器,ARM92OT體系結構所支持的最大定址空間為4GB。

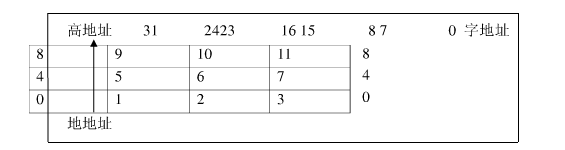

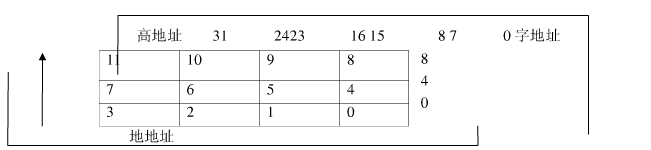

ARM92OT體系結構可以用兩種方法存儲字數據,分別稱為大端格式和小端格式。大端格式中字數據的高位元組存儲在低地址中,而字數據的低位元組則存放在高地址中

以大端格式存儲數據

以小端格式存儲數據

優勢

1). 時鐘頻率的提高

雖然ARM7和ARM9核心架構相同,但ARM7處理器採用3級流水線的馮·諾伊曼結構;,而ARM9採用5級流水線的哈佛結構。增加的流水線設計提高了時鐘頻率和並行處理能力。5級流水線能夠將每一個指令處理分配到5個時鐘周期內,在每一個時鐘周期內同時有5個指令在執行。在常用的晶片生產工藝下,ARM7一般運行在100MHz左右,而ARM9則至少在200MHz以上。

2) 指令周期的改進

指令周期的改進對於處理器性能的提高有很大的幫助。性能提高的幅度依賴於代碼執行時指令的重疊,這實際上是程式本身的問題。對於採用最高級的語言,一般來說,性能的提高在30%左右。

3).MMU(記憶體管理單元)

ARM7一般沒有MMU(記憶體管理單元),(ARM720T有MMU)。

ARM9一般是有MMU的,ARM9940T只有MPU ,不是一個完整的MMU。

這一條很重要,MMU單元是大型作業系統必需的硬體支持,如LINUX;WINCE等。這就是說,ARM7一般只能運行小型的實時系統如UCOS-II,eCOS等,而ARM9無此限制,一般的作業系統都可以移植。其實即使ARM720T能支持LINUX;WINCE等系統,也鮮有人用,因為以ARM7的運行速度跑這種大型作業系統,實在有點吃力。再者兩者的套用領域明顯不同,也無此必要。

指令

⒈loads 指令與n stores指令

指令周期數的改進最明顯的是loads指令和stores指令。從ARM7到ARM9這兩條指令的執行時間減少了30%。

指令周期的減少是由於ARM7和ARM9兩種處理器內的兩個基本的微處理結構不同所造成的。

⑴ARM9有獨立的指令和數據

存儲器接口,允許處理器同時進行取指和讀寫數據。這叫作改進型

哈佛結構。而ARM7隻有數據

存儲器接口,它同時用來取指令和數據訪問。

⑵5級流水線引入了獨立的

存儲器和寫回流水線,分別用來訪問存儲器和將結果寫回

暫存器。

以上兩點實現了一個周期完成loads指令和stores指令。

⒉互鎖(interlocks)技術

當指令需要的數據因為以前的指令沒有執行完而沒有準備好就會產生管道互鎖。當管道互鎖發生時,硬體會停止這個指令的執行,直到數據準備好為止。雖然這種技術會增加代碼執行時間,但是為初期的設計者提供了巨大的方便。編譯器以及彙編程式設計師可以通過重新設計代碼的順序或者其他方法來減少管道互鎖的數量。

⒊分枝指令

ARM9和ARM7的分枝

指令周期是相同的。而且ARM9TDMI和ARM9E-S並沒有對分枝指令進行預測處理。

處理能力

新一代的ARM9處理器,通過全新的設計,採用了更多的電晶體,能夠達到兩倍以上於ARM7處理器的處理能力。這種處理能力的提高是通過增加

時鐘頻率和減少指令執行周期實現的。

ARM7處理器採用3級流水線,而ARM9採用5級流水線。增加的流水線設計提高了

時鐘頻率和

並行處理能力。5級流水線能夠將每一個指令處理分配到5個

時鐘周期內,在每一個時鐘周期內同時有5個指令在執行。在同樣的加工工藝下,ARM9TDMI處理器的時鐘頻率是ARM7TDMI的1.8~2.2倍。

指令周期的改進對於處理器性能的提高有很大的幫助。性能提高的幅度依賴於代碼執行時指令的重疊,這實際上是程式本身的問題。對於採用最高級的語言,一般來說,性能的提高在30%左右。

典型套用

基於arm9核心的處理器,是具有低功耗,高效率的開發平台。廣泛用於各種嵌入式產品。它主要套用於音頻技術以及高檔工業級產品,可以跑linux以及wince等高級嵌入式系統,可以進行界面設計,做出人性化的人機互動界面,像一些網路產品和手機產品。