ARM9TDMI是基於ARM體系結構v4版本的高端ARM核(核並非晶片,ARM核與其他部件(如RAM、ROM、片內外設)組合在一起才構成現實的晶片)。

基本介紹

- 中文名:ARM9TDMI

- T:支持高密度Thumb指令集擴展

- D:支持片上調試

- M:支持64位乘法指令

簡介

ARM9與ARM7TDMI比較

10.1

10.1

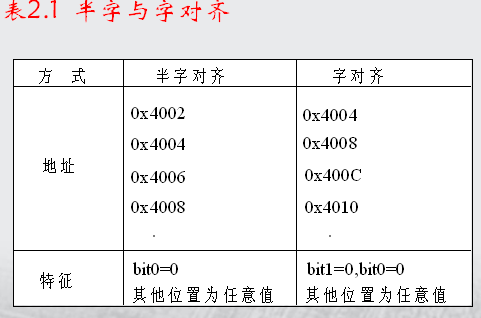

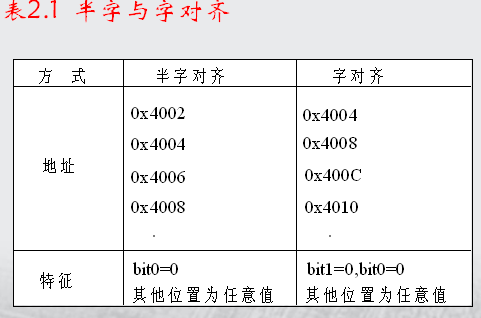

存儲器的字與半字

表2.1 半字與字對齊

表2.1 半字與字對齊

ARM9TDMI是基於ARM體系結構v4版本的高端ARM核(核並非晶片,ARM核與其他部件(如RAM、ROM、片內外設)組合在一起才構成現實的晶片)。

10.1

10.1

表2.1 半字與字對齊

表2.1 半字與字對齊ARM9TDMI是基於ARM體系結構v4版本的高端ARM核(核並非晶片,ARM核與其他部件(如RAM、ROM、片內外設)組合在一起才構成現實的晶片)。...

ARM9系列處理器是英國ARM公司設計的主流嵌入式處理器,主要包括ARM9TDMI和ARM9E-S等系列。...

ARM9是英國ARM公司設計的32位的嵌入式處理器,主要包括ARM9TDMI、ARM968E-S、ARM946E-S 和 ARM926EJ-S系列處理器。...

非常流行的ARM芯核有 ARM7TDMI, StrongARM, ARM720T, ARM9TDMI, ARM922T, ARM940T, RM946T, ARM966T, ARM10TDM1等。自V5以後,ARM公司提供Piccolo DSP的...

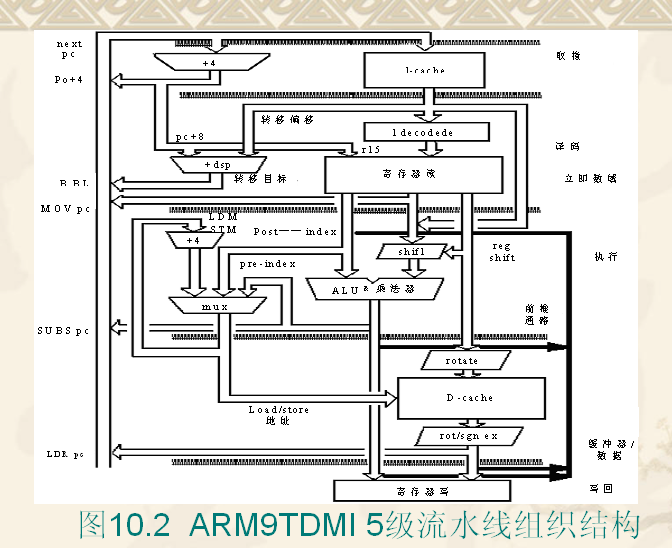

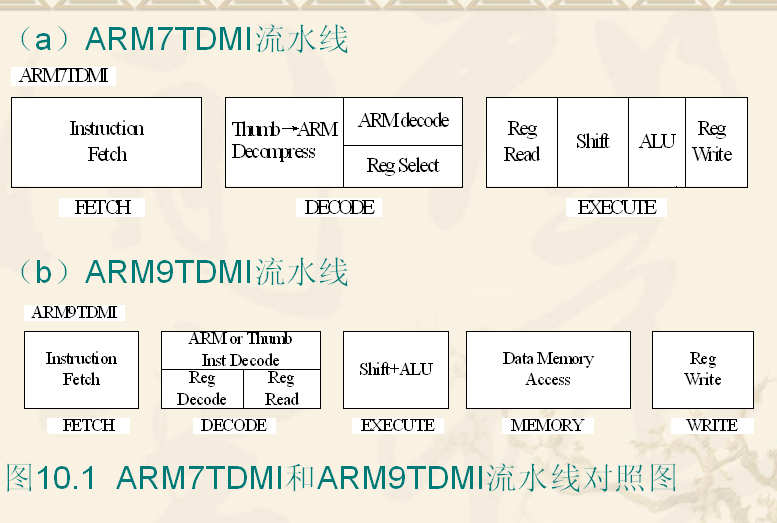

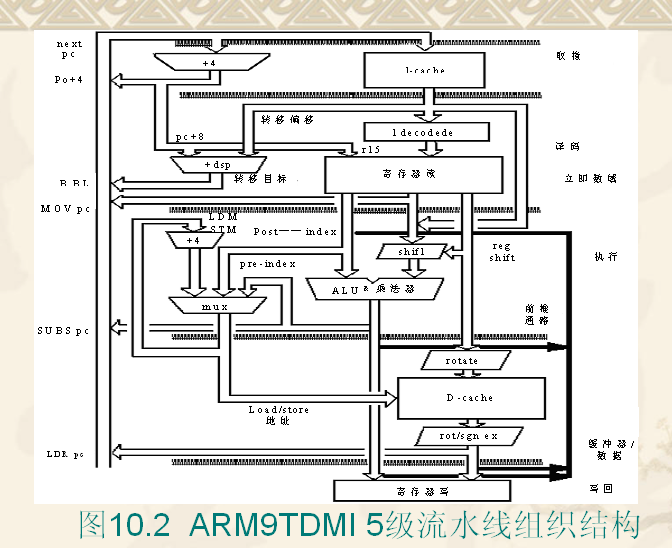

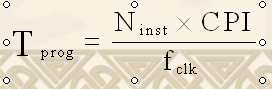

在同樣的加工工藝下,ARM9TDMI處理器的時鐘頻率是ARM7TDMI的1.8~2.2倍。 (二) 指令周期的改進: 指令周期的改進對於處理器性能的提高有很大的幫助。性能提高的...

ARM9TDMI ARMv4T ARM9TDMI 五級流水線 無 ARM920T 16KB/16KB, MMU 200 MIPS @ 180 MHz Armadillo,GP32,GP2X(第一顆核心), Tapwave Zodiac(Motorolai...

ARM開發板ARM核心特點 英國ARM公司是嵌入式RISC處理器的IP(智慧財產權)供應商,它為ARM架構處理器提供ARM處理器核心(如ARM7TDMI、ARM9TDMI及ARM10TDMI等)。由各...

ARM7系列處理器是英國ARM公司設計的主流嵌入式處理器 ARM7核心是0.9MIPS/MHz的三級流水線和馮·諾伊曼結構; ARM9核心是5級流水線,提供1.1MIPS/MHz的哈佛結構。...

D.1指令周期定時表的使用D.2 ARM7TDMI指令周期定時D.3 ARM9TDMI指令周期定時D.4 StrongARM1 指令周期定時D.5 ARM9E指令周期定時D.6 ARM10E指令周期定時...

9.2ARM82179.3ARM9TDMI2209.4ARM10TDMI2239.5討論2269.6例題與練習227 第10章 存儲器層次10.1存儲器容量及速度22810.2片上存儲器229...

2.2.1 arm處理器結構特點 122.2.2 arm的版本 13.2.2.3 arm結構的變體 142.2.4 常見arm型號簡介 152.2.5 arm9tdmi核心 17...

介紹的ARM產品包括ARM7TDMI、ARM9TDMI、ARM10TDMI 、710T、720T、740T、920T、940T、1020E和Strong、ARM還給出異步ARM核心AMULET的一件系統設計原理以及軟體問題...

ARM開發板是以ARM核心晶片的嵌入式開發版,包括ARM7,ARM9,ARM11,Cortex-M,...ARM9TDMI Armadillo,GP32,GP2X(第一顆核心), Tapwave Zodiac(Motorolai. MX1...

課程安排由以下部分組成,嵌入式系統綜述、嵌入式系統設計開發過程、基於ARM的嵌入...2.2ARM9處理器2.2.1與ARM7處理器的比較2.2.2ARM9TDMI核心...

5.3 ARM處理器核心5.3.1 ARM7TDMI處理器核心5.3.2 ARM9TDMI處理器核心5.3.3 ARM10TDMI處理器核心5.4 ARM處理器核5.4.1 ARM720T/ARM740T處理器核5.4....